声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

二进制

+关注

关注

2文章

809浏览量

42799 -

计算机

+关注

关注

19文章

7764浏览量

92682 -

乘法器

+关注

关注

9文章

221浏览量

38526

发布评论请先 登录

相关推荐

热点推荐

模拟乘法器AD834的原理与应用

模拟乘法器AD834的原理与应用:AD834是美国ADI公司推出的宽频宽、四象限、高性能的模拟乘法器。它工作稳定,计算误差小,并具有低失真和微功耗的特点,本文介绍了AD834模拟乘法器

发表于 09-29 10:49

•188次下载

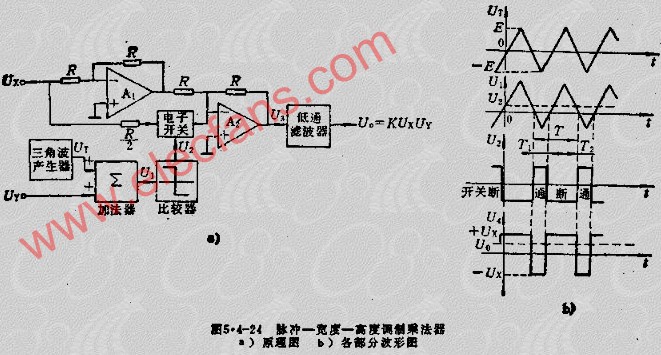

脉冲-宽度-高度调制乘法器

脉冲-宽度-高度调制乘法器

脉冲-宽度-高度调制乘法器双称为时间分割乘法器。这类乘法器电路原理图如图5.4-24A所示。图中,三角波电压UT和模拟

发表于 05-18 14:23

•2332次阅读

基于IP核的乘法器设计

实验目的 1、熟悉Xilinx的ISE 软件的使用和设计流程; 2、掌握Modelsim仿真软件的使用方法; 3、用乘法运算符实现一个16*16 乘

发表于 05-20 17:00

•68次下载

使用verilogHDL实现乘法器

本文在设计实现乘法器时,采用了4-2和5-2混合压缩器对部分积进行压缩,减少了乘法器的延时和资源占 用率;经XilinxISE和QuartusII两种集成开发环境下的综合仿真测试,与用

发表于 12-19 13:30

•1.1w次阅读

乘法器原理_乘法器的作用

乘法器(multiplier)是一种完成两个互不相关的模拟信号相乘作用的电子器件。它可以将两个二进制数相乘,它是由更基本的加法器组成的。

发表于 02-18 15:08

•2.8w次阅读

模拟乘法器输出与输入的关系式

模拟乘法器是输出电压与两路输入电压之积成正比的有源网络。理想的乘法器具有无限大的输入阻抗及零输出阻抗,其标尺因子不随频率变化并且与电压的大小无关。如果理想的

发表于 02-18 17:21

•7369次阅读

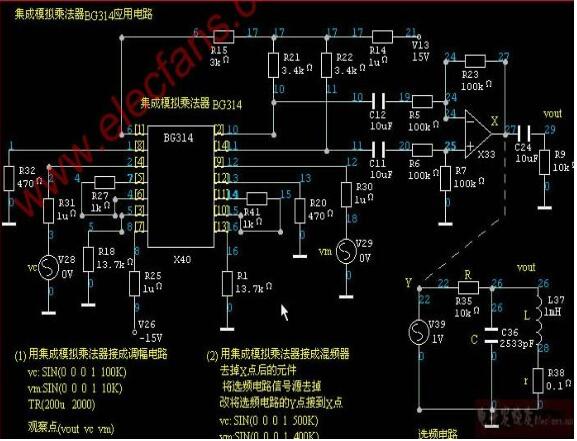

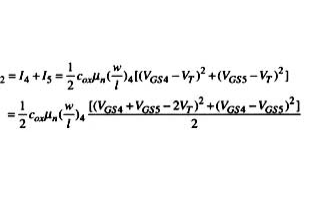

采用Gillbert单元如何实现CMOS模拟乘法器的应用设计

在集成电路系统中,模拟乘法器在信号调制解调、鉴相、频率转换、自动增益控制和功率因数校正控制等许多方面有着非常广泛的应用。实现模拟乘法器的方法有很多,按采用的工艺不同,可以分为三极管乘法器

如何实现一个四输入乘法器的设计

如何实现一个四输入乘法器的设计

评论