乘法器是模拟式电子式电能表的重要组成部分,也是电能表计量误差的最主要来源。对时分割乘法器在谐波条件下的计量误差进行了定量的研究与分析,根据时分割乘法器的工作原理,推导其在谐波条件下计量误差的理论表达式,并通过仿真计算验证计量误差量化表达式的准确性。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

仿真

+关注

关注

53文章

4406浏览量

137671 -

电能表

+关注

关注

5文章

877浏览量

35651 -

乘法器

+关注

关注

9文章

221浏览量

38526

发布评论请先 登录

相关推荐

热点推荐

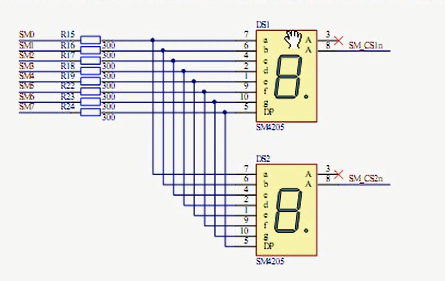

FPGA视频教程之使用BJ-EPM240学习板进行数码管显示实验的资料说明

本文档的主要内容详细介绍的是FPGA视频教程之使用BJ-EPM240学习板进行数码管显示实验的资料说明

发表于 02-28 10:35

•5次下载

FPGA视频教程之BJ-EPM240学习板的详细资料介绍

本文档的主要内容详细介绍的是FPGA视频教程之BJ-EPM240学习板的详细资料说明免费下载,BJ-EPM240学习

发表于 03-01 11:35

•21次下载

FPGA视频教程之BJ-EPM240学习板乘法器设计实验的详细资料说明

乘法器是众多数字系统中的基本模块。从原理上说它属于组合逻辑范畴:但从工程实际设计上来说,它往往会利用时序逻辑设计的方法来实现,属于时序逻辑的范畴。

发表于 03-04 17:06

•1次下载

BJ-EPM240学习板介绍

主芯片使用的是Altera公司的MAXII系列EPM240T100C5,该芯片有240个逻辑单元,等效宏单元192个,资源比较丰富,内有8KbitFlash的存储空间。

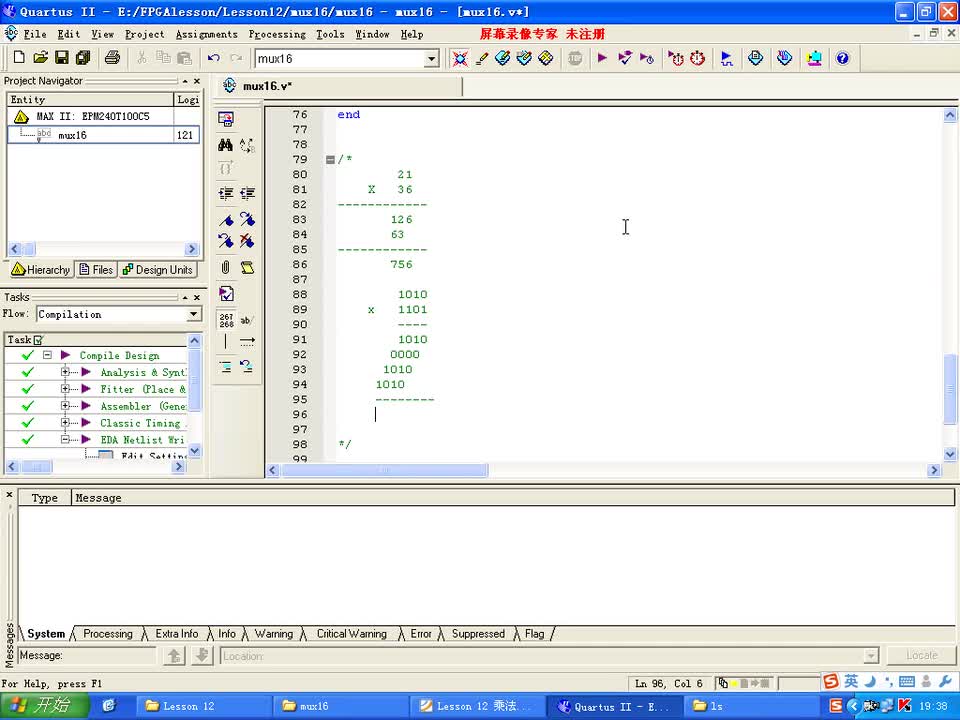

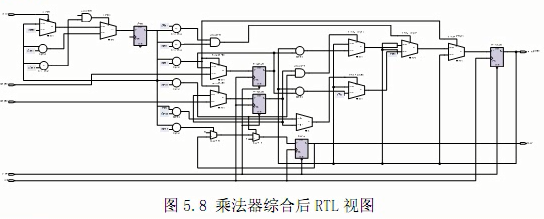

BJ-EPM240学习板之乘法器设计实验

乘法器是众多数字系统中的基本模块。从原理上说它属于组合逻辑范畴:但从工程实际设计上来说,它往往会利用时序逻辑设计的方法来实现,属于时序逻辑的范畴。

FPGA视频教程:BJ-EPM240学习板-乘法器设计实验

乘法器可以通过使用一系列计算机算数技术来实现。乘法器不仅作为乘法、除法、乘方和开方等模拟运算的主要基本单元,而且还广泛用于电子通信系统作为调制、解调、混频、鉴相和自动增益控制;另外还可用于滤波、波形形成和频率控制等场合,因此是一

乘法器原理_乘法器的作用

乘法器(multiplier)是一种完成两个互不相关的模拟信号相乘作用的电子器件。它可以将两个二进制数相乘,它是由更基本的加法器组成的。乘法器可以通过使用一系列计算机算数技术来实现。乘法器

发表于 02-18 15:08

•2.8w次阅读

BJ-EPM240学习板:乘法器设计实验

BJ-EPM240学习板:乘法器设计实验

评论