引言

在集成电路系统中,模拟乘法器在信号调制解调、鉴相、频率转换、自动增益控制和功率因数校正控制等许多方面有着非常广泛的应用。实现模拟乘法器的方法有很多,按采用的工艺不同,可以分为三极管乘法器和CMOS乘法器。

CMOS模拟乘法器的工作原理有三种:基于MOS管在饱和区工作时的平方法则,这种模拟乘法器性能好,但结构复杂;基于MOS管在线性区工作时的电流电压法则,这种模拟乘法器比较适宜低压运用;采用Gillbert单元实现的模拟乘法器。本文详细分析了采用Gillbert单元实现的模拟乘法器的原理,对其进行了改进,使它能拥有更低的工作电压和更大的输入范围。

基本电路原理

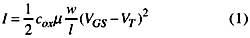

简单的Gillbert单元CMOS模拟乘法器如图1所示,图中M1管给乘法器提供偏置电流ISS。忽略MOS管的沟道长度调制效应,工作在饱和区的MOS管电流都可以写成:

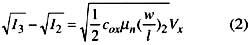

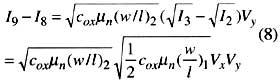

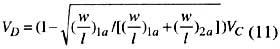

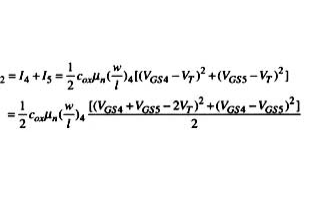

若M2、M3的宽长比相同,设为(w/1)2,由Vx=VGS3-VGS2可得:

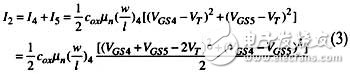

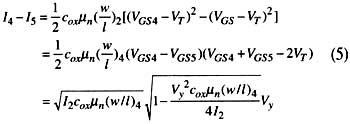

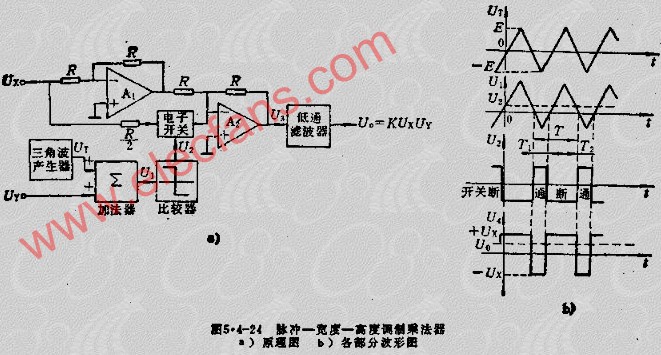

若M4、M5、M6、M7这四个管子的宽长比相同,设为(w/1)4,则可以得到:

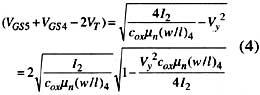

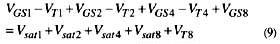

由VGS4-VCS5=Vy得:

从而有:

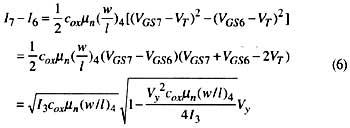

同理可得:

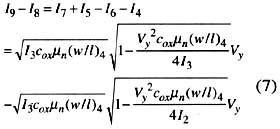

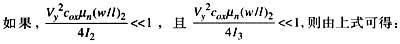

所以:

如此就实现了乘法功能。

如果要使图1中的乘法器正常工作,那么至少要保证所有的管子都处在饱和工作区,因此电源电压至少需要:

式中在电源的饱和压降。如果要实现两个大电电压较低的情况下,电路不能正常工作,因此需要对它进行改进,降低乘法器的工作电压。

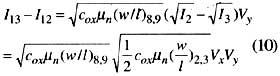

如图2所示,将输入电压Vx产生的电流通过M4、M5镜像到M6、M7管。把M2、M3的宽长比设成相等,用(w/1)2,3来表示;把M8、M9、M10、M11的宽长比设成相等,用(w/1)8,9来表示;把M4、M5、M6、M7的宽长比设成相等。可得:

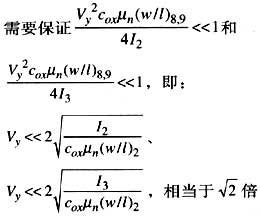

与图1中的电路相比,图2的模拟乘法器工作所需要的电源电压比图1少一个饱和压降,所以能在更低的电源电压下工作。与图1相似,如果图2的电路要正常工作,那么

的饱和压降。如果要实现两个大电压信号的相乘,该输入范围是远远不够的。因此,本文在乘法器的输入端加入了一个有源衰减电路,以增大电路的输入范围。

NMOS有源衰减电路如图3(a)所示,它提供Vx的输入;PMOS有源衰减电路如图3(b)所示,提供Vy的输入。两个电路的原理相同,以图3(a)中的NMOS电路为例,设A点输入电压VA,M2处在饱和区,VB

M5、M6作为电平位移电路,为乘法器的输入端提供电压偏置。由(11)式可得:

通过调整M1、M2的宽长比可以调节Vout与Vin的比值,改变它的输入范围。

仿真结果

基于上华0.6μm CMOS工艺,电路采用Cadence Spectre仿真器进行了仿真模拟。乘法器使用3V电源电压时,仿真结果显示,当输入电压在0~2V之间变化时,输出基本上与输入成线性变化。也就是说,采用3V电源电压时,乘法器的两个输入电压能够达到2V而不产生明显线性失真。这验证了本文设计的正确性。

结语

本文分析了CMOS工艺下的Gillbert单元乘法器,对这种乘法器做了改进,降低了乘法器工作所需要的电源电压,扩大了乘法器的输入范围。

-

CMOS

+关注

关注

58文章

6186浏览量

241581 -

三极管

+关注

关注

145文章

3678浏览量

126733 -

仿真器

+关注

关注

14文章

1048浏览量

86760

发布评论请先 登录

结构简单的高线性CMOS四象限模拟乘法器设计

怎么设计基于FPGA的WALLACETREE乘法器?

数字阵列乘法器的算法及结构分析

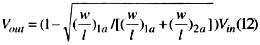

脉冲-宽度-高度调制乘法器

基于FPGA的WALLACE TREE乘法器设计

使用verilogHDL实现乘法器

乘法器原理_乘法器的作用

采用Gillbert单元如何实现CMOS模拟乘法器的应用设计

基于CMOS工艺下的Gillbert单元乘法器的研究

基于CMOS工艺下的Gillbert单元乘法器的研究

评论