完善资料让更多小伙伴认识你,还能领取20积分哦,立即完善>

标签 > fpga

FPGA(Field-Programmable Gate Array),即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

文章:12841个 浏览:630747次 帖子:7998个

【ZYNQ Ultrascale+ MPSOC FPGA教程】第十章PWM呼吸灯实验

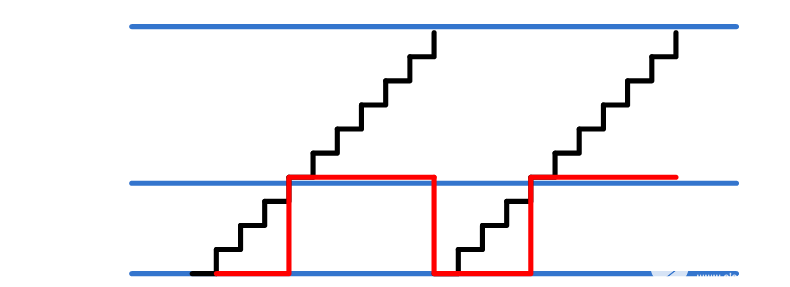

用一个N比特的计数器,最大值可以表示为2的N次方,最小值0,计数器以“period”为步进值累加,加到最大值后会溢出,进入下一个累加周期。当计数器值大于...

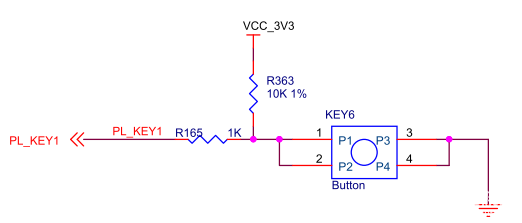

【ZYNQ Ultrascale+ MPSOC FPGA教程】第九章Vivado下按键实验

按键是FPGA设计当中最常用也是最简单的外设,本章通过按键检测实验,检测开发板的按键功能是否正常,并了解硬件描述语言和FPGA的具体关系,学习Vivad...

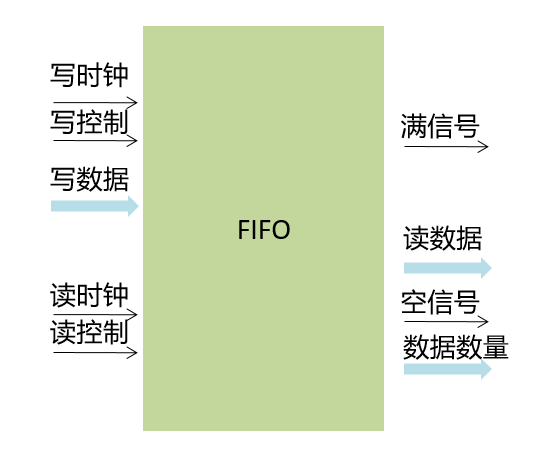

【ZYNQ Ultrascale+ MPSOC FPGA教程】第八章FPGA片内FIFO读写测试实验

FIFO: First in, First out代表先进的数据先出,后进的数据后出。Xilinx在VIVADO里为我们已经提供了FIFO的IP核, 我...

【ZYNQ Ultrascale+ MPSOC FPGA教程】第七章FPGA片内ROM测试实验

既然是ROM,那么我们就必须提前给它准备好数据,然后在FPGA实际运行时,我们直接读取这些ROM中预存储好的数据就行。Xilinx FPGA的片内ROM...

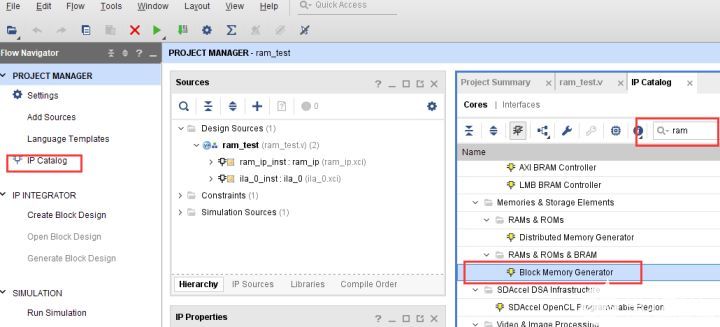

【ZYNQ Ultrascale+ MPSOC FPGA教程】第六章FPGA片内RAM读写测试实验

RAM是FPGA中常用的基础模块,可广泛用于缓存数据的情况,同样它也是ROM,FIFO的基础。本实验将为大家介绍如何使用FPGA内部的RAM以及程序对该...

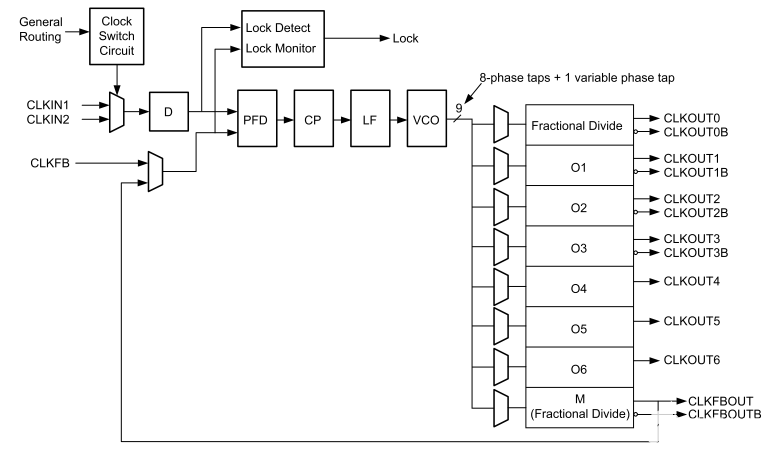

【ZYNQ Ultrascale+ MPSOC FPGA教程】第五章Vivado下PLL实验

PLL(phase-locked loop),即锁相环。是FPGA中的重要资源。由于一个复杂的FPGA系统往往需要多个不同频率,相位的时钟信号。所以,一...

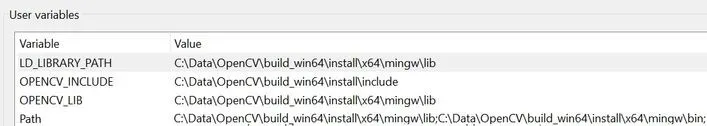

Vitis HLS工具在Standalone模式下调用Xilinx Vision Library L1 API例程

在论坛上遇到在高层次综合工具中调用视觉库遇到的大多数问题都和 opencv 库以及Xilinx Vision 库的安装路径有关,如今 Vitis HLS...

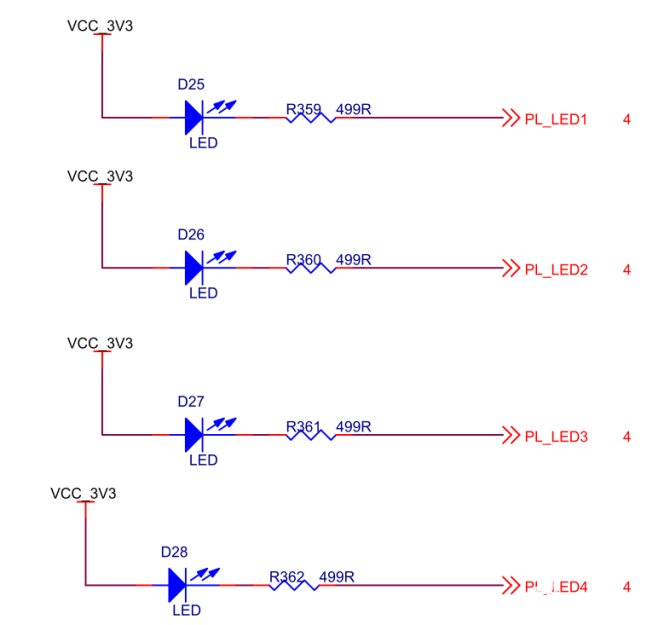

【ZYNQ Ultrascale+ MPSOC FPGA教程】第四章PL的LED实验

对于ZYNQ来说PL(FPGA)开发是至关重要的,这也是ZYNQ比其他ARM的有优势的地方,可以定制化很多ARM端的外设,在定制ARM端的外设之前先让我...

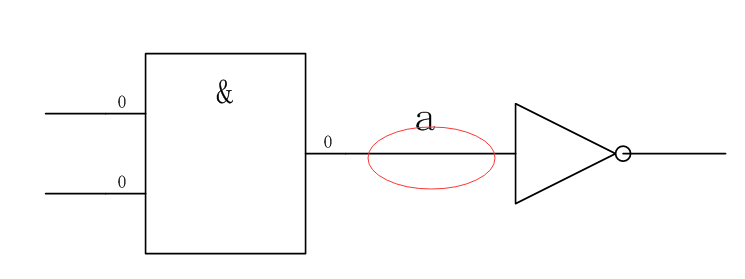

【ZYNQ Ultrascale+ MPSOC FPGA教程】第三章Verilog基础模块介绍

Wire 类型变量,也叫网络类型变量,用于结构实体之间的物理连接,如门与门之间,不能储存值,用连续赋值语句assign赋值,定义为wire [n-1:0...

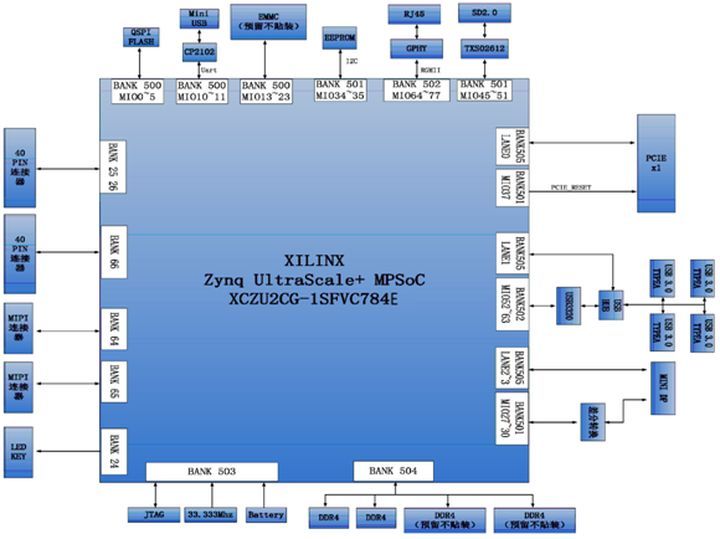

【ZYNQ Ultrascale+ MPSOC FPGA教程】第二章硬件原理图介绍

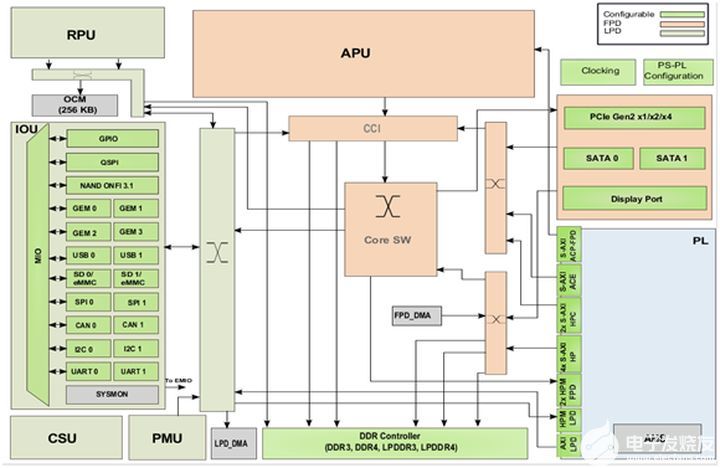

XCZU2CG-1SFVC784E芯片的PS系统PS系统集成了2个ARMCortex™-A53处理器,速度高达1.2Ghz,支持2级Cache;另外还包...

【ZYNQ Ultrascale+ MPSOC FPGA教程】第一章MPSoC芯片介绍

原创声明: 本原创教程由芯驿电子科技(上海)有限公司(ALINX)创作,版权归本公司所有,如需转载,需授权并注明出处。 适用于板卡型号: AXU2CGA...

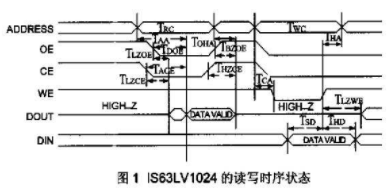

基于Virtex-E系列XCV300E与高速静态存储设备的接口实现

为了能更好﹑更有效的设计FPGA与IS63LV1024的接口实现,必须先了解IS63LV1024的性能特点。充分利用这些特点会使设计的实现变得事半功倍。...

基于EP1C3T144C6芯片和VHDL语言实现语音电子密码锁的设计

随着电子技术的发展,具有防盗报警、语音提示等功能的电子密码锁代替密码量少、安全性差的机械式密码锁已是必然趋势。目前大部分密码锁采用单片机进行设计,电路较...

低功耗设计的实现是我们关注的焦点,现代企业越来越注重低功耗。因为,低功耗往往能为器件带来更好的性能。在前文中,小编对FPGA低功耗设计有所阐述。为增进大...

功耗是我们关注的设计焦点之一,优秀的器件设计往往具备低功耗特点。在前两篇文章中,小编对基于Freez技术的低功耗设计以及FPGA低功耗设计有所介绍。为增...

基于XC2V500-6FG256C和AD9858实现复杂信号模拟的设计

在1992年5月美国电信系统会议上,JeoMitola首次提出了软件无线电概念,之后迅速引起了人们的关注,并开始对它进行广泛而深入的研究。具体地说,软件...

基于Nios Ⅱ软核处理器和FPGA实现人脸检测跟踪系统的设计

人脸检测跟踪是计算机视觉中十分重要的研究领域,正受到越来越多的关注。传统基于PC平台的人脸检测跟踪系统体积大,不能满足便携的要求,更不适合露天使用;而采...

编辑推荐厂商产品技术软件/工具OS/语言教程专题

| 电机控制 | DSP | 氮化镓 | 功率放大器 | ChatGPT | 自动驾驶 | TI | 瑞萨电子 |

| BLDC | PLC | 碳化硅 | 二极管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 无刷电机 | FOC | IGBT | 逆变器 | 文心一言 | 5G | 英飞凌 | 罗姆 |

| 直流电机 | PID | MOSFET | 传感器 | 人工智能 | 物联网 | NXP | 赛灵思 |

| 步进电机 | SPWM | 充电桩 | IPM | 机器视觉 | 无人机 | 三菱电机 | ST |

| 伺服电机 | SVPWM | 光伏发电 | UPS | AR | 智能电网 | 国民技术 | Microchip |

| 开关电源 | 步进电机 | 无线充电 | LabVIEW | EMC | PLC | OLED | 单片机 |

| 5G | m2m | DSP | MCU | ASIC | CPU | ROM | DRAM |

| NB-IoT | LoRa | Zigbee | NFC | 蓝牙 | RFID | Wi-Fi | SIGFOX |

| Type-C | USB | 以太网 | 仿真器 | RISC | RAM | 寄存器 | GPU |

| 语音识别 | 万用表 | CPLD | 耦合 | 电路仿真 | 电容滤波 | 保护电路 | 看门狗 |

| CAN | CSI | DSI | DVI | Ethernet | HDMI | I2C | RS-485 |

| SDI | nas | DMA | HomeKit | 阈值电压 | UART | 机器学习 | TensorFlow |

| Arduino | BeagleBone | 树莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 华秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |