1 引言

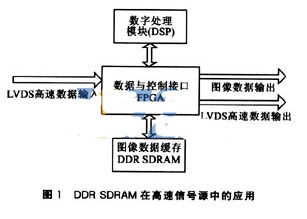

在高速信号处理系统中, 需要缓存高速、大量的数据, 存储器的选择与应用已成为系统实现的关键所在。DDR SDRAM是一种高速CMOS、动态随机访问存储器, 它采用双倍数据速率结构来完成高速操作。SDR SDRAM一个时钟周期只能传输一个数据位宽的数据, 因此在相同的数据总线宽度和工作频率下, DDR SDRAM的总线带宽比SDR SDRAM的总线带宽提高了一倍。

Xilinx VirtexTM- 4 FPGA 具备ChipSync 源同步技术等优势。它的输入输出模块( IOB) 提供了封装引脚与内部可配置逻辑之间的接口, 无论是输入路径还是输出路径都提供了一个可选的SDR 和DDR 寄存器。VirtexTM- 4 的IOB 专门针对源同步设计进行了优化, 包括每一位的偏移校正、数据的串行化和解串行化、时钟分频以及专用的本地时钟资源等, 而且它在每一个I/O 模块中都提供了64- 阶延迟线。这些特性使得VirtexTM- 4 FPGA 能够更好的实现DDR SDRAM控制器的逻辑设计, 准确可靠的捕获数据。

实验板选择专为DSP 应用而优化的Virtex- 4 SX35 作为DDR SDRAM控制器的实现平台, 选用Micron MT46V8M16P-75Z DDR SDRAM。

2 DDR SDRAM 控制器工作原理

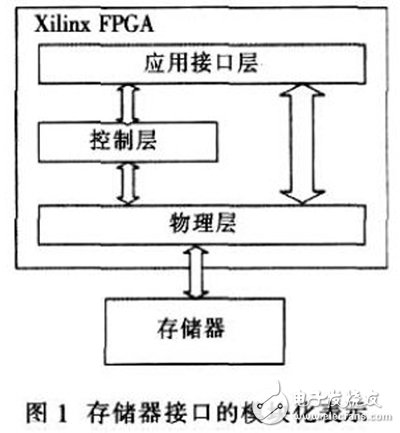

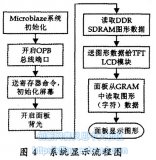

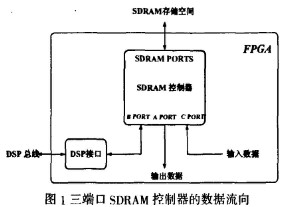

DDR SDRAM控制器的主要功能就是完成对DDR SDRAM的初始化, 将DDR SDRAM复杂的读写时序转化为用户简单的

读写时序, 以及将DDR SDRAM接口的双时钟沿数据转换为用户的单时钟沿数据, 使用户像操作普通的RAM一样控制DDR SDRAM; 同时, 控制器还要产生周期性的刷新命令来维持DDR SDRAM内的数据而不需要用户的干预。该控制器的模块化表示如图1。

应用层接口是DDR 控制器与FPGA 用户设计的接口。对于DDR 控制器的用户来说, 只需要了解如何使用应用层接口, 通

过应用层接口给DDR 控制器发出指令、数据, 并且接收数据。这种模块化设计增加了DDR 控制器的可移植性, 也使用户使用起来更简单。

要功能是:完成存储器的初始化, 接收并解码用户指令然后产生读、写、刷新等指令。控制层的逻辑设计主要是由一个状态机管理的。物理层是直接与DDR SDRAM通信的平台, 它的主要功能是:捕获DDR SDRAM发出的数据、以及通过输入输出缓存发送所有DDR SDRAM的控制信号、地址信号以及数据信号。

2.1 控制层工作原理

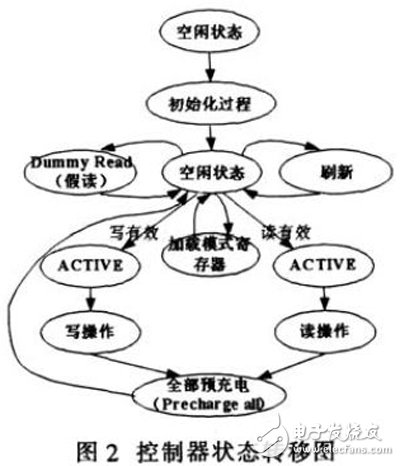

控制层主要由一个状态机来控制DDR SDRAM控制器的状态转移。状态机如图2 所示。

DDR SDRAM上电后必须按照规定的程序完成初始化的过程。在初始化过程中一定要注意普通模式寄存器与扩展模式寄

存器的值是否正确。普通模式寄存器用来设定DDR SDRAM的工作方式, 包括突发长度、突发类型、CAS 潜伏期和工作模式;扩展模式寄存器主要实现对DDR SDRAM内部DLL 的使能和输出驱动能力的设置。在本实验板中选择的是Micron

MT46V8M16P- 75Z 型号的DDR SDRAM, 该型号芯片CAS 潜伏期只能为2 或者2.5。

初始化完成之后, DDR SDRAM进入正常的工作状态, 此时可对存储器进行读写和刷新操作。在本设计中为了计算读数据

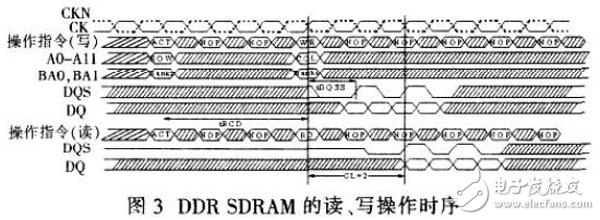

延迟量引入了一个假读操作(Dummy Read) , 这将在下一节中详细分析。DDR SDRAM在一对差分时钟的控制下工作。命令在每个时钟的上升沿触发。随着数据一起传送的还包括一个双向的数据选通信号DQS, 接收方通过该信号来接收数据。该选通信号与数据相关, 其作用类似于一个独立的时钟。DQS 作为选通信号在读周期中由DDR SDRAM来产生。读周期中, DQS 与数据是边沿对齐的。读操作时, DDR 控制器采用直接时钟获取的方式捕获数据。读命令触发后, 数据将在CAS 延迟之后出现在数据总线上。DQS 在写周期中是由DDR 控制器产生的。写周期中, DQS 与数据是中心对齐的。读写操作时序如图3(DQ 指传输的数据) 。

在进行读写操作之前需要先执行ACTIVE 命令( 激活命令) , 与激活命令一起被触发的地址用来选择将要存取的区( bank) 和页( 或行) 。与读或写命令一起触发的地址位用来选择突发存取的起始列单元。在激活指令之前还有一个预充电

( PRECHARGE) 操作, 预充电操作关闭之前进行操作的存储区或行, 此操作之后DDR SDRAM才能对新的区或者行进行读写操作。

DDR SDRAM需要用自动刷新(AUTO REFRESH) 命令来周期性的刷新DDR SDRAM, 以保持其内部的数据不丢失。自动刷新必须在所有区都空闲的状态下才能执行。128Mb 的DDR SDRAM执行自动刷新的周期最大为15.625μs。

写操作是由FPGA 向DDR SDRAM写入数据, 只需按照DDR SDRAM的工作要求发出相应的指令即可, 逻辑设计相对简单, 因此下面我们将详细介绍读操作中的数据捕获技术。

2.2 物理层数据捕获技术及数据通道电路

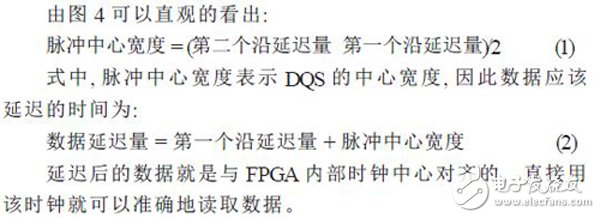

物理层的主要功能是获得DDR SDRAM发出的数据、以及通过输入输出缓存发送所有DDR SDRAM的控制信号、地址信号以及数据信号。数据捕获技术及数据通道电路是DDR SDRAM控制器的技术核心。DDR SDRAM接口是源同步接口,

即数据与传输时钟是边沿对齐的。因此, 为了在FPGA 中可靠捕获数据要么延迟时钟要么延迟数据, 使数据与时钟中心对齐。本设计采取直接时钟数据捕获技术。

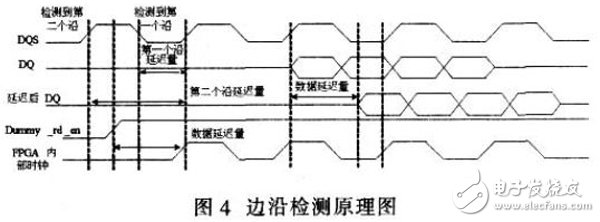

所谓直接时钟数据捕获技术就是利用DQS 信号计算数据延迟量, 通过延迟数据使数据中心与FPGA 内部时钟沿对齐, 然

后用该内部时钟直接读取数据。DQS 是由DDR 发出的数据选通信号, 它与FPGA 内部时钟频率相同。此项技术的关键是确定数据的延迟时间。相对于其他的数据捕获技术, 这种直接时钟数据捕获技术可以应用于更高的时钟频率, 精确性和稳定性都高于其他方法。

为了得到数据应该延迟的时间量, 首先要对DQS 进行边沿检测。控制器发出Dummy_rd_en 信号( 即假读信号) 使DDR

SDRAM 发出DQS 信号, 当延迟量计算完毕时, 置Dummy_rd_en 为低。

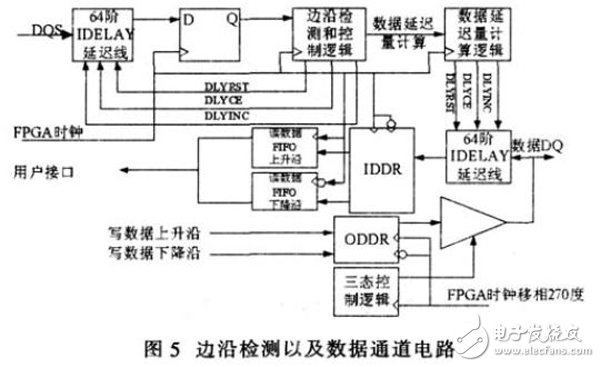

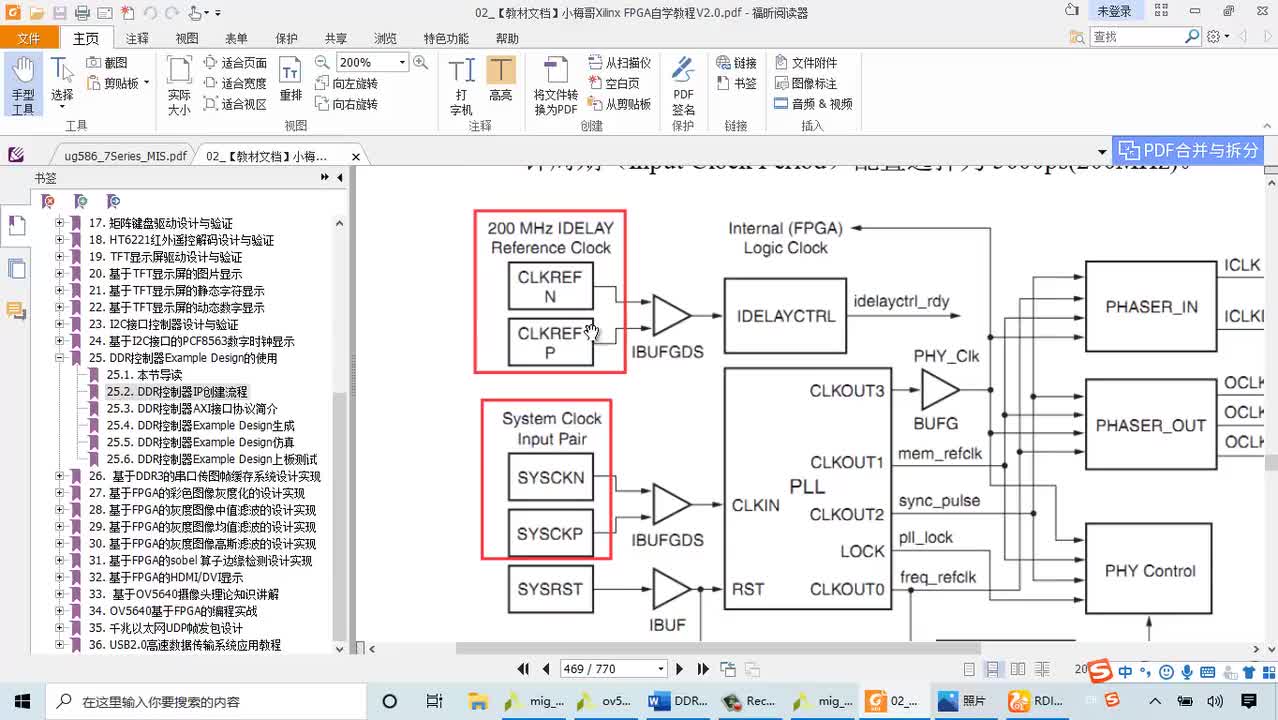

在Xilinx VirtexTM- 4 FPGA 中实现该延迟检测电路是非常容易的, 因为设计可以直接利用FPGA 内部的IDELAY 与IDELAY_CTRL 电路。图5 表示了边沿检测以及数据通道电路。

在该电路中, DQS 输入到IDELAY 模块, 延迟量初始化为0, 然后延迟量逐次递增, 在这个过程中不断检测延迟后的DQS 的跳变沿, 并将延迟量TAP 值记录下来, 以便计算数据DQ 的延迟量。在图中可看出, 边沿检测和控制逻辑发出DLYRST、DLYCE 和DLYINC 三个信号来控制IDELAY 延迟模块的工作模式。

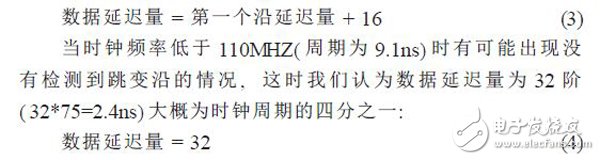

由于IDELAY 模块的最大延迟阶数为64, 且在Xilinx VirtexTM-4 FPGA 中, 延迟模块的精度TIDELAYRESOLUTION 为75ps, 所以延迟时间最大为75ps*64=4.8ns, 因此当时钟频率低于200MHZ( 周期为5ns) 时, 不可能检测到两个跳变沿, 此时必须采取适当的措施来获得数据延迟量。当64 阶延迟量完成时只检测到一个跳变沿时, 我们认为数据延迟量为检测到第一个跳变沿时的延迟量加上16, 因为四分之一个200MHZ 时钟周期大约为16阶延迟量( 16*75=1.2ns) 即:

延迟后的数据经过IDDR 触发器分别得到上升沿对应的数据和下降沿对应的数据, 然后再通过异步查找表FIFO 使读进

FPGA 的数据与FPGA 内部时钟同步方便用户使用。

3 控制器实验结果及结论

该DDR 控制器设计总共占用751 个4 输入LUT, 占总LUT 资源的2%。另外, 设计还使用了3 个DCM。DDR 控制器在

Xilinx ISE8.1i 编程环境下实现, 结合ModelSim SE6.1b 进行仿真。板上调试时时钟选为100MHZ, 经测试数据传输及捕获准确无误。

经实验验证该DDR 控制器工作稳定可靠、确实可行, 占用逻辑资源较少, 且具有较高的可移植性, 以及简单方便的用户接

口。该DDR 控制器经过简单的修改就可以控制其他型号的DDR SDRAM芯片, 因此可以极大地提高信号处理板的存储容

量, 很好的用于高速信号处理系统中。

电子发烧友App

电子发烧友App

评论