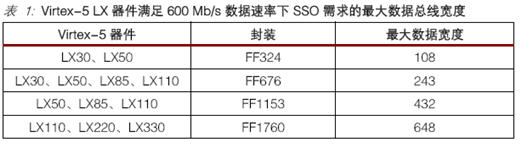

本白皮书讨论各种存储器接口控制器设计所面临的挑战和 Xilinx 的解决方案,同时也说明如何使用 Xilinx软件工具和经过硬件验证的参考设计来为您自己的应用(从低成本的 DDR SD

2010-08-18 10:50:37 3238

3238

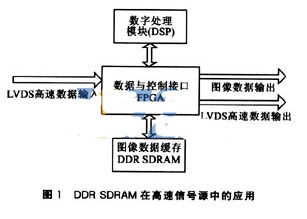

用户端使用的,框图如图1所示。 如图1 所示的中间部分为我们调取的IP 核,user FPGA Logic 为用户端逻辑,DDR2/DDR3 SDRAM 为存储芯片。其中IP 核与存储芯片之间的总线大部分

2020-12-31 11:17:02 5068

5068

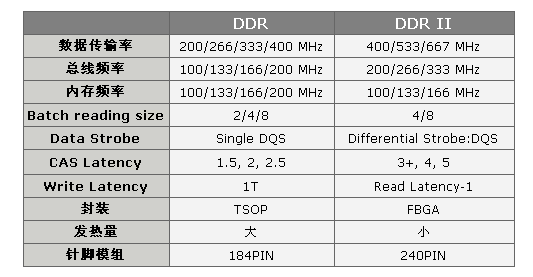

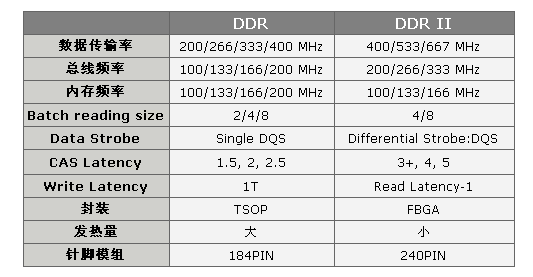

DDR内存1代已经淡出市场,直接学习DDR3 SDRAM感觉有点跳跃;如下是DDR1、DDR2以及DDR3之间的对比。

2023-04-04 17:08:47 2871

2871

本贴资料整理于《例说FPGA 可直接用于工程项目的第一手经验》1.1功能概述:对FPGA提供的DDR2控制器IP核模块进行读写操作。每1.78秒执行一次写入和读出操作。先从0地址开始遍历写256

2017-02-15 20:31:49

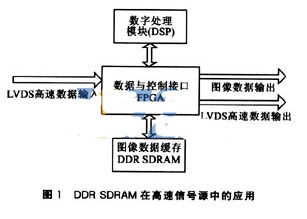

DDRSDRAM接口的双时钟沿数据转换为用户方的单时钟沿数据,使用户像操作普通的RAM一样控制DDR SDRAM;同时,控制器还要产生周期性的刷新命令来维持DDRSDRAM内的数据而不需要用户的干预

2018-12-18 10:17:15

使用LatticeECP3 I/O协议板来实现并通过全部测试。图2展示了一个存储器控制器的框图。图最上面的配置接口用于设置设计的各个选项。DDR3 I/O模块使用I/O 基元来实现。指令译码模块根据每个bank

2019-05-24 05:00:34

DDR3存储器接口控制器是什么?有什么优势?

2021-04-30 06:57:16

DDR4,DDR3,DDR2,DDR1及SDRAM有什么不同之处?

2021-03-12 06:22:08

SDRAM控制器用户手册主要内容包括功能特点、整体框图、工作原理、信号定义、参数介绍、GUI 调用、接口时序等。主要用于帮助用户快速了解高云半导体 SDRAM 控制器的产品特性、特点及使用方法。

2022-10-08 07:48:27

有人用Xilinx ISE的mig生成ddr2,然后进行调试的吗?如果选择了内含pll,顶层时钟怎么连接

2014-09-15 19:14:41

求一DDR2接口设计代码

2013-04-24 10:00:36

在DDR2 MIG的使用时,想把DDR2封装成一个FIFO使用,但是有些问题不是太明白。在MIG的User Interface接口中,提供给控制器的数据是上升沿和下降沿的拼接,一个周期提供两个数据到

2015-03-29 18:41:43

本帖最后由 dybttkl 于 2015-11-1 13:26 编辑

用的cycloneiii 里面的ddr2 ip核。感觉网上的资料很少,仿真的倒很多,但是真正到用户接口那段时序的解释却一个也没有。为何没人写个教程

2015-11-01 13:24:54

最近在做ddr2方面的东西,需要仿真ddr2,可是一直没有头绪。xx_example_top_tb仿真不知道是对是错,网上说的外挂美光ddr2 模型的仿真方法,没有具体讲解。哪位大虾能够指点一二哇,不甚感激!

2016-06-29 15:50:28

CoreLink DDR2动态存储器控制器(DMC-341)技术参考手册

2023-08-02 15:28:28

® ALTMEMPHY宏功能来构建所有的 DDR2或者 DDR SDRAM外部存储器。通过将 Altera DDR2 或者 DDR SDRAM 存储控制器、第三方控制器或者定制控制器用于特定的应用需要,可以实现控制器功能

2017-11-14 10:12:11

本项目使用的是cycloneIII的芯片,利用IP核生成了一个DDR2的控制器,但是再分配引脚的时候产生了如下问题,如Error: The assigned location PIN U21

2012-06-19 10:26:30

。Gowin DDR2 Memory Interface IP 参考设计可在高云官网下载,参考设计已配置一例特定参数,可用于仿真,实例化加插用户设计后的总综合,总布局布线

2022-10-08 07:25:25

IBIS Models for DDR2 Analysis 仿真

2012-03-16 16:52:07

实现特权同学的例程 特权FPGA VIP视频图像开发套件例程详解2——DDR2控制器读写测试 时,进行IP核配置时,进入下一步配置参数时,变成黑屏重装软件也不行

2018-01-24 08:23:17

PL341内存控制器是一款高性能、面积优化的DDR2 SDRAM内存控制器,兼容高级微控制器总线架构(AMBA)AXI协议。

有关AXI协议的详细说明,请参阅AMBA AXI协议规范。

本节总结了周期模型的功能与硬件的功能,以及周期模型的性能和准确性。

2023-08-12 06:01:49

存储器控制器用户指南列出了数据,地址,控制和时钟信号的长度匹配要求。给出的数字是否必须补偿FPGA和DDR2封装内的键合线长度?如果是这样,我在哪里可以找到这些长度?谢谢,TL以上来自于谷歌翻译以下

2019-03-15 10:06:16

,是ddr2控制器导出给用户的接口信号,用户要向ddr2存储器中写入数据或者从ddr2中读出数据,只需要操作local接口即可。local信号,可以分为以下几组:控制组local_init_done

2020-02-25 18:33:00

嗨,我使用MIG 2.1构建了两个DDR2 SDRAM控制器来进行Ping Pong缓冲。该设备是virtex4FX60FF1152和ISEver是10.1。当它在设备上运行时,控制器

2020-06-02 16:58:51

所需的物理接口。● DDR2的自动校正是在初始化阶段进行的,此时ALTMEMPHY断开用户逻辑和存储控制器之间的接口,ALTMEMPHY产生存储控制器所需的DDR2读写控制,直到校正完成。在初始化过后

2016-10-27 16:36:58

最近在设计一个需要连接DDR2 SDRAM的FPGA小系统,由于是第一次在使用SDRAM,在硬件连接时就遇到一个很纠结的问题——引脚的连接。看了几种参考设计,发现有两种说法:1、DDR2的数据(DQ

2017-09-25 17:51:50

这是我自己写ddr2控制器的写操作,但为什么写的地址不按顺序写,有谁做过吗?

2017-03-20 16:36:20

基于Xilinx FPGA的DDR2 SDRAM存储器接口

2012-08-20 18:55:15

Cyclone III系列型号为EP3C16F484C6N的FPGA作为控制器,以Micron公司生产的型号为MT47H16M16BG-5E(16M×16bit)的DDR2 SDRAM为存储器。用一个IP核完成

2011-05-03 11:31:09

进行了DDR3 SDRAM控制器的编写,分析并提出了提高带宽利用率的方法。最终将其进行类FIFO接口的封装,屏蔽掉了DDR3 IP核复杂的用户接口,为DDR3数据流缓存的实现提供便利。系统测试表明,该

2018-08-02 09:34:58

嗨!我正在寻找Spartan-3A / 3ANFPGA入门KitBoard用户指南(UG334)。具体来说第13章:DDR2 SDRAM和我不明白如何使用DDR2 SDRAM,因为例如这个内存

2019-07-31 06:18:10

本文提出了一种基于FPGA的SDRAM控制器的设计方法,并用Verilog给于实现,仿真结果表明通过该方法设计实现的控制器可以在FPGA芯片内组成如图1所示的SDRAM接口,从而使得系统用户对SDRAM的操作非常方便。

2021-04-15 06:46:56

你好使用Xilinx的任何一个端口MIG DDR2 SDRAM控制器都是我遇到了问题我有vhdl顶级系统,其中我实例化ddr2控制器我的ddr2包装器与testcase一起工作正常(由MIG提供

2019-08-19 10:47:06

嗨,我们从xilnx购买了ML555板。我们想验证该板上的ddr2控制器。我们已经加载了CD中提供的ddr2控制器的位图文件。我们没有观察到为阅读文件中提到的比较逻辑有效的数据提供的任何LED切换。如用户指南中所述,正确生成时钟。让我们知道这种行为的原因。问候--sampath

2019-08-19 09:35:52

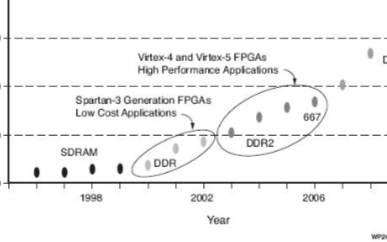

的工作时钟频率。然而,设计至DDR3的接口也变得更具挑战性。在FPGA中实现高速、高效率的DDR3控制器是一项艰巨的任务。直到最近,只有少数高端(昂贵)的FPGA有支持与高速的DDR3存储器可靠接口的块

2019-08-09 07:42:01

嗨,我即将使用Virtex-4QV设备(XQR4VFX140)开始一个新项目。虽然我对使用DDR2 / DDR3 SDRAM的Xilinx MIG有一些经验,但我发现MIG IP不支持VIRTEX-4QV器件。那可能是另类?如何将DDR2 SDRAM与此FPGA连接?弥敦道

2020-04-02 06:08:46

下降的缺陷(甚至于DDR/DDR2又有着不支持单一地址访问的限制,分别至少2/4个地址同时访问)。但是,速度是王道,容量也是它的优势,这些特点是其它任何易失存储器无法媲美的,也是它存在的唯一理由

2014-12-30 15:22:49

DDR SDRAM在嵌入式系统中有哪些应用?DDR SDRAM的工作方式有哪几种?怎样去设计DDR SDRAM控制器?

2021-04-30 07:04:04

FPGA与DDR2存储器接口DDR2控制器的设计原理是什么?DDR2控制器的应用有哪些?

2021-04-30 06:28:13

的内存控制器的设计与应用.pdf基于Spartan-3+FPGA的DDR2+SDRAM存储器接口设计.pdf一种采用FPGA设计的SDRAM控制器.pdf用Xilinx+FPGA实现DDR+SDRAM控制器.pdf

2012-07-28 14:40:53

各位好!之前用DM368的开发板进行实验,目前需要根据自己公司的产品重新画电路板,由于开发板上的FLASH和DDR2 SDRAM过于老旧,需要对这两颗零件重新选型。我不太清楚在选择DDR2

2018-06-21 05:34:23

×16bit)的DDR2 SDRAM为存储器。用一个IP核完成对4片DDR2的控制(带宽为64bit),且DDR2的最高速率可达200MHz,以此完成对数据的高速大容量存储。由于采用一个DDR2的IP核进行控制

2019-05-31 05:00:05

DDR2 SDRAM控制器的设计与实现

本文介绍了&&," -&,+. 的基本特征!并给出了一种&&," -&,+. 控制器的设计方法!详述了其基本结构和设计思想!并使用+JC:8B 公

2010-02-09 14:57:51 64

64 本文介绍了DDR3 SDRAM 的基本特点和主要操作时序,给出了一种基于ALTMEMPHY宏功能的DDR3 SDRAM控制器的设计方法。详述了控制器基本结构和设计思想,分析了各模块功能与设计注意事项,并

2010-07-30 17:13:55 30

30 DDR2 SDRAM 和 FB-DIMM的电气检验:

随着DDR2 SDRAM时钟频率和信号边沿速率不断提高,检查电路板结构、电气系统和信令正变得越来越重要。本应用指南介绍了电路板、电源系统、

2010-08-06 08:29:01 39

39 不只计算机存储器系统一直需要更大、更快、功率更低、物理尺寸更小的存储器,嵌入式系统应用也有类似的要求。本应用指南介绍了逻辑分析仪在检验DDR, DDR2 和DDR3 SDRAM 命令和

2010-08-06 08:29:49 79

79 在高速、大容量存储的系统设计中,DDR2 SDRAM为设计者提供了高性价比解决方案。在FPGA中实现DDR2 SDRAM控制器,降低了系统功耗并节省空间, 缩短开发周期,降低系统开发成本

2010-12-13 17:10:35 49

49 DDR2名词解释

DDR2的定义:

DDR2(Double Data Rate 2) SDRAM是由JEDEC(电子设备工程联合委员会)进行开发的新生代内存技术标准,它与上一代DDR内

2009-04-26 18:02:22 1186

1186

什么是DDR2 SDRAM

DDR2的定义:

DDR2(Double Data Rate 2) SDRAM是由JEDEC(电子设备工程联合委员会)进行开发的新生代内存技

2009-12-17 11:17:59 623

623 DDR2的定义:

DDR2(Double Data Rate 2) SDRAM是由JEDEC(电子设备工程联合委员会)进行开发的新生代内存技术标准,它与上一代DDR内存技术标准最大的不

2009-12-17 16:26:19 731

731 DDR2,DDR2是什么意思

DDR2(Double Data Rate 2) SDRAM是由JEDEC(电子设备工程联合委员会)进行开发的新生代内存技术标准,它与上一代DDR内

2010-03-24 16:06:36 1381

1381 MAX17000A脉宽调制(PWM)控制器为笔记本电脑的DDR、DDR2、DDR3存储器提供完整的电源方案。该器件集成了一路降压控制器、一路可

2010-11-25 09:26:24 682

682

文中在介绍DDR2的工作原理的基础上,给出了一个用VHDL语言设计的DDR2 SDRAM控制器的方法,并且提出了一种在高速图像处理系统中DDR2 SDRAM的应用方案,同时在Virtex-5系列的FPGA上得到了实现

2011-07-23 10:03:16 5102

5102 文章对适用DDR2 SDRAM控制器的结构、接口和时序进行了深入研究与分析,总结出一些控制器的关键技术特性,然后采用了自顶向下(TOP-IX)WN)的设计方法,用Verilog硬件描述语言实现控制器,

2011-09-01 16:36:29 174

174 SDRAM, DDR, DDR2, DDR3 是RAM 技术发展的不同阶段, 对于嵌入式系统来说, SDRAM 常用在低端, 对速率要求不高的场合, 而在DDR/DDR2/DDR3 中,目前基本上已经以DDR2 为主导,相信不久DDR3 将全面取代

2012-01-16 14:53:01 0

0 使用功能强大的FPGA来实现一种DDR2 SDRAM存储器的用户接口。该用户接口是基于XILINX公司出产的DDR2 SDRAM的存储控制器,由于该公司出产的这种存储控制器具有很高的效率,使用也很广泛,

2013-01-08 18:15:50 237

237 ddr2_sdram 操作时序,非常好的教程,可以充分了解DDR2

2015-10-28 11:07:39 19

19 用FPGA设计DDR2控制器讲解DDR2时序原理用户接口设计帮助用户快速掌握DDR2的控制技术新手上路的非常有帮助的资料。

2015-11-10 10:54:14 3

3 DDR2 SDRAM操作时序规范,中文版规范

2015-11-10 17:42:44 0

0 带自测功能的DDR2控制器设计,感兴趣的可以看看。

2016-01-04 15:23:32 0

0 Xilinx FPGA工程例子源码:DDR2 Controller

2016-06-07 11:44:14 24

24 Xilinx FPGA工程例子源码:DDR SDRAM控制器参考设计VHDL代码

2016-06-07 11:44:14 19

19 Xilinx FPGA工程例子源码:DDR SDRAM控制器verilog代码

2016-06-07 14:13:43 38

38 Xilinx FPGA工程例子源码:Xilinx DDR2存储器接口调试代码

2016-06-07 14:54:57 27

27 DDR2SDRAM控制器在机载显控系统中的应用_孙少伟

2017-03-19 11:26:54 1

1 SDRAM):DDR4提供比DDR3/ DDR2更低的供电电压1.2V以及更高的带宽,DDR4的传输速率目前可达2133~3200 MT/s。

2017-11-17 13:15:49 25152

25152 控制器用户接口设计方案。该控制器用户接口已经在Xilinx 公司的VC707 开发板上通过了功能验证,并成功的被应用到高速图像数据采集系统中。

2017-11-17 14:14:02 3290

3290

原理,并对DDR2控制器的IP核进行了模块化的划分,分析了每个模块的功能。强调了用户接口功能的完善,并介绍了IP核的操作流程,使每个用户都能轻松的使用该IP核。

2017-11-22 07:20:50 4687

4687

DDR2(Double Data Rate2)SDRAM是由JEDEC(电子设备工程联合委员会)制定的新生代内存技术标准,它与上一代DDR内存技术标准最大的不同:虽然采用时钟的上升/下降沿同时传输

2017-11-25 01:41:01 3855

3855

DRAM (动态随机访问存储器)对设计人员特别具有吸引力,因为它提供了广泛的性能,用于各种计算机和嵌入式系统的存储系统设计中。本文概括阐述了DRAM 的概念,及介绍了SDRAM、DDR SDRAM、DDR2 SDRAM、DDR3 SDRAM、DDR4 SDRAM、LPDDR、GDDR。

2018-06-07 22:10:00 91644

91644 本文档介绍了DDR2内存控制器在tms320dm646x数字媒体片上系统(dmsoc)的DDR2内存控制器。

DDR2内存控制器是用来与jesd79d-2a标准兼容的DDR2 SDRAM接口

2018-04-18 10:45:10 4

4 2 协议,并遵从 JEDEC 标准 JESD79-2F (2009 年 11 月)的电气接口来实现对外部存储器总线接口的控制。组件包括带可配置选项的 DDR SDRAM 控制器内核及 DDR 物理接口。

2018-05-30 09:29:00 7

7 ,因此能够很好地满足上述场合对大量数据缓存的需求。但DDR SDRAM的接口不能直接与现今的微处理器和DSP的存储器接口相连,需要在其间插入控制器实现微处理器或DSP对存储器的控制。

2019-07-02 08:03:00 4051

4051

操作,设计了DDR SDRAM 的数据与命令接口。用控制核来简化对DDR SDRAM 的操作,并采用自顶至下模块化的设计方法,将控制核嵌入到整个数据采集系统的控制模块中,完成了数据的高速采集、存储及上传

2019-08-14 08:00:00 3401

3401

DDR2 设备概述:DDR2 SDRAM接口是源同步、支持双速率传输。比如DDR SDRAM ,使用SSTL 1.8V/IO电气标准,该电气标准具有较低的功耗。与TSOP比起来,DDR2 SDRAM的FBGA封装尺寸小得多。

2019-06-22 10:05:01 1793

1793

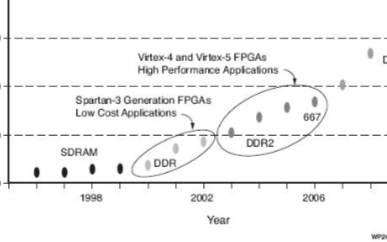

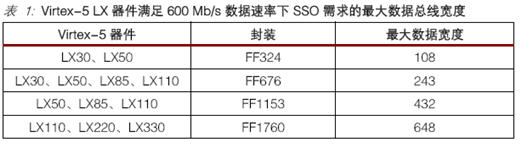

20 世纪 90 年代后期,存储器接口从单倍数据速率 (SDR) SDRAM 发展到了双倍数据速率 (DDR) SDRAM,而今天的 DDR2 SDRAM 运行速率已经达到每引脚 667 Mb

2020-04-12 10:57:53 995

995

DDR2 SDRAM采用双数据速率结构实现高速运行。双数据速率体系结构本质上是4n预取体系结构,其接口设计为在I/O球处每个时钟周期传输两个数据字。DDR2 SDRAM的单次读写操作有效地包括在内部

2020-05-21 08:00:00 1

1 、PSRAM、MRAM等存储芯片供应商英尚微电子解析这款比脑力更强大的DDR SDRAM控制器。 任何DRAM控制器背后的智商都是与命令时序和执

2020-07-24 14:25:27 719

719 DDR对于做项目来说,是必不可少的。一般用于数据缓存和平滑带宽。今天介绍下Xilinx DDR控制器MIG IP核的例化及仿真。 FPGA芯片:XC7K325T(KC705) 开发工具:Vivado

2020-11-26 15:02:11 7386

7386

本文首先分析了DDR SDRAM的基本特征,并提出了相应的解决方案详细介绍了基于J EDEC DDR SDRAM规范的DDR SDRAM控制器设计方案。该控制器采用Verilog HDL硬件描述语言实现,并集成到高性能SoC中。

2021-03-28 10:57:24 18

18 基于FPGA的DDR3SDRAM控制器设计及实现简介(arm嵌入式开发平台PB)-该文档为基于FPGA的DDR3SDRAM控制器设计及实现简介资料,讲解的还不错,感兴趣的可以下载看看…………………………

2021-07-30 09:05:51 7

7 基于FPGA的DDR3SDRAM控制器设计及实现(嵌入式开发式入门)-该文档为基于FPGA的DDR3SDRAM控制器设计及实现总结文档,是一份很不错的参考资料,具有较高参考价值,感兴趣的可以下载看看………………

2021-07-30 13:07:09 35

35 ,以及对应的波形图和 Verilog HDL 实现。我们调取的 DDR3 SDRAM 控制器给用户端预留了接口,我们可以通过这些预留的接口总线实现对该 IP 核的控制,本章节将会讲解如何根据 Xilinx 官方提供的技术参数来实现对 IP 核的写控制。写命令和写数据总线介绍DDR3 SDRAM控制器I

2021-12-04 19:21:05 4

4 DDR2总线的仿真方法,基于Agree公司最新的网络处理器APP300和HY的

DDR2 SDRAM HY5PS121621。

2022-10-21 16:09:58 0

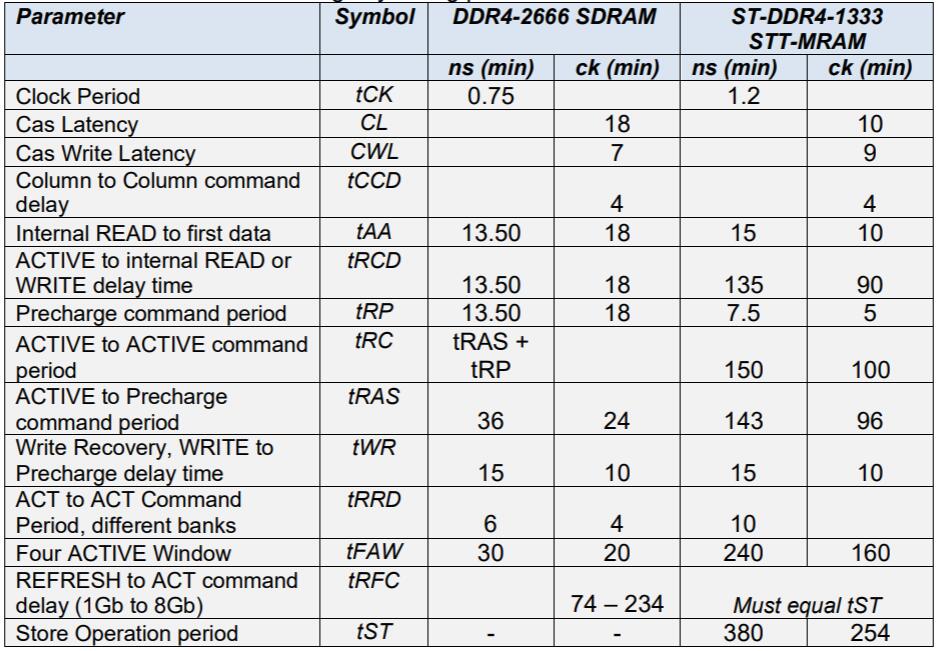

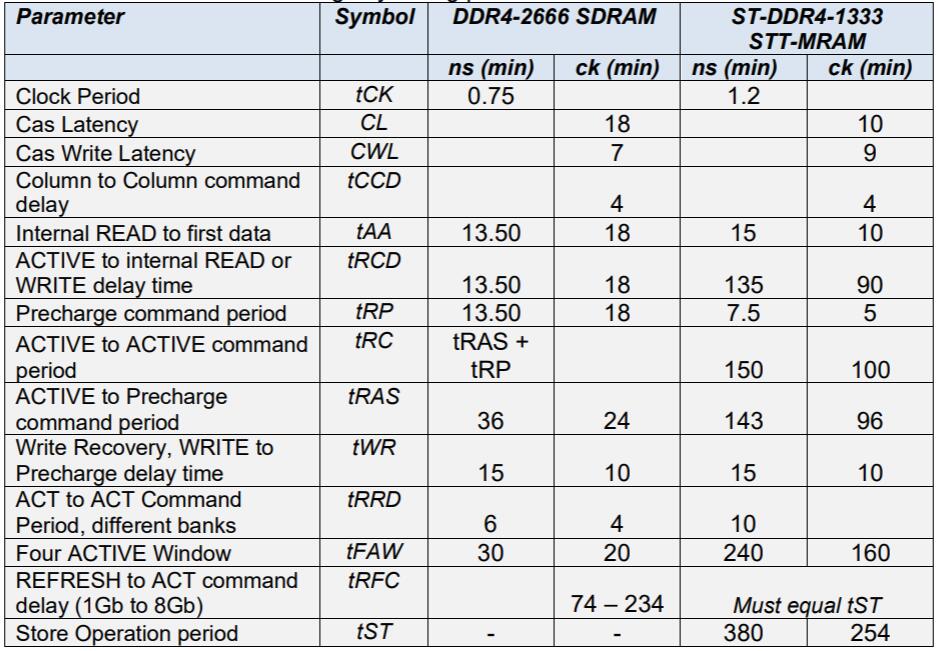

0 为了使设计人员能够快速集成ST-DDR4支持,该过程从Xilinx Vivado开发环境中生成的现有8Gb DDR4 SDRAM-2666存储器接口生成器(MIG)开始。

2022-11-17 14:35:21 666

666

电子发烧友网站提供《完整的DDR、DDR2和DDR3内存电源解决方案同步降压控制器数据表.pdf》资料免费下载

2024-03-13 10:16:45 0

0

电子发烧友App

电子发烧友App

评论