静态时序分析包括建立时间分析和保持时间分析。建立时间设置不正确可以通过降低芯片工作频率解决,保持时间设置不正确芯片无法正常工作。

2022-08-22 10:38:24 3291

3291 建立时间(setup time)和保持时间(hold time)是时序分析中最重要的概念之一,深入理解建立时间和保持时间是进行时序分析的基础。

2023-06-21 10:44:01 885

885

今天有个小伙伴遇到一个问题,就是在vivado里面综合后看到的建立时间和保持时间裕量都是inf,我们来看看怎么解决这个问题。

2023-07-30 10:26:02 649

649

我理解这个D触发正常运转要满足四个约束,第一个是建立时间,第二个是保持时间,第三个是对于最后一个传输门的关断时间的控制,第四个是[时钟周期]() 约束。

2023-12-04 15:44:02 352

352

ADC时延和建立时间的区别是什么?以及ADC时延和建立时间将会如何影响您的应用电路?

2021-04-12 07:19:18

;Tpd 为时钟到 T1 和 T2 的偏差;在一个时钟周期 T 之内,数据从寄存器 T1 传出,需要经过延时 Tco,然后经过组合逻辑,需要经过延时 Tdelay,最后到达寄存器 T2,然后在寄存器 T2 建立起来,需要经过延时 Tsetup,那么可以得出建立时间的要求:Tsetup

2015-03-10 23:19:03

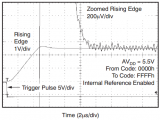

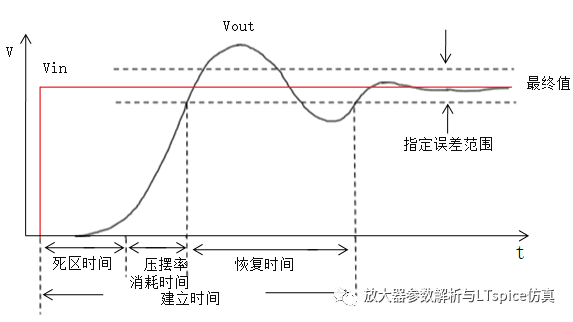

作者: TI专家 Bruce Trump翻译: TI信号链工程师 Michael Huang (黄翔) 建立时间是运放阶跃响应进入和停留在最终值的特定误差范围内的所需时间。它在一些应用中十分重要

2018-09-20 16:32:36

。

问题:

写完AD模式寄存器启动单次采样后,至首个通道RDY信号有效,间隔约为78us,后面3个通道均为56us(与描述手册相同),请问第一个建立时间为何多出20us?使一次采样超出了系统的中断周期。

谢谢大家!

2023-12-13 09:00:30

寄存器启动单次采样后,至首个通道RDY信号有效,间隔约为78us,后面3个通道均为56us(与描述手册相同),请问第一个建立时间为何多出20us?使一次采样超出了系统的中断周期。谢谢大家!

2019-02-14 15:24:34

Hi,All AD7195数据手册中讲,当选择Sinc(4)滤波(禁用斩波,禁用零延时),在通道切换或单个通道上进行转换且输入发生阶跃变化时,ADC建立时间为4/fadc。 我的问题时,如果使用了

2018-11-06 09:08:07

(1)AD8436的建立时间就是内部的5K电阻乘以外部的CAVG的电容值吗?

(2)按照数据手册中的图28显示,如果输入信号为20khz的正弦波,那么要保证精度在0.5以内,那么选择0.01uF的电容可以吗?图28没有给出高于1K的频率时电容如何选择?

2023-12-07 08:25:19

有没有人遇到在DC综合后分析建立时间时序,关键路径时序违例是因为起始点是在时钟的下降沿开始驱动的,但是设计中都是时钟上升沿触发的。在线等待各位大牛解惑!很急 求大神帮忙!

2015-01-04 15:17:16

建立时间和保持时间本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt 在这个波形中,我们看到clk_r3的前后

2015-07-17 12:02:10

几天前量测了下intel 南桥发出到一个电源控制器的I2C信号,发现数据建立时间(hold time)只有150ns左右,I2C协议里面所说至少300ns,这个问题该怎么解决啊 求大神指导建立时间有

2013-12-08 00:38:24

PLL jitter 对建立时间和保持时间有什么样的影响?哪位大神给解答下

2015-10-30 11:16:30

的问题)应使RC滤波电路的-3dB带宽尽可能地宽,缩短反向建立时间,使ADC在tACQ时间对阶跃输入有18-bit的建立精度。但是RC滤波电路的-3dB带宽变宽,使得进入到ADC的噪声也相应的增加了,如此

2018-11-13 09:28:42

简单的来分析一下数据的建立时间和保持时间应该满足怎样的关系才能保证被时钟lcd_clk稳定的锁存到ADV7123芯片中。首先,我们需要来看看这个实例的时钟launch edge和latch edge

2019-04-10 06:33:34

在为ad7610选择一个单电源的驱动放大器,手册中推荐的ad8021是双电源,建立时间参数为:Settling Time to 0.01% VO = 1 V step, RL = 500 Ω 23

2023-11-17 06:22:37

。AD7175系列ADC允许选择不同类型的滤波器。下一部分将介绍不同类型滤波器之间的区别,并提供一个例子来说明如何计算各种情况下的建立时间。现在看看多路复用情况下的建立时间。在过程控制和工厂自动化中

2018-10-16 21:39:01

关于 ADS1298,我想澄清下列问题:1. 为什么 ADS1298 在初始化过程中 START 引脚的建立时间会有延迟?如果输入信号在该建立时间过程中 (tsettle) 发生变化,会出现什么情况

2019-05-30 14:50:14

什么是同步逻辑和异步逻辑?同步电路和异步电路的区别在哪?为什么触发器要满足建立时间和保持时间?

2021-09-28 08:51:33

什么是同步逻辑和异步逻辑?同步电路和异步电路的区别在哪?为什么触发器要满足建立时间和保持时间?什么是亚稳态?为什么两级触发器可以防止亚稳态传播?

2021-08-09 06:14:00

什么叫建立时间,保持时间,和恢复时间

2017-04-08 16:52:35

1、FPGA中的时序约束--从原理到实例 基本概念 建立时间和保持时间是FPGA时序约束中两个最基本的概念,同样在芯片电路时序分析中也存在。 电路中的建立时间和保持时间其实跟生活中的红绿灯很像

2022-11-15 15:19:27

。这种方法把准确性和精确度建立在波形生成器和采样保持电路的相对速度上。 受测器件的步进输入 本文中,建立时间是指使用某个理想步进输入,到受测器件(DUT)进入并维持在某个规定误差范围(终值对称)内

2012-07-30 17:36:20

如图,建立时间和保持时间都是针对的时钟沿,如图所示,时钟沿有一个上升的过程,图中虚线与clk上升沿的交点是什么?幅值的50%?还是低电平(低于2.5V)往高电平(高于2.5V)跳转的那个点?

2018-11-29 00:20:02

传输介质所用的时间。在传输线上的时延就是指信号通过整个传输线所用的时间。 Propagation delay又叫传播延迟(PD),通常是指电磁信号或者光信号在单位长度的传输介质中传输的时间

2014-10-21 09:54:56

关于数字IC的建立时间以及保持时间你想知道的都在这

2021-09-18 07:24:40

已做简要说明。转换器要产生有效数据,毛刺必须稳定在输出的1 LSB以内,而输入稳定在1 LSB以内(并保持在该范围内!)所需的时间就是输入建立时间(tS)。tS是前面描述的延迟td的组成部分,它对

2018-10-23 14:32:23

ADC、容性 DAC 和采样电路等)的开关应用更为普遍。转换器要产生有效数据,毛刺必须稳定在输出的1 LSB以内,而输入稳定在 1 LSB 以内(并保持在该范围内!)所需的时间就是输入建立时间(tS

2018-10-29 17:06:48

在多通道多路复用数据采集系统中,增加每个ADC的通道数量可改善系统的整体成本、面积和效率。现代逐次逼近寄存器模数转换器(SAR ADC)具有高吞吐量和高能效,使得系统设计人员能够实现比以往更高的通道

2020-12-28 07:30:52

对于一个ADF芯片,比如手上有一块ADF4016,如果外围条件稳定,外围触发信号的时刻及幅度都能确定,内部器件稳态建立时间是否每次都有区别?如果不是,稳态建立需要的时间精度能到什么级别?我看说明书上只写了T1-T6的稳态所需最小时间,没有精度说明,有没有相关的资料?

2018-10-29 09:13:25

一个较高水平。关键词:FPGA 数字电路 时序 时延路径 建立时间 保持时间1 数字电路设计中的几个基本概念:1.1 建立时间和保持时间:建立时间(setup time)是指在触发器的时钟信号上升沿

2012-10-26 17:24:58

建立时间测量的采样保持方法测试装置存在哪些局限性?

2021-04-09 06:08:05

就可以乘坐,必须的提前到站的时间就是建立时间。 如果数据信号在时钟沿触发前的持续时间超过了建立时间Tsu...

2021-07-26 07:36:01

请问,对于触发器的时钟信号,建立时间和保持时间有要求吗?刚看到一个门控时钟产生毛刺的反例,(如下图)想到了这个问题。若此时钟信号毛刺极小,有没有可能被触发器忽略呢?为什么呢?如果有可能小到什么程度会被忽略呢?

2012-01-27 18:44:58

小于说明书中规定的建立时间规范,那么系统建立所用的时间就会变短。在大部分高精度应用中,建立时间是 DAC 的有效更新速率。本文将对DAC 基础知识做一个终结。此外,别忘了观看我同事 Rahul Prakash 主讲的最新“设计精萃”视频 — 关于乘法 DAC (MDAC)。

2018-09-13 09:56:17

建立时间是什么意思?精确测量ADC驱动电路建立时间

2021-04-14 06:29:09

有朋友问我,用我司BigTao200测试仪测试交换机时,在时延的统计项中有“直通时延”和“存储转发时延”,二者的区别在哪里?我的理解是这样的——存储转发时延是数据最后一个比特到达设备输入端口的时间

2014-08-26 16:29:34

AD8021的建立时间具体是多少,在Datasheet上The AD8021 is a well-behaved amplifier that settles to 0.01% in 23 ns

2018-07-30 06:55:57

您好:我在ADE7880的文档中多处看到建立时间,那我在配置或者在编程中如何去考虑这个建立时间?

2018-11-05 09:00:08

1.有效值采集问题1)有效值采集中的建立时间(settling time)是指从上电到有效值稳定的时间吗?两次读取有效值的最小时间间隔与建立时间有关系吗?2)有效值中建议过零点的时候进行有效值的读取

2019-03-05 14:30:09

一般运算放大器的datasheet都会给出0.01%建立时间(有的给出0.1%建立时间),比如ADA4897,给出2V阶跃测试时0.01%建立时间为90 ns。

因此对于单运放电路来说,建立时间

2023-11-27 06:54:56

一般运算放大器的datasheet都会给出0.01%建立时间(有的给出0.1%建立时间),比如ADA4897,给出2V阶跃测试时0.01%建立时间为90 ns。因此对于单运放电路来说,建立时间可以

2018-11-13 15:08:15

在为ad7610选择一个单电源的驱动放大器,手册中推荐的ad8021是双电源,建立时间参数为:Settling Time to 0.01% VO = 1 V step, RL = 500 Ω 23

2018-08-01 09:25:24

如何增加ESP32-S2 以太网SPI接口的CS建立时间?(1)问题现象:偶尔出现_[0;31mE (6321) dm9051.mac: buffer size too small, needs

2023-02-15 06:55:16

T2max,最小为T2min。问,触发器D2的建立时间T3和保持时间应满足什么条件

2019-09-09 17:19:55

计算开关电容ADC的建立时间:很多C8051F器件具有片内模/数转换器ADC这些ADC使用一个采样电容该电容被充电到输入信号电压由SAR逻辑进行数据转换由于存在ADC采样电容输入阻抗和外部输

2008-10-30 18:25:08 24

24 该文简要讨论了环路性能(建立时间,相位噪声和杂散信号)和环路参数(带宽,相位裕度等)的相互关系。提出并分析了一种自适应的具有快速建立时间的锁相环结构及其关键模块(鉴相

2010-04-23 08:33:53 20

20 常估算运算放大器建立时间的方法受示波器分辨率或电路寄生的制约,而且这些方法都未考虑模数转换器(ADC)的采样电路、封装寄生电容和电感等因素。对此给出了一个精

2010-12-20 17:51:37 39

39 基本概念:线与逻辑、锁存器、缓冲器、建立时间、缓冲时间

基本概念:线与逻辑、锁存器、缓冲器、建立时间、缓冲时间

标签/分类:

2007-08-21 15:17:27 1169

1169 用于测试运算放大器建立时间的基本设备包括:一个高品 质(且昂贵)的平顶脉冲发生器用作DUT的输入;一个 DUT测试夹具,在运算放大器插口电源引脚处具有电源和 旁路电容;以及一个

2011-03-28 17:19:44 0

0 本文将介绍一种新方法,其经过证明可以有效地完成这些测量工作。它是一种相对低成本、简单的建立时间测量方法。这种方法把准确性和精确度建立在波形生成器和采样保持电路的相

2012-07-27 10:25:16 1034

1034

如何计算多路复用器的建立时间和采样速率

2013-08-21 17:33:12 0

0 建立时间和保持时间贯穿了整个时序分析过程。只要涉及到同步时序电路,那么必然有上升沿、下降沿采样,那么无法避免setup-time 和 hold-time这两个概念。 1. 什么是setup-time

2017-02-08 14:48:11 4928

4928 今天,我们将介绍两种相关的动态参数 — 压摆率与建立时间。如欲了解更多有关静态和动态参数的不同之处,敬请参阅本文。

2018-07-10 16:14:00 5294

5294

本篇仿真介绍放大器的建立时间,也称为上升时间。它是高速放大电路、或在SARADC驱动电路设计时,需要谨慎评估的参数。

2021-02-15 16:37:00 5258

5258

AN-1024: 如何计算多路复用器的建立时间和采样速率

2021-03-21 09:43:42 7

7 MT-046:运算放大器建立时间

2021-03-21 11:48:10 11

11 AN-256:准确测试运算放大器建立时间

2021-04-17 19:28:04 1

1 AN74组件和测量改进确保16位DAC建立时间

2021-04-20 08:04:18 8

8 AN10-运算放大器建立时间的测量方法

2021-04-27 15:21:40 2

2 AN-359:运算放大器的建立时间

2021-04-29 15:28:46 3

3 AD5399:二进制补码、双12位DAC,带内部基准电压源和快速建立时间数据表

2021-05-18 16:53:00 0

0 宽带放大器的128-2纳秒、1%分辨率的建立时间测量

2021-05-25 17:05:58 6

6 AN79-30纳秒精密宽带放大器建立时间测量

2021-05-27 09:22:10 7

7 本篇通过仿真介绍放大器的建立时间,也称为上升时间。它是高速放大电路、或在SAR ADC驱动电路设计时,需要谨慎评估的参数。

2023-02-22 11:29:31 286

286

运算放大器建立时间是保证数据采集系统性能的关键参数。为了实现精确的数据采集,运算放大器输出必须在A/D转换器能够准确数字化数据之前建立。然而,建立时间通常不是一个容易测量的参数。

2023-06-17 10:37:54 368

368

本文主要介绍了建立时间和保持时间。

2023-06-21 14:38:26 1081

1081

在时序电路设计中,建立时间/保持时间可以说是出现频率最高的几个词之一了,人们对其定义已经耳熟能详,对涉及其的计算(比如检查时序是否正确,计算最大频率等)网上也有很多。

2023-06-27 15:43:55 4597

4597

建立时间和保持时间是SOC设计中的两个重要概念。它们都与时序分析有关,是确保芯片正常工作的关键因素。

2023-08-23 09:44:55 390

390 信号经过传输线到达接收端之后,就牵涉到建立时间和保持时间这两个时序参数,它们表征了时钟边沿触发前后数据需要在锁存器的输入持续时间,是接收器本身的特性。简而言之,时钟边沿触发前,要求数据必须存在一段时间,这就是器件需要的建立时间;

2023-09-04 15:16:19 393

393

电子发烧友网站提供《多路复用器的建立时间和采样速率的计算.pdf》资料免费下载

2023-11-24 11:03:17 0

0 文件提到两种setup/hold测量方式:10% push-up和pass/fail,按照TSMC说法,前者会更乐观一些,因此如果是采用前者(10% push-up)的测量方式得到建立时间和保持时间,需要十份小心时序裕量是否足够,最好人为添加margin。

2023-12-05 11:19:38 696

696

电子发烧友App

电子发烧友App

评论