静态时序分析包括建立时间分析和保持时间分析。建立时间设置不正确可以通过降低芯片工作频率解决,保持时间设置不正确芯片无法正常工作。

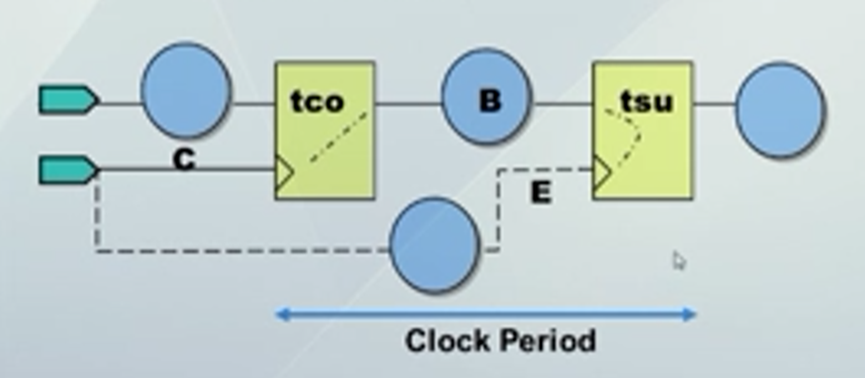

保持时间分析与建立时间分析的电路结构相同。需要分析的变量与建立时间分析的变量相似,包括:C(时钟信号传递到源触发器的延时)、E(时钟信号传递到目标触发器的延时)、B(从源触发器到目标触发器所经过的组合逻辑电路的延时)、tco(源触发器延时)。

图一,图片来源:学堂在线《IC设计与方法》

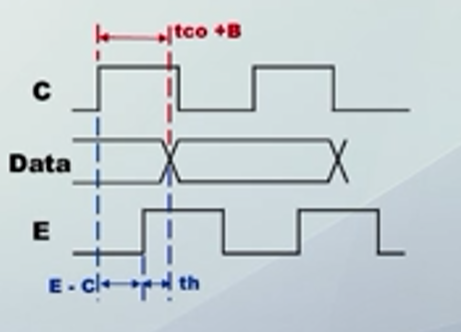

结合图一和图二说明建立时间和保持时间。

建立时间的设置需保证时钟信号到达目标触发器前,数据信号已在目标触发器稳定建立,在图二波形图中显示为Data数据的替换的时间点先于E的第二个时钟上升沿。

保持时间的设置需保证数据信号在目标触发器稳定建立前,数据信号可以一直保持,源触发器的下一个数据信号未替换当前信号,在图二的波形图中显示为Data数据替换的时间点滞后于E的第一个时钟上升沿。即满足如下公式:

tco+B>E-C+th

其中th为保持时间。

图二,图片来源:学堂在线《IC设计与方法》

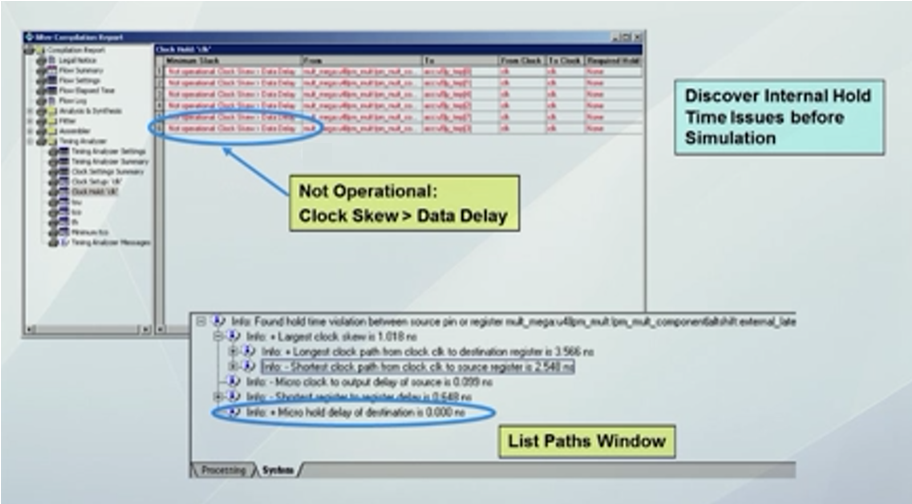

图三是Quartus Ⅱ工具关于保持时间的分析结果,图中红色字部分显示保持时间设置错误,原因是Clock Skew>Data Delay,其中ClockSkew=E-C,Data Delay=tco+B。设计人员可以通过Quarus Ⅱ工具观测保持时间分析结果的具体值,如ClockSkew的值为1.018ns等。

图三,图片来源:学堂在线《IC设计与方法》

设计人员除了进行电路内部的时序分析,还需进行电路输入路径和输出路径的时序分析。

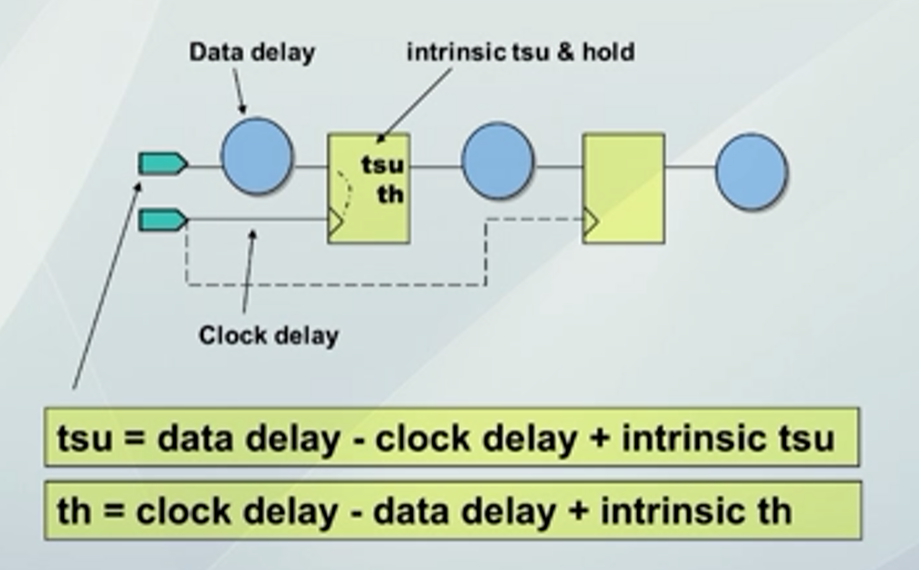

输入路径的建立时间和保持时间计算:基于内部建立时间(intrinsic tsu)和保持时间(intrinsic th),结合输入数据延时(data delay)和时钟延时(clock delay),得出如图四所示的两个公式(tsu为建立时间、th为保持时间)。

图四,图片来源:学堂在线《IC设计与方法》

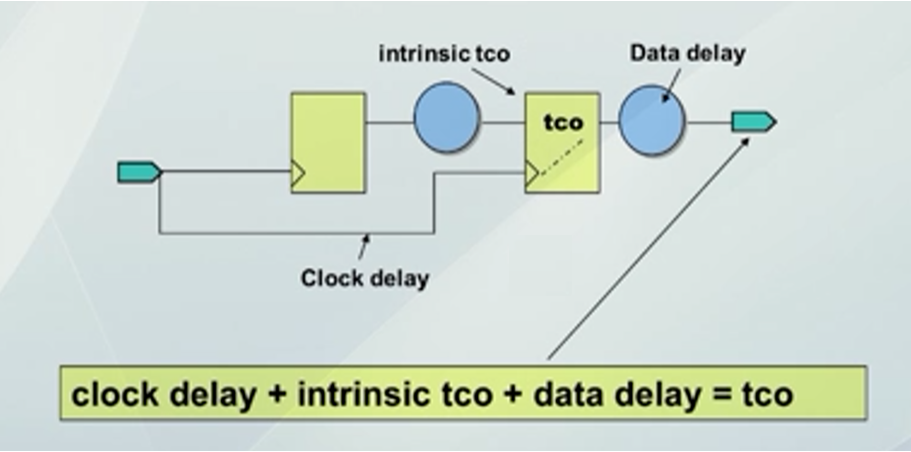

输出路径的延时计算公式如图五所示,将内部延时、数据延时、时钟延时相加得出输出路径延时。

图五,图片来源:学堂在线《IC设计与方法》

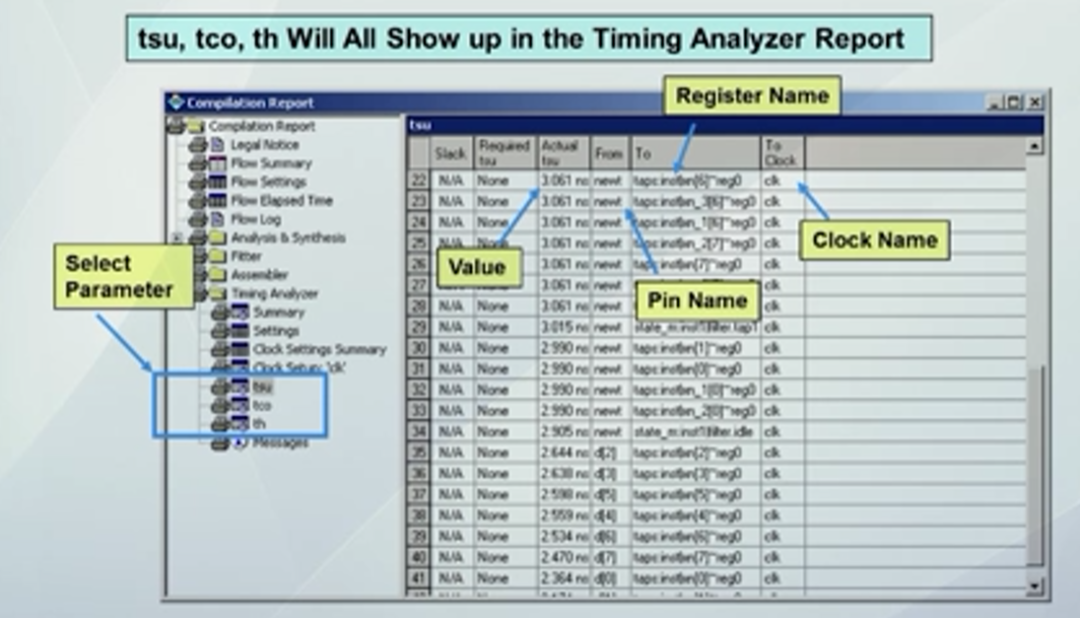

图六展示了Quartus Ⅱ工具关于输入路径、输出路径时序分析结果。Quartus Ⅱ工具会分析所有路径,并将延时最长路径放置在最靠上的位置。每条路径的信息包括延时时长、输入引脚、输出到的寄存器、时钟信号。

由图六可以发现,输入路径(虚拟D触发器)最长的建立时间为3ns,大于内部D触发器建立时间(内部D触发器的建立时间为0.1ns-0.3ns)。

因此,如果设计人员需要设计高性能电路,需要尽可能将数据传递路径(包括内核运算逻辑和数据保存)设计在芯片内部。如果芯片设计的数据路径经过芯片外部器件如SRAM(一种寄存器),芯片性能会大幅下降。

图六,图片来源:学堂在线《IC设计与方法》

总结芯片时序分析过程,包括芯片内部保持时间分析和建立时间分析、输入路径保持时间分析和建立时间分析、输出延时分析。时序分析在芯片设计中具有重要作用,如果时序分析结果不能满足要求,一般需要修改芯片设计代码。

审核编辑:刘清

-

触发器

+关注

关注

14文章

2065浏览量

63606 -

组合逻辑电路

+关注

关注

6文章

71浏览量

15189 -

时钟信号

+关注

关注

4文章

511浏览量

30149

原文标题:芯片设计相关介绍(33)——保持时间和建立时间

文章出处:【微信号:行业学习与研究,微信公众号:行业学习与研究】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

芯片设计进阶之路—从CMOS到建立时间和保持时间

FPGA时序分析-建立时间和保持时间裕量都是inf怎么解决呢?

建立时间和保持时间讨论

FPGA实战演练逻辑篇57:VGA驱动接口时序设计之4建立和保持时间分析

保持时间与建立时间

建立时间和保持时间(setup time 和 hold time)

PCB传输线建立时间、保持时间、建立时间裕量和保持时间裕量

关于建立时间和保持时间的测量方法

静态时序之建立时间和保持时间分析

静态时序之建立时间和保持时间分析

评论