单稳态触发器原理及应用

多谐振荡器是一种自激振荡电路。因为没有稳定的工作状态,多谐振荡器也称为无稳态电路。具体地说,如果一开始多谐振荡器处于0状态,那

2010-05-27 09:34:28 4668

4668

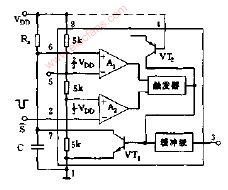

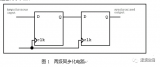

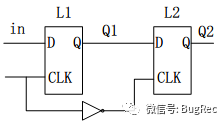

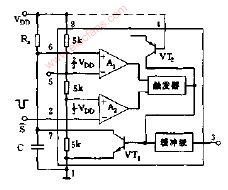

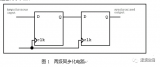

图中所示是用CMOS电路D触发器组成的单稳态多谐振荡器.因为D触发器除了具有传送D端数据的功能外,还具

2010-09-21 00:08:57 4665

4665

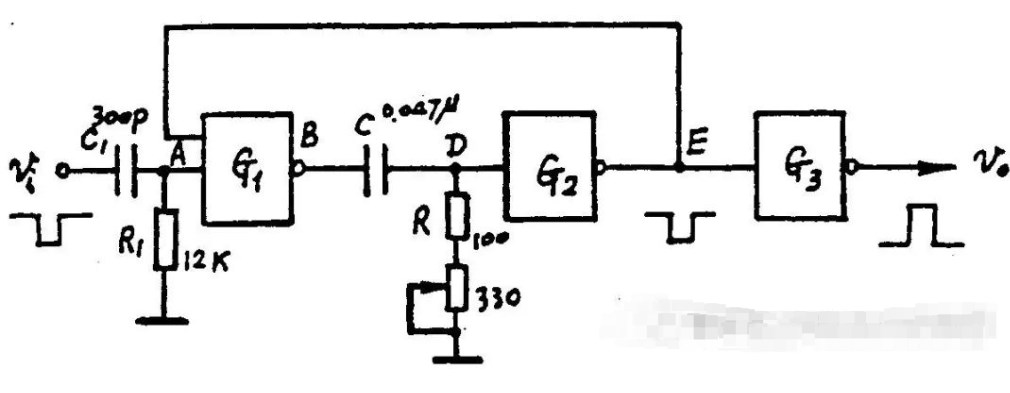

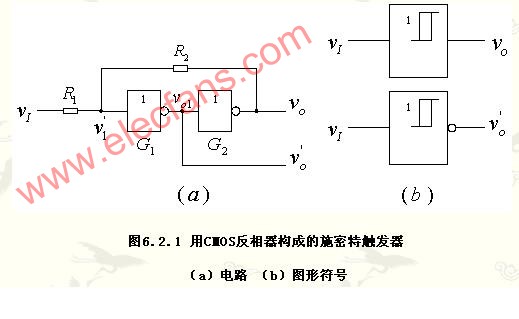

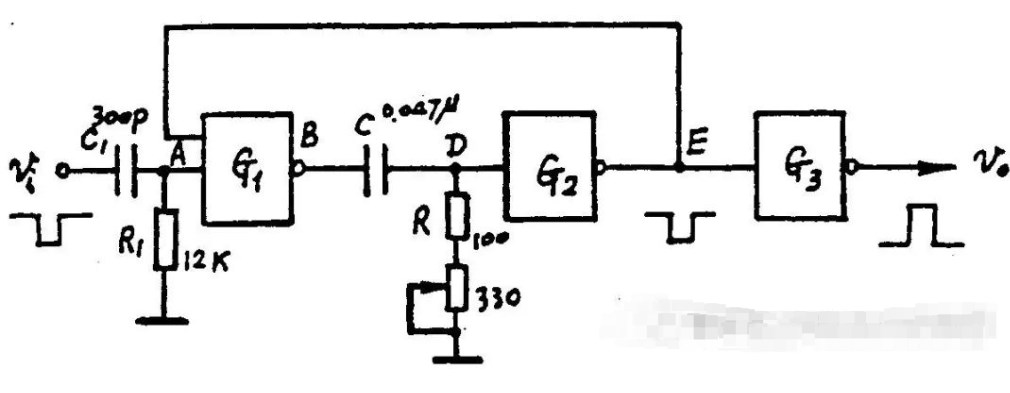

用CMOS与非门或者或非门都可以组成单稳态触发器,这种单稳态触发器在电路中广泛地用于对脉冲信号的延

2010-12-01 13:49:36 11674

11674

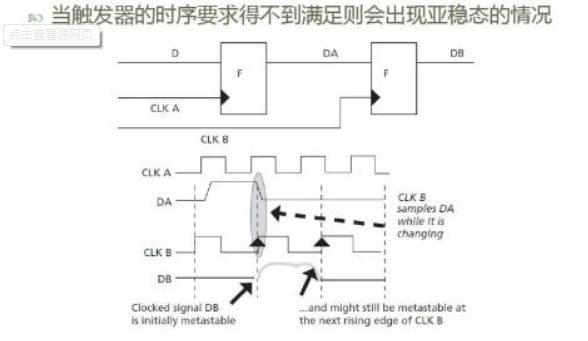

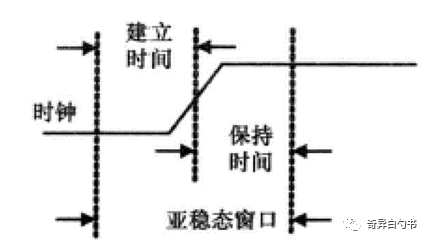

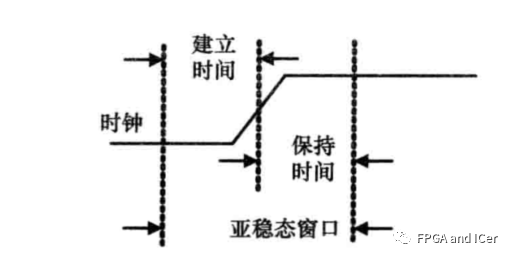

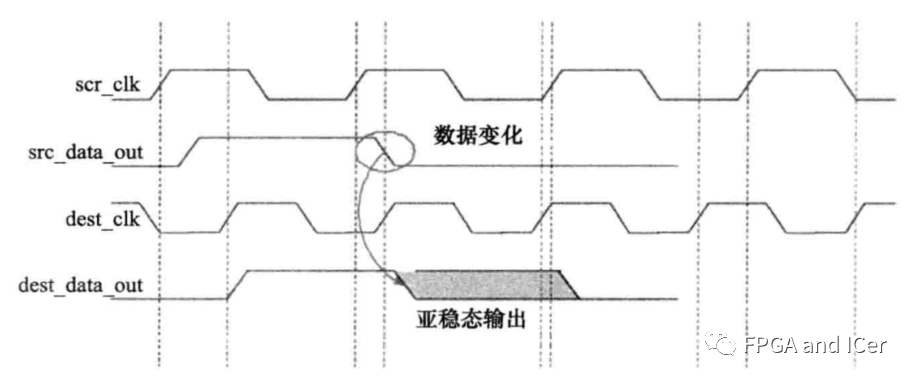

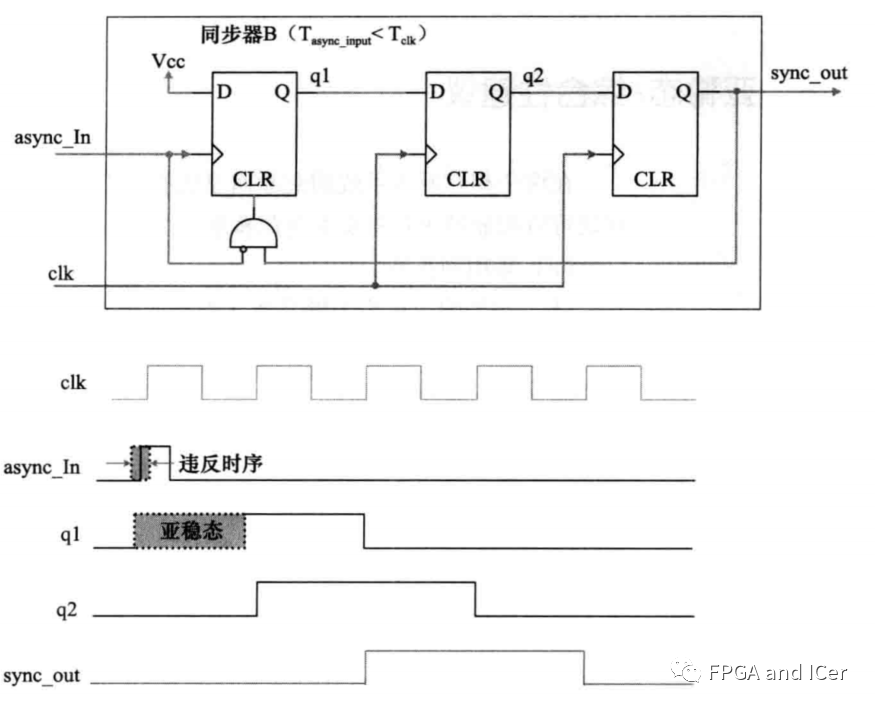

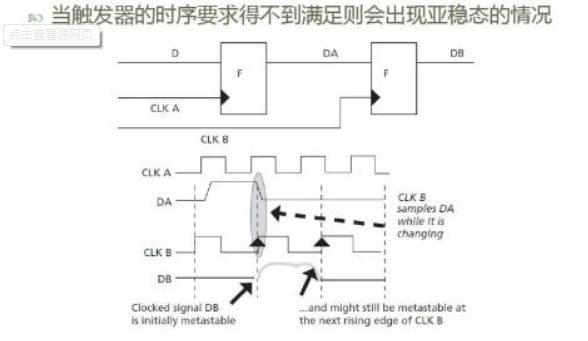

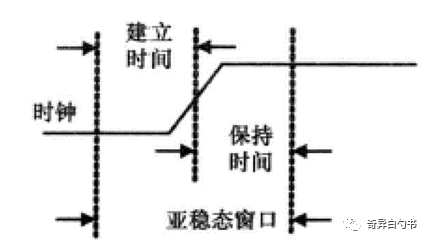

发生亚稳态的原因是信号在传输的过程中不能满足触发器的建立时间和保持时间。

2023-06-20 15:29:58 2210

2210

在 FPGA 系统中,如果数据传输中不满足触发器的 Tsu 和 Th 不满足,或者复位过程中复位信号的释放相对于有效时钟沿的恢复时间(recovery time)不满足,就可能产生亚稳态,此时触发器

2020-10-22 11:42:16

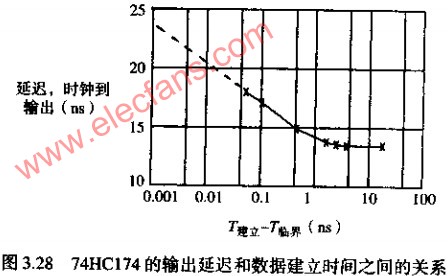

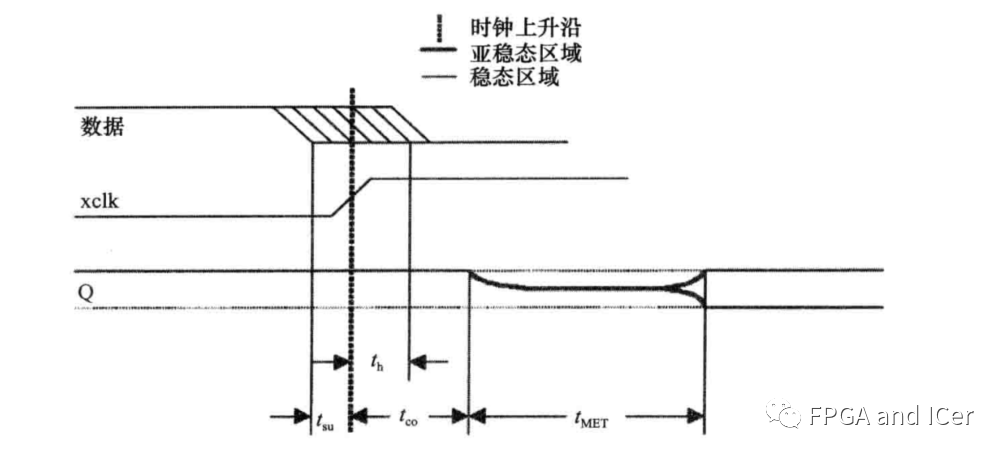

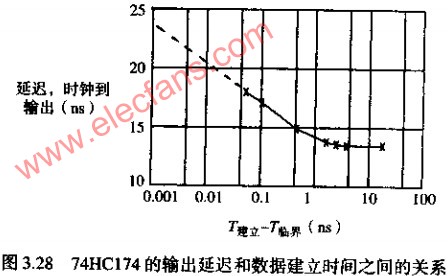

的问题。亚稳态的特点: 1. 增加触发器进入稳定状态的时间。 亚稳态的坏处之一是会导致触发器的TCO时间比正常情况要大。多出来的时间tR (resolution time) 就是亚稳态持续的时间,参考图1

2012-12-04 13:51:18

产生亚稳态,此时触发器输出端Q在有效时钟沿之后比较长的一段时间处于不确定的状态,在这段时间里Q端在0和1之间处于振荡状态,而不是等于数据输入端D的值。这段时间称为决断时间(resolution

2012-01-11 11:49:18

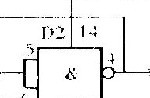

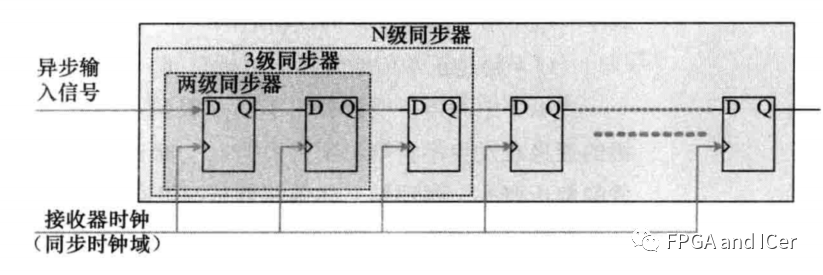

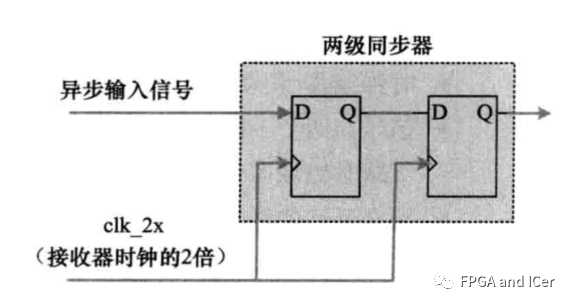

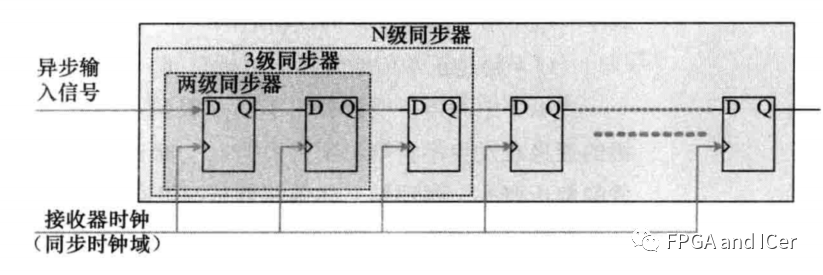

,也就是Tsu和Th时间较小的FPGA器件;2.3.2 亚稳态的串扰概率使用异步信号进行使用的时候,好的设计都会对异步信号进行同步处理,同步一般采用多级D触发器级联处理,如图3.6所示,采用三级D

2012-04-25 15:29:59

说起亚稳态,首先我们先来了解一下什么叫做亚稳态。亚稳态现象:信号在无关信号或者异步时钟域之间传输时导致数字器件失效的一种现象。

2019-09-11 11:52:32

要求的,进而出现亚稳态。但是有人认为, “cnt”的值原来是零,“clr_cnt”只是把”cnt”的值清零, 这样来说触发器“cnt”的输入根本没有发生过变化,怎么可能有亚稳态事件? 而且故障出现的概率

2012-12-04 13:55:50

`作者:Primitivo Matas Sanz,技术专家,西班牙马德里Telefonica I+D 公司,技术专家现身说教,使用触发器链(赛灵思FPGA 中ILOGIC 块的组成部分)限制设计中

2012-03-05 14:11:41

是为了防止触发器变成亚稳态`timescale 1ns / 1psmodule key_test(inputclk,input [3:...

2021-07-30 06:44:48

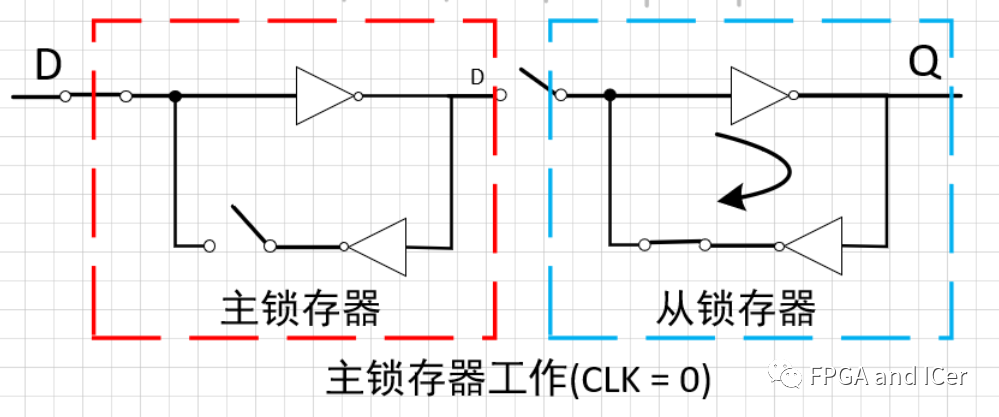

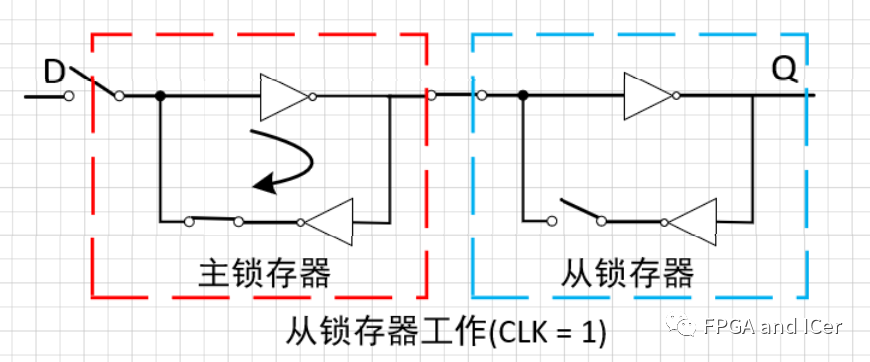

什么是同步逻辑和异步逻辑?同步电路和异步电路的区别在哪?为什么触发器要满足建立时间和保持时间?什么是亚稳态?为什么两级触发器可以防止亚稳态传播?

2021-08-09 06:14:00

让我们从触发器开始,所有触发器都有一个围绕活动时钟沿的建立(setup time)和保持窗口(hold time),在此期间数据不得更改。如果该窗口中的数据实际发生了变化,则触发器的输出将进入不确定

2022-10-18 14:29:13

什么是单稳态触发器?单稳态触发器的工作特点是什么?

2021-04-22 06:09:01

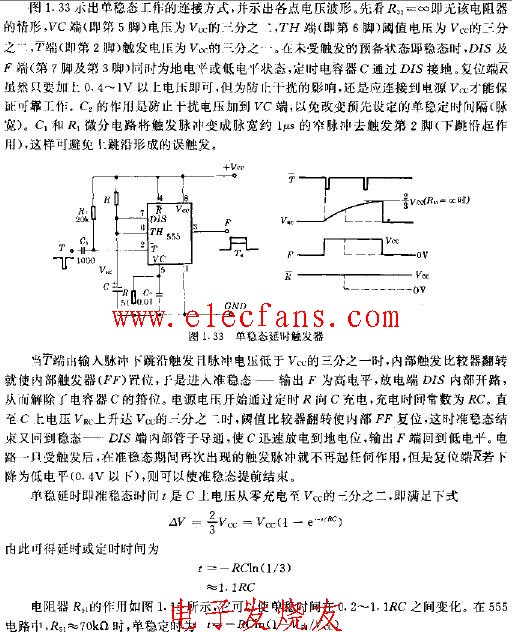

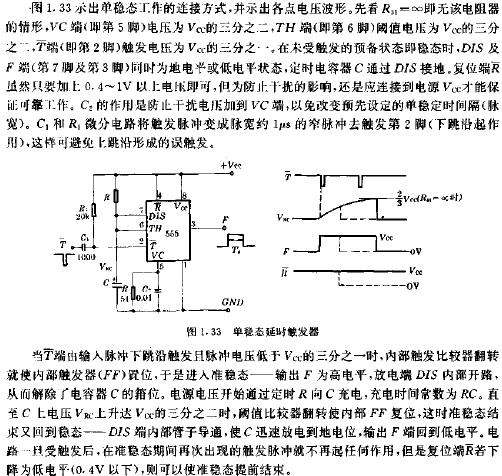

单稳态延时触发器

2019-11-08 09:01:59

,就可能产生亚稳态,此时触发器输出端 Q 在有效时钟沿之后比较长的一段时间处于不确定的状态,在这段时间里 Q 端在 0 和 1 之间处于振荡状态,而不是等于数据输入端 D 的值。这段时间称为决断时间

2020-10-19 10:03:17

数字电路--触发器双稳态触发器

2017-02-05 14:16:51

新建两个D触发器的目的是什么?何谓亚稳态?解决亚稳态的方法是什么?

2021-11-09 07:15:01

单稳态触发器

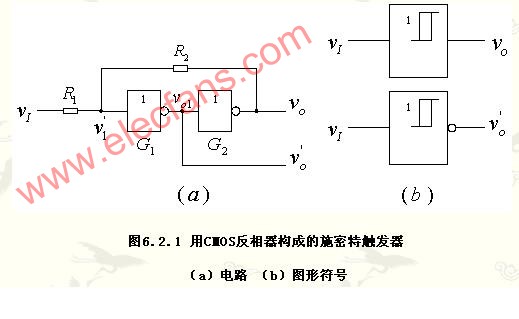

作者:上海

2006-07-03 14:25:13 18465

18465

D触发器真值表分析:

1. D 触发器真值表

Dn

2007-09-11 23:15:20 20330

20330 单稳态延时触发器

2008-05-19 23:05:30 2835

2835

单稳态延时触发器

2008-05-19 23:05:35 1093

1093

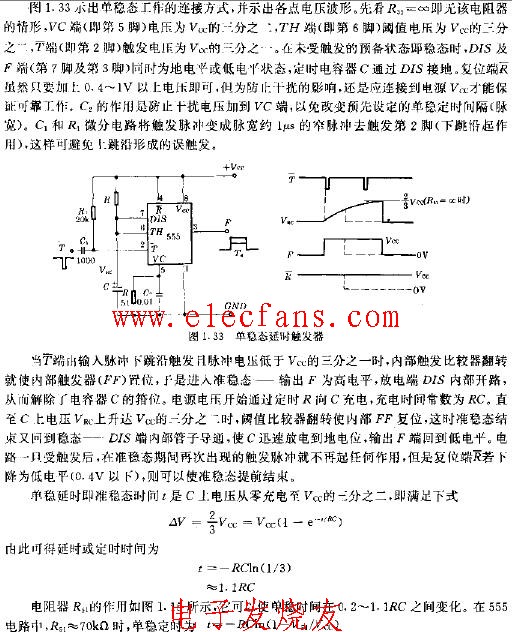

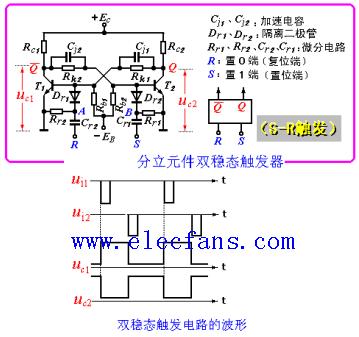

什么是双稳态触发器?

双稳态触发电路实际上也是RS触发器,其ui1端相当于R端,ui2端相当于S端。因此,用门电路组成的

2008-05-26 13:31:40 10798

10798

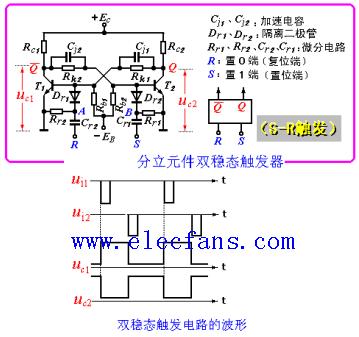

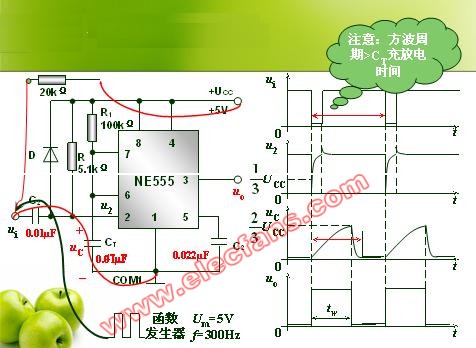

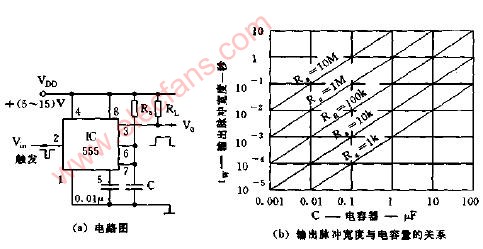

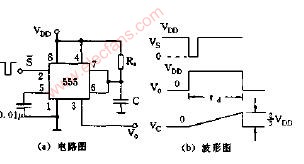

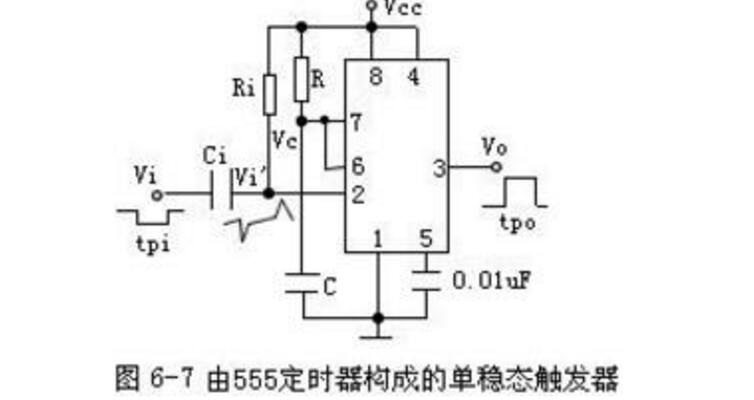

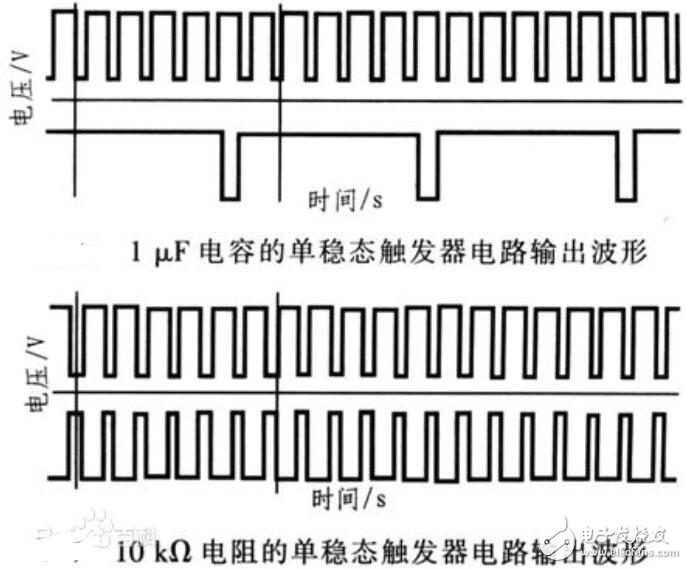

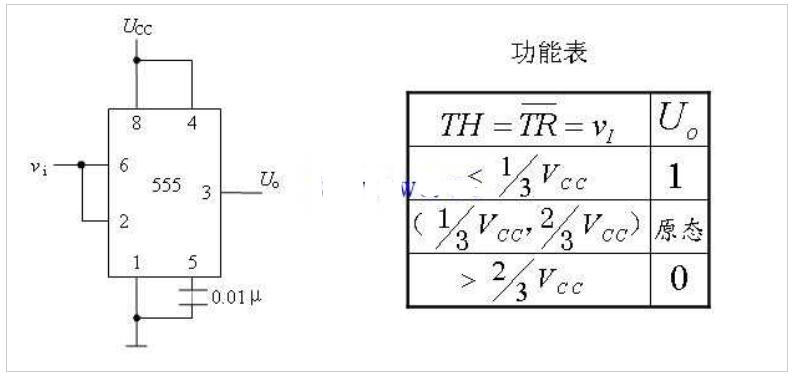

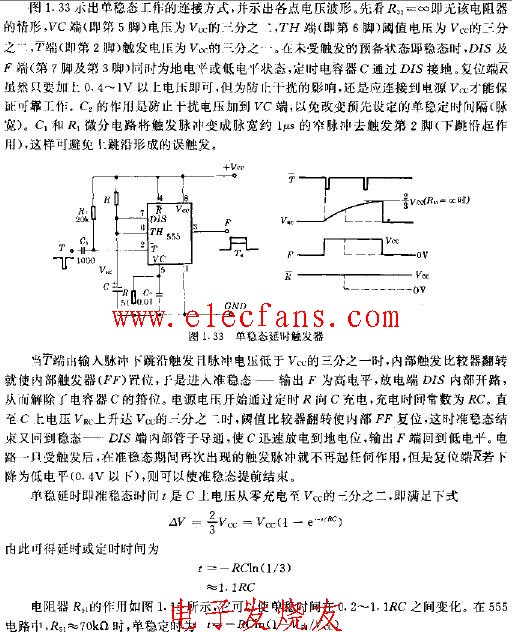

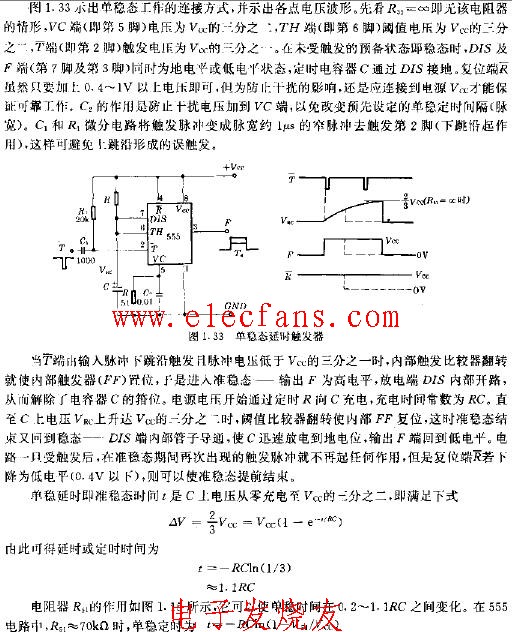

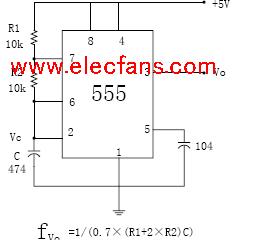

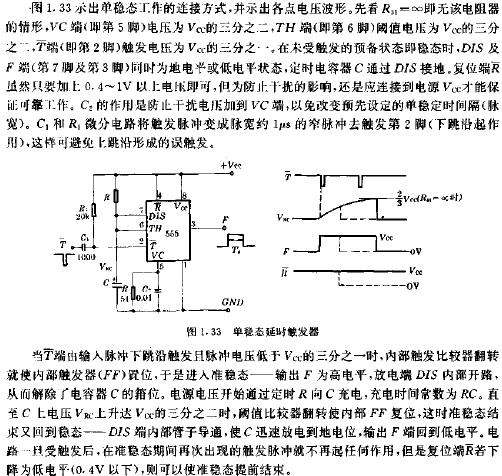

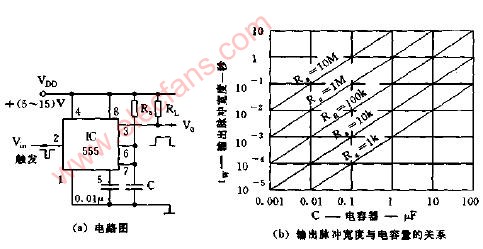

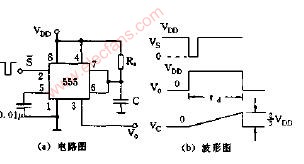

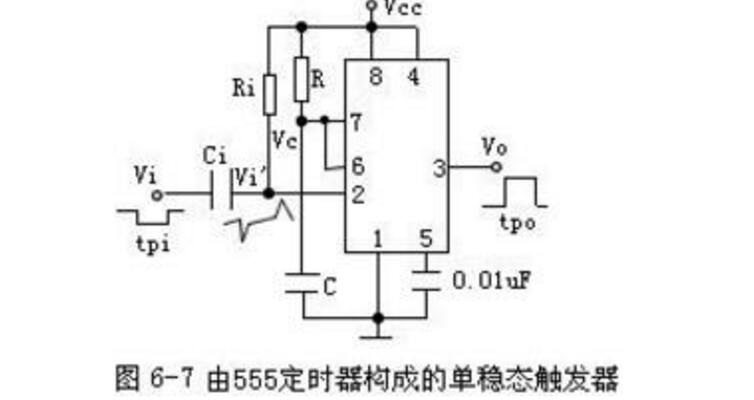

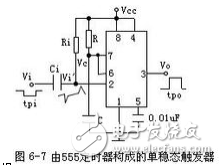

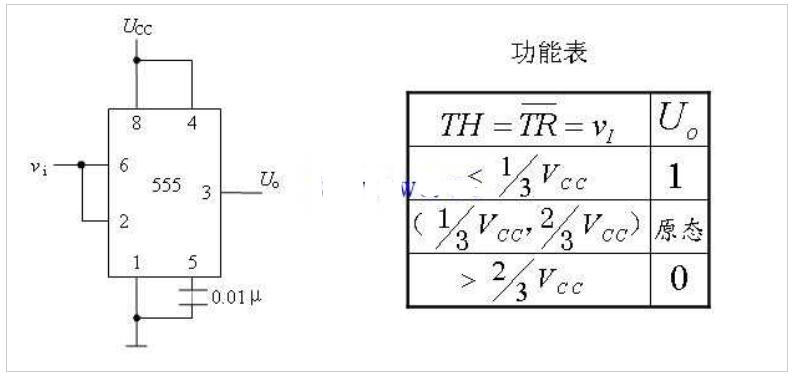

1. 555单稳态触发器

图3.10 单稳态触发器电路图

2008-09-22 11:31:17 3698

3698

D触发器

同步式D触发器逻辑电路图

D触发器功能

2008-10-20 09:57:54 2818

2818

555组成的单稳态触发器

2008-12-17 14:21:08 1189

1189

单稳态延时触发器

2009-04-08 08:49:26 803

803

555单稳态触发器电路图

2009-05-16 16:46:26 1503

1503

555接成单稳态触发器电路图

2009-05-16 16:46:51 1462

1462

单稳态触发器电路图

2009-05-16 16:47:43 976

976

JK触发器工作原理详细介绍

JK触发器,采用与或非电路结构,它的工作原理为:CP为0时,触发器处于一个稳态;CP由0变1时,触发器不

2010-03-08 13:47:58 54681

54681 D触发器,D触发器是什么意思

边沿D 触发器: 电平触发的主从触发器工作时,必须在正跳沿前加入输入信号。如果在CP 高

2010-03-08 13:53:13 5319

5319 图3.27所示的是一个观察D触发器亚稳态的电路图。使用这个电路至少需要一个双通道示波器。

2010-06-08 14:31:27 1490

1490

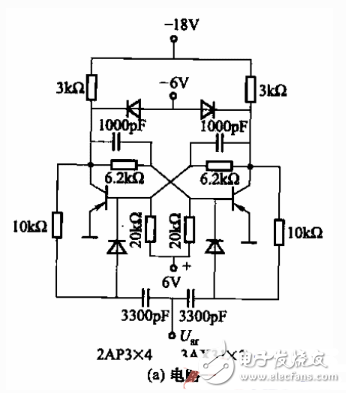

图3.29是一个简化的数字触发器原理图。在这个例子中,为放大器提供了对称的正、负电压。正反馈电路把电

2010-06-08 15:05:44 2058

2058

单稳态触发器仿真电路.ms8

2012-07-16 23:07:20 92

92 数字电路--触发器双稳态触发器

2016-12-20 17:32:40 0

0 单稳态触发器74123资料分享

2022-07-10 10:35:30 20

20 在进行FPGA设计时,往往只关心“0”和“1”两种状态。然而在工程实践中,除了“0”、“1”外还有其他状态,亚稳态就是其中之一。亚稳态是指触发器或锁存器无法在某个规定时间段内达到一个可确认的状态[1]。当一个触发器进入亚稳态时,既无法预测该单元的输出电平,也无法预测何时输出才能稳定在某个正确的电平上。

2019-10-06 09:42:00 1760

1760

亚稳态是指触发器无法在某个规定时间段内达到一个可确认的状态。当一个触发器进入亚稳态时,既无法预测该单元的输出电平,也无法预测何时输出才能稳定在某个正确的电平上。在这个稳定期间,触发器输出一些中间级电平.

2017-12-02 10:40:12 45616

45616

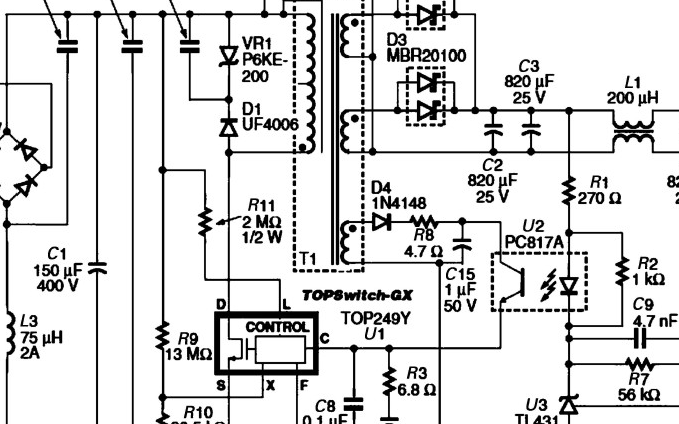

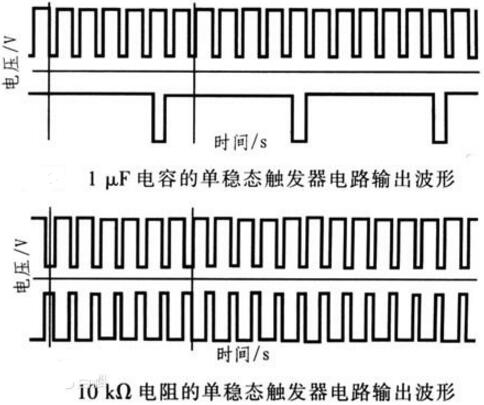

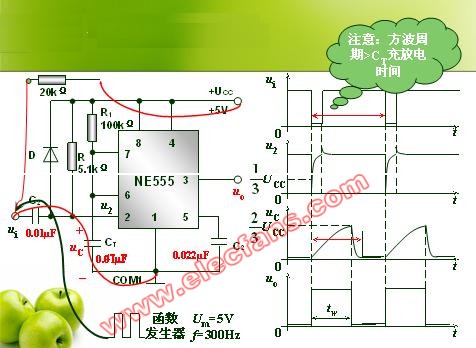

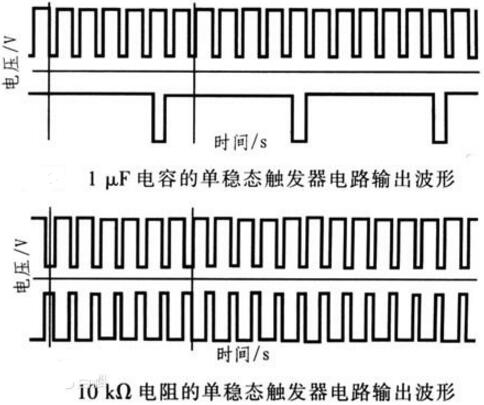

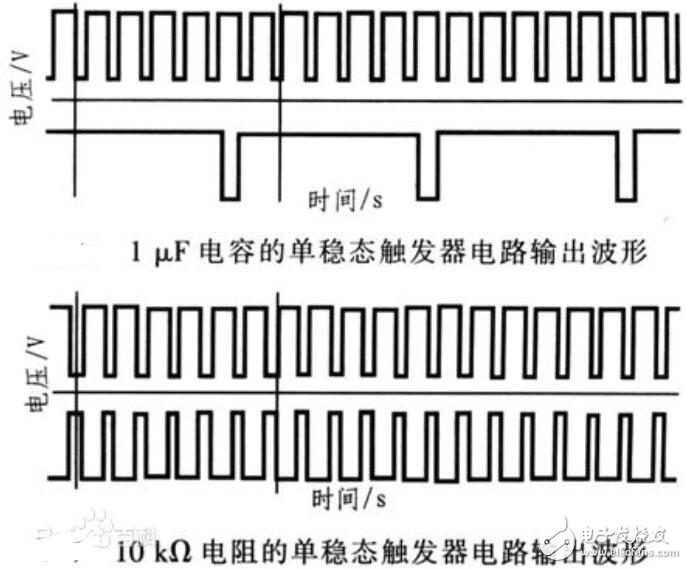

本文开始介绍了什么是单稳态触发器以及单稳态触发器的电路组成,其次阐述了单稳态触发器特点、门电路构成的单稳态触发器、D触发器构成的单稳态触发器,最后详细的阐述了时基电路构成的单稳态触发器。

2018-03-27 09:24:23 78857

78857

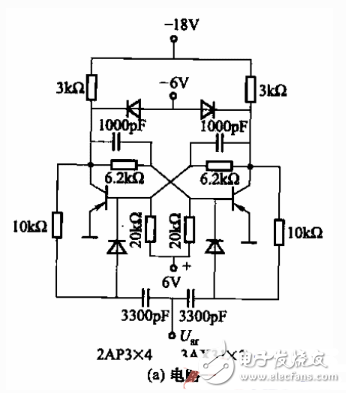

本文主要介绍了双稳态触发器电路图大全(三极管/CD4017/CD4013双D触发器)。双稳态触发器电路具有记忆脉冲信号的功能。它有两个稳定的状态:三极管VTi截止、VTz导通;或VTi导通、VT2

2018-03-27 09:42:00 75588

75588

本文开始介绍了单稳态触发器电路组成和单稳态触发器的四种基本电路图,其次详细阐述了单稳态触发器工作原理,最后介绍了单稳态触发器的作用。

2018-03-27 10:02:25 77290

77290

本文开始介绍了单稳态触发器的概念,其次阐述了单稳态触发器工作特点和单稳态触发器的用途,最后介绍了单稳态触发器的应用。

2018-03-27 10:16:25 33523

33523

本文开始阐述了触发器概念和触发器作用,其次阐述了触发器分类和触发器优点,最后分析了触发器有几个稳态。

2018-03-27 11:18:51 28664

28664 本文开始介绍了触发器的定义和触发器的特点,其次阐述了触发器的分类和触发器的作用,最后介绍了触发器的工作原理。

2018-03-27 17:35:52 22379

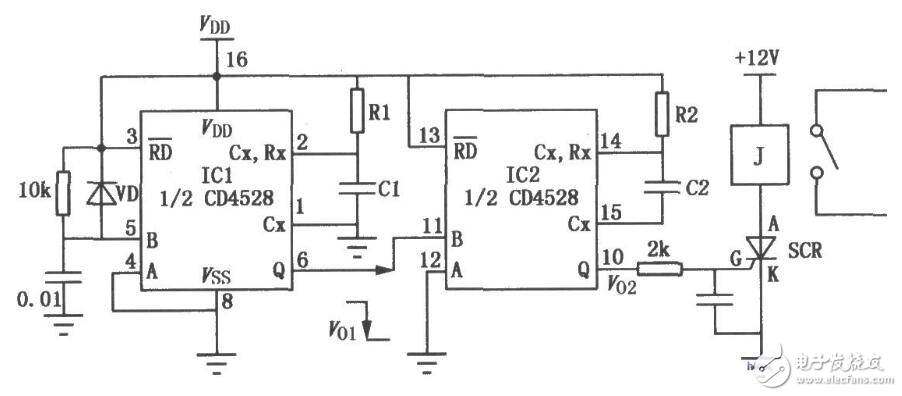

22379 本文开始阐述了单稳态触发器工作特点和单稳态触发器的分类,其次阐述了单稳态触发器工作原理,最后介绍了常用的CD4098单稳态触发器。

2018-03-28 15:41:35 43626

43626

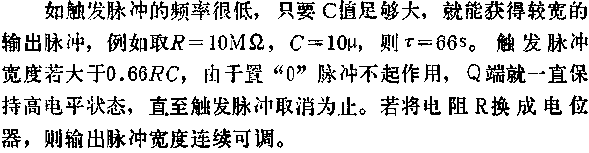

本文主要介绍了单稳态触发器芯片有哪些_单稳态触发器工作原理。单稳态触发器只有一个稳定状态,一个暂稳态。在外加脉冲的作用下,单稳态触发器可以从一个稳定状态翻转到一个暂稳态。由于电路中RC延时环节的作用

2018-03-28 18:22:32 31398

31398

本文主要介绍了双稳态触发器的工作原理详解。双稳态触发器是脉冲和数字电路中常用的基本触发器之一。双稳态触发器的特点是具有两个稳定的状态,并且在外加触发信号的作用下,可以由一种稳定状态转换为另一种稳定

2018-04-04 10:58:47 104654

104654

亚稳态是指触发器无法在某个规定时间段内达到一个可确认的状态。

2018-09-22 08:25:00 10011

10011

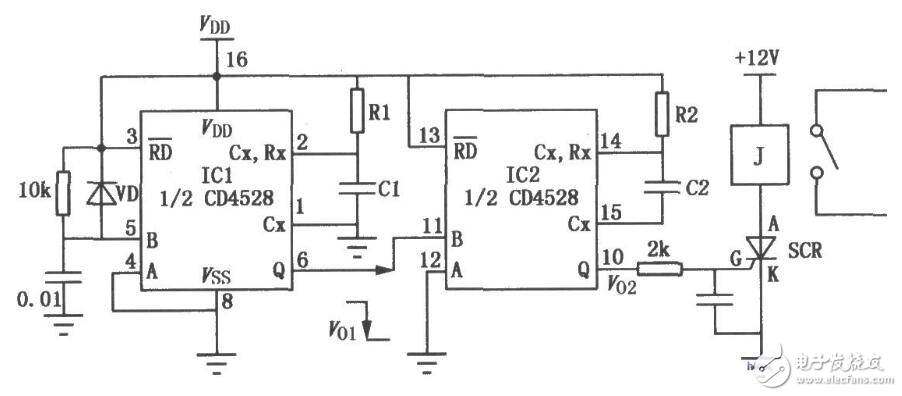

单稳态触发器CD4528组成的延时电路图如下:单稳态触发器电路处于稳态时,由于反相器D2输入端经R接+VDD,其输出端为0,耦合至D1输入端使D1输出端为1,电容C两端电位相等,无压降。

2019-08-05 15:19:31 22223

22223

单稳态触发器只有一个稳定状态,一个暂稳态。在外加脉冲的作用下,单稳态触发器可以从一个稳定状态翻转到一个暂稳态。由于电路中RC延时环节的作用,该暂态维持一段时间又回到原来的稳态,暂稳态维持的时间取决于RC的参数值。

2019-08-05 15:30:37 18165

18165

555守时器构成的单稳态触发器原理图如下:电路构造与作业原理:

2020-09-25 11:23:51 11107

11107

在同步系统中,如果触发器的setup time / hold time不满足,就可能产生亚稳态,此时触发器输出端Q在有效时钟沿之后比较长的一段时间处于不确定的状态,在这段时间里Q端毛刺、振荡、固定的某一电压值,而不是等于数据输入端D的值。

2021-03-09 10:49:23 2037

2037

今天写一下时序问题常见的跨时钟域的亚稳态问题。 先说明一下亚稳态问题: D触发器有个明显的特征就是建立时间(setup time)和保持时间(hold time) 如果输入信号在建立时间和保持时间

2021-06-18 15:28:22 3606

3606 亚稳态的概念 亚稳态是指触发器无法在某个规定时间段内达到一个可确认的状态。当一个触发器进入亚稳态引时,既无法预测该单元的输出电平,也无法预测何时输出才能稳定在某个正确的电平上。在这个稳定期间,触发器

2021-07-23 11:03:11 5493

5493

单稳态触发器只有一个稳定状态,一个暂稳态。在外加脉冲的作用下,单稳态触发器可以从一个稳定状态翻转到一个暂稳态。 单稳态触发器工作原理 微分型单稳态触发器包含阻容元件构成的微分电路。触发器电路

2021-08-12 16:27:26 15330

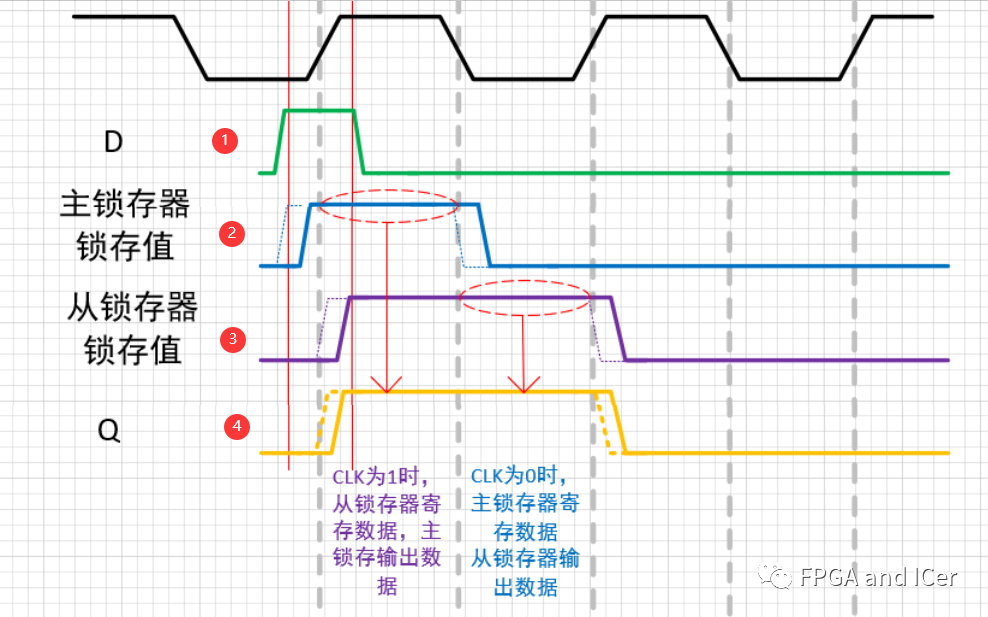

15330 本系列整理数字系统设计的相关知识体系架构,为了方便后续自己查阅与求职准备。对于FPGA和ASIC设计中,D触发器是最常用的器件,也可以说是时序逻辑的核心,本文根据个人的思考历程结合相关书籍内容和网上文章,聊一聊D触发器与亚稳态的那些事。

2023-05-12 16:37:31 2934

2934

亚稳态在电路设计中是常见的属性现象,是指系统处于一种不稳定的状态,虽然不是平衡状态,但可在短时间内保持相对稳定的状态。对工程师来说,亚稳态的存在可以带来独特的性质和应用,如非晶态材料、晶体缺陷等

2023-05-18 11:03:22 6015

6015 本文主要介绍了亚稳态的分析与处理。

2023-06-21 14:38:43 5126

5126

本系列整理数字系统设计的相关知识体系架构,为了方便后续自己查阅与求职准备。对于FPGA和ASIC设计中,D触发器是最常用的器件,也可以说是时序逻辑的核心,本文根据个人的思考历程结合相关书籍内容和网上文章,聊一聊D触发器与亚稳态的那些事。

2023-07-25 10:45:39 2841

2841

亚稳态(Metastability)是由于输入信号违反了触发器的建立时间(Setup time)或保持时间(Hold time)而产生的。建立时间是指在时钟上升沿到来前的一段时间,数据信号就要

2023-09-19 09:27:49 1841

1841

RS触发器是由两个交叉连通的反相器(NOT门)和两个逻辑门组成的,通常是由两个与门(AND门)和一个非门(NOT门)构成。而双稳态触发器(也称为D触发器)是由一对互补输出的锁存器构成,通常是由两个与非门(NAND门)和一个非门(NOT门)构成。

2023-09-26 16:11:50 2683

2683 两级触发器同步,就能消除亚稳态吗? 两级触发器同步可以帮助消除亚稳态。本文将详细解释两级触发器同步原理、亚稳态的定义和产生原因、以及两级触发器同步如何消除亚稳态的机制。 1. 两级触发器同步

2024-01-16 16:29:38 2541

2541 。本文将详细介绍施密特触发器的工作原理、稳态数以及其应用。 施密特触发器的工作原理 施密特触发器是由约瑟夫·斯密特于1938年提出的,它基于正反馈原理,能够将不稳定的输入信号转换为稳定的输出信号。施密特触发器一般由一

2024-02-04 09:53:12 7843

7843 详细介绍单稳态触发器的主要用途、功能和特点。 一、单稳态触发器的主要用途 脉冲宽度调整:单稳态触发器被广泛应用于脉冲调整电路中,可以根据设计要求调整输出脉冲的宽度。例如,在数字系统中,可以利用单稳态触发器生成

2024-02-05 10:54:51 6429

6429 单稳态触发器是一种基本的数字电路元件,具有两个稳态(稳定状态):稳定低电位(低电平)和稳定高电位(高电平)。当输入信号触发器时,触发器会进入暂态(暂态)状态,即从一个稳态过渡到另一个稳态。单稳态

2024-02-06 10:59:23 2972

2972 单稳态触发器是一种能够在某个时间间隔内将输入信号的电平转换为期望的输出信号电平的数字电路。在单稳态触发器中,暂稳态时间是指当触发器的输入信号发生改变时,触发器在从暂稳态过渡到稳态所需的时间。 暂稳态

2024-02-06 11:01:38 3440

3440 单稳态触发器(Monostable Multivibrator)是一种具有两个稳定状态的逻辑电路,其输出在输入触发信号的边沿触发之后会暂时改变,并在一段时间后返回到初始的稳定状态。本文将详细介绍单

2024-02-06 11:16:11 3467

3467 D触发器的稳态 D触发器是数字电路中常用的一种存储元件,它有两种稳态,即低电平稳态和高电平稳态。当输入D为低电平时,输出Q保持为低电平;当输入D为高电平时,输出Q保持为高电平。 D触发器和RS触发器

2024-02-06 11:32:41 5586

5586 稳态是指触发器在某个特定的输入状态下稳定保持输出的状态。根据触发器的类型和触发方式,触发器分为很多种类,不同类型的触发器有不同的稳态。本文将详细描述几种常见的触发器及其稳态,并介绍如何判断触发器

2024-02-06 13:36:55 7912

7912 。D触发器是一种双稳态逻辑器件,它可以在时钟信号的作用下将输入数据存储,并在时钟上升沿或下降沿时将存储的数据传递到输出端。 D触发器的输入端被称为D端,它是一个单一的数据输入端。当时钟信号的相应边沿到来时,D触发器将

2024-02-18 16:28:45 17725

17725 单稳态触发器是一种具有两个稳定状态的触发器,也称为单稳态多谐振荡器(Monostable Multivibrator)或单稳态脉冲发生器(Monostable Pulse Generator)。它

2024-02-21 15:26:26 4199

4199 单稳态触发器(Monostable Multivibrator),也称为单稳态多谐振荡器或单稳态脉冲发生器,是一种具有两个稳定状态的触发器。它的主要特点是,当接收到一个触发信号后,能够从一个稳定状态

2024-07-16 16:33:00 9641

9641

单稳态触发器是一种数字电路,它具有一个稳定状态和一个暂态状态。在单稳态触发器中,当输入信号触发时,触发器从稳定状态转换到暂态状态,然后经过一定的延时后,触发器返回到稳定状态。单稳态触发器广泛应用

2024-08-11 09:39:44 1717

1717 单稳态触发器(Monostable Trigger)是一种数字电路,它可以将输入的脉冲信号转换为一定宽度的输出脉冲。单稳态触发器广泛应用于数字系统中,如定时器、脉冲整形、脉冲计数器等。 一、单稳态

2024-08-11 09:43:39 3921

3921 单稳态触发器可以产生的波形主要是 矩形波波形 。这一结论基于单稳态触发器的工作原理和输出特性。 单稳态触发器(Monostable Multivibrator),也称为单稳态多谐振荡器或单稳态脉冲

2024-08-11 09:45:48 2198

2198 。暂态时间是单稳态触发器的一个重要性能指标,它直接影响到电路的响应速度和稳定性。 本文将从以下几个方面介绍单稳态触发器的暂态时间: 单稳态触发器的工作原理 单稳态触发器是一种具有两个稳定状态的数字逻辑电路,其中一

2024-08-11 09:50:33 2125

2125 单稳态触发器(Monostable Trigger)是一种数字电路,它在接收到一个触发信号后,能够保持输出状态一段时间,然后自动返回到初始状态。单稳态触发器广泛应用于定时控制、脉冲延迟、脉冲整形等

2024-08-11 09:52:50 2208

2208 双稳态触发器(Bistable Trigger)是一种具有两个稳定状态的数字逻辑电路,广泛应用于数字系统中的存储、计数、时序控制等领域。 一、双稳态触发器的基本特征 双稳态特性:双稳态触发器具有两个

2024-08-11 09:56:13 1547

1547 双稳态触发器(Bistable Trigger)是一种具有两个稳定状态的逻辑电路,广泛应用于数字电路设计中。 双稳态触发器的基本概念 双稳态触发器,又称为双稳态电路或双稳态逻辑门,是一种具有两个稳定

2024-08-11 09:59:08 2238

2238 双稳态触发器(Bistable Trigger or Flip-Flop)是一种具有两个稳定状态的数字电路元件,广泛应用于数字逻辑电路、存储器和时序电路中。 一、双稳态触发器的基本概念 1.1 定义

2024-08-11 10:00:52 5546

5546 双稳态触发器(Bistable Trigger)是一种具有两个稳定状态的逻辑电路,广泛应用于数字电路设计中。它具有两个基本性质:记忆性和切换性。 一、双稳态触发器的基本概念 1.1 双稳态触发器

2024-08-11 10:08:05 1848

1848 双稳态触发器(Bistable Trigger)是一种具有两个稳定状态的触发器,广泛应用于数字电路和电子系统中。 一、双稳态触发器的特点 稳定性:双稳态触发器具有两个稳定的输出状态,即高电平和低电平

2024-08-11 10:10:54 1749

1749 双稳态触发器是一种具有两个稳定状态的数字逻辑电路,它可以在两个状态之间切换,并且能够在没有外部输入信号的情况下保持当前状态。双稳态触发器广泛应用于数字电子系统中,如存储器、计数器、寄存器等。 耦合

2024-08-11 10:15:34 1876

1876 双稳态触发器(Bistable Trigger)是一种具有两个稳定状态的电路,通常用于存储一位二进制信息。在数字电路中,双稳态触发器是一种非常重要的基本组件,广泛应用于寄存器、计数器、存储器等数字

2024-08-11 10:18:22 3919

3919 双稳态触发器(Bistable Trigger)是一种具有两个稳定状态的电子电路,广泛应用于数字电路设计中。 双稳态触发器的工作原理 双稳态触发器是一种具有两个稳定状态的电路,即“0”状态和“1

2024-08-11 10:21:00 1901

1901 双稳态触发器的使用方法主要包括以下几个方面: 一、安装与连接 安装 :双稳态触发器通常是以集成电路的形式存在,可以通过焊接或插入到电路板上。在安装过程中,需要注意正确的引脚连接和电路布局,以确保

2024-08-11 10:23:20 1410

1410 触发器稳态的判断是数字电路设计中的一个重要环节,它涉及到触发器在不同输入条件下的输出状态稳定性。

2024-08-12 10:27:51 1703

1703 单稳态触发器(Monostable Multivibrator)是一种具有两个稳定状态的逻辑电路,但与其他触发器(如JK触发器、D触发器等)不同,单稳态触发器在输入触发信号的边沿触发之后,会从一个稳定状态暂时翻转到一个暂稳态,并在一段时间后自动返回到初始的稳定状态。

2024-08-12 11:24:54 3892

3892 单稳态触发器(Monostable Multivibrator),也称为单稳态多谐振荡器或单稳态脉冲发生器,是一种重要的数字电路元件。它能够在接收到一个触发信号后,从一个稳定状态翻转到一个暂稳态,并保持该状态一定时间后自动返回原稳定状态。这种特性使得单稳态触发器在多种场景中有着广泛的应用。

2024-08-12 11:25:20 2657

2657 单稳态触发器,也称为单稳态多谐振荡器或单稳态脉冲发生器,是一种常用的数字电子元件。关于其稳态状态,存在不同的表述方式,但核心意义是一致的。以下是单稳态触发器稳态状态的介绍: 单稳态触发器的稳态状态

2024-08-22 10:09:26 1616

1616 单稳态触发器是一种数字逻辑电路,广泛应用于各种电子设备和系统中。它具有两个工作状态:稳定状态和暂态状态。 单稳态触发器的工作原理 单稳态触发器是一种具有两个稳定状态的触发器,其中一个状态是稳定状态

2024-08-22 10:11:26 1607

1607 双稳态触发器(Bistable Trigger)是一种具有两个稳定状态的数字电路,常用于存储一位二进制信息。它在数字电路设计中具有重要应用,如存储器、计数器、寄存器等。 一、双稳态触发器的类型

2024-08-22 10:12:52 1831

1831 边沿式D触发器是一种 双稳态电路 。 双稳态电路是指具有两个稳定状态的电路,即触发器有两个稳态,可分别表示二进制数码0和1,无触发信号作用时,电路将维持原状态不变,触发器处于稳定状态。边沿式D触发器

2024-08-22 10:15:40 2377

2377 ,可以存储一位二进制信息。触发器的输出状态取决于输入信号和触发器的当前状态。触发器的分类主要有D触发器、JK触发器、T触发器等。 D触发器 D触发器是一种常见的触发器类型,其名称来源于其数据输入端(Data input)的缩写。D触发器具

2024-08-22 10:37:33 5059

5059 可以分为多种类型,如SR触发器、JK触发器、D触发器等。其中,JK触发器因其具有两个稳态的特性,被广泛应用于数字电路设计中。 JK触发器的基本概念 2.1 触发器的定义 触发器是一种具有记忆功能的数字逻辑电路,可以存储一位二进制信息。

2024-08-22 10:39:18 2766

2766

电子发烧友App

电子发烧友App

评论