本文主要介绍的是FPGA的片上资源使用情况,分别是从组合逻辑及时序逻辑来详细的分析。

2018-04-18 09:06:24 18789

18789

Allegro中如何进行颜色设置

在ALLEGRO中,如何对网络设置颜色?比如对POWER网络,我想让它显示为红颜色!怎么做?RichardLC网友回复:我想你

2008-03-22 16:40:44 11885

11885

在FPGA设计中经常使用到逻辑复制,逻辑复制也用在很多场合。

2022-09-29 09:17:53 1256

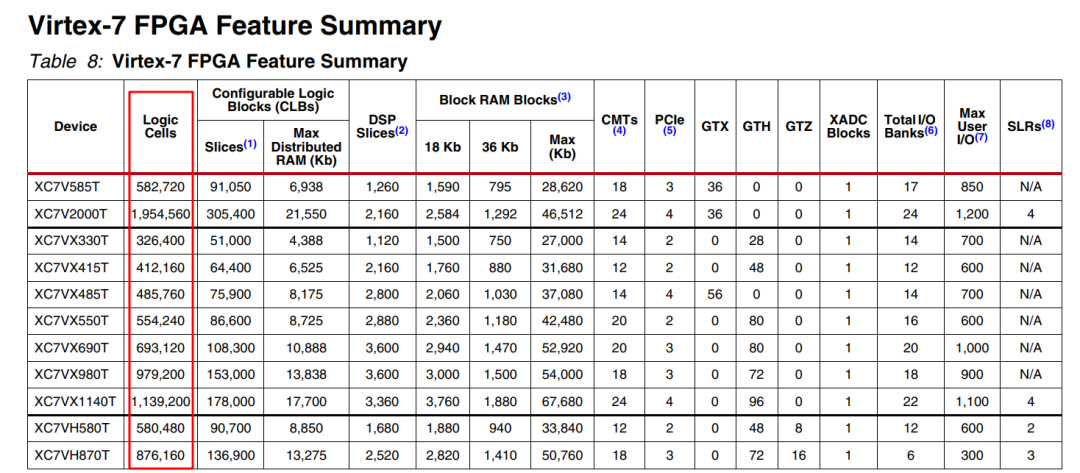

1256 输入输出端口 从Implemented Design中可以看到FPGA中资源大致分布如下。中间蓝色是CLB可编程逻辑块、DSP或BRAM,两侧的彩色矩形块是I/O接口和收发器,划分的方块是不同的时钟域 Configurable Logic Block (CLB)可编程逻

2022-12-27 15:54:52 3346

3346 把基本逻辑运算的电子电路称之为逻辑门电路。在数字电路关系应用中,逻辑门电路中的门代表着基本逻辑关系的电路。

2024-02-04 14:58:13 5712

5712

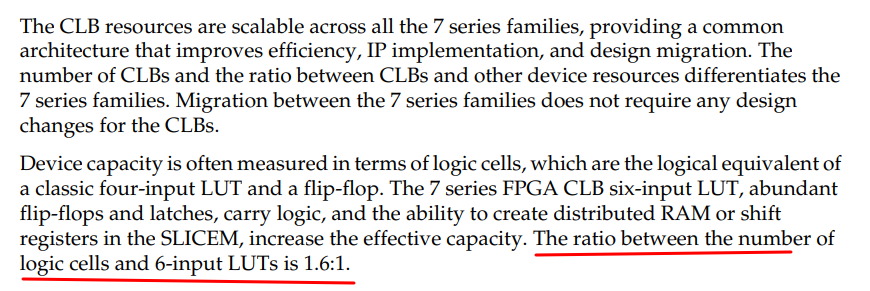

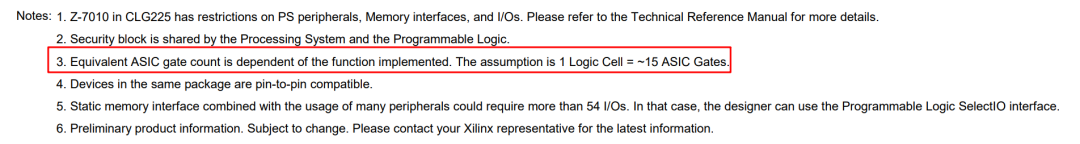

数据。 对于第一种方法,FPGA 包括LUT/FF/RAM 等资源,分析各种资源等效门数时,总原则是等效原则,就是实现相同的功能,在标准门阵列中需要的门数就是FPGA 该资源等效门数,例如实现一个带

2012-08-11 10:29:07

FPGA 如何进行浮点运算

2015-09-26 09:31:37

时,总原则是等效原则,就是实现相同的功能,在标准门阵列中需要的门数就是FPGA 该资源等效门数,例如实现一个带寄存器输出的4 输入XOR,在FPGA 中需要用一个LUT 和1 个FF 实现,在标准门阵列

2012-03-01 10:08:53

在Quartus中怎样在工具在设置使得代码可以被映射到FPGA上的指定区域?在书上看到要进行位置约束,不知怎么弄!本人刚接触这个,求大神解答

2017-06-10 22:25:21

FPGA中组合逻辑门占用资源过多怎么降低呢?有什么方法吗?

2023-04-23 14:31:17

)是两种不同的硬件实现方式。

FPGA是一种可编程逻辑器件,其内部资源可以根据需要进行配置和重新配置。这些资源包括但不限于:

逻辑单元(Logic Cells):这些是FPGA的核心计算资源,可以实现各种

2024-02-22 09:52:22

FPGA中等效逻辑门概念数的计算方法有两种,一是把FPGA基本单元(如LUT+FF,ESB/BRAM)和实现相同功能的标准门阵列比较,门阵列中包含的门数即为该FPGA基本单元的等效门数,然后乘以

2012-08-10 14:05:35

FPGA小白一枚,个人理解的FPGA本质上或者核心就是查找表(LUT),即将所有的函数/方法 转换为固定的查找表(使用DSP除外)。但是为什么所有的文章提到FPGA全部都注重逻辑门呢?其实FPGA本身内部也没有多少物理的逻辑门吧?

2019-05-30 10:53:46

设置其工作状态的。这些存储单元被称为配置存储单元(CMUs),用于存储逻辑门和内部互连网络的配置信息。

当FPGA开始工作时,它首先从外部源(如EPROM)中读取配置数据,然后将这些数据加载到内部的配置

2024-04-29 23:26:51

FPGA的学习。

在学习中才发现,FPGA远不是门电路那么简单。FPGA中有各种需要的资源,比如门电路、存储单元、片内RAM、嵌入式乘法器、PLL、IO引脚等。等于是说,可以根据需求,把需要的资源都放到芯片中,通过设置整合起来使用。这与单片机有些类似了。

2024-05-22 18:27:24

逻辑复制与资源共享本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt 逻辑复制是一种通过增加面积来改善时序条件

2015-07-05 19:54:33

在线调试方式大都是通过FPGA器件引出的JTAG接口,同时使用了一些FPGA片内固有的逻辑、存储器或布线资源就能够实现的。这些调试功能通常也只需要随着用户设计所生产的配置文件一同下载到目标FPGA器件中

2015-09-02 18:39:49

与CPLD不同,FPGA是基于门阵列方式为用户提供可编程资源的,其内部逻辑结构的形成是由配置数据决定的。那么是如何进行配置的呢?配置的模式又有那些?

2024-06-19 14:40:43

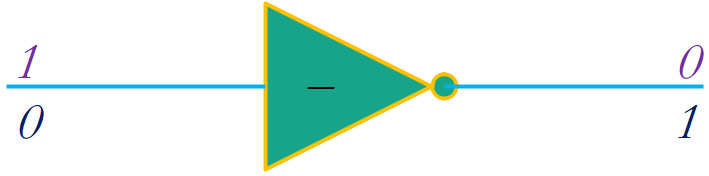

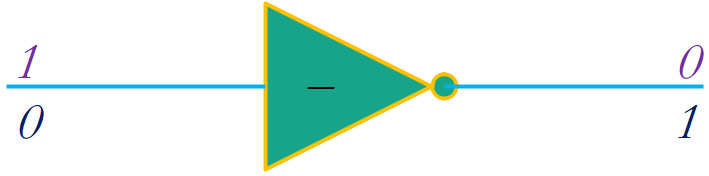

和坏,或者电路的通和断、电灯的亮和暗、门的开和关等等。这种只有两种对立逻辑状态的逻辑关系成为二值逻辑。当使用两个数码表示逻辑状态时,它们之间可以按照指定的某种因果关系进行推理计算,将这种运算称为逻辑

2023-02-20 17:24:56

时序电路)。 在组合逻辑电路中,任何时刻的输出仅仅取决于该时刻的输入,与电路原来的状态无关。这就是组合逻辑电路在逻辑功能上的共同特点。在上一节中,设计的三人表决器就是组合逻辑电路,输出与输入一一对应,和其他

2023-02-21 15:35:38

;"小于"这样的判断语句, 这样会明显增加使用的逻辑单元数量 .看一下报告,资源使用差别很大.例程:always@(posedge clk)begincount1=count1+1

2018-03-24 11:04:41

组合逻辑:基本逻辑门Wirewire线型的基本描述已在笔记整理(1)中给出了。题目:实现输入与输出的连接。答案:module top_module ( input in, output out

2021-09-08 07:32:26

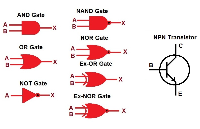

逻辑门及组合逻辑电路实验实验目的1. 掌握与非门、或非门、与或非门及异或门的逻辑功能。2. 了解三态门的逻辑功能以及禁止状态的判别方法。了解三态门的应用。3. 掌握组合逻辑电路的设计和实现方法。4.

2008-09-25 17:28:34

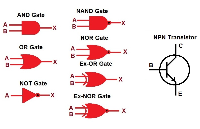

我们还看到,每个门分别具有与非门,或非门和缓冲器形式的相反或互补形式,并且这些门中的任何一个都可以连接在一起以形成更复杂的组合逻辑电路。我们还看到,在数字电子产品中,“与非”门和“或非”门都可以被

2021-01-27 08:00:00

USB OTG的工作原理是什么?IP设计原理是什么?如何进行IP模块设计?USB OTG IP核有什么特性?如何对USB OTG IP核进行FPGA验证?

2021-04-27 06:44:33

TTL逻辑门与普通逻辑门的区别在哪里为什么引入OC门?

2021-03-29 07:23:21

够大;从确保足够的驱动电流考虑应当足够小.2、线与逻辑,即两个输出端(包括两个以上)直接互连就可以实现“AND”的逻辑功能.在总线传输等实际应用中需要多个门 的输出端并联连接使用,而一般TTL门输出端

2016-08-23 21:39:46

FPGA的逻辑电路基础知识四、逻辑值 逻辑0:表示低电平,对应GND。 逻辑1:表示高电平,对应VCC。 逻辑X:表示未知,可能高电平,可能低电平。 逻辑Z:表示高阻态,外部没有激励信号,悬空状态

2019-12-10 20:32:03

我用fpga生成的两路分辨率很高的脉冲,想在fpga外进行逻辑与。对与门参数有什么要求吗。比如上升沿下降沿的识别能力或者带宽等等

2019-05-13 10:57:47

逻辑门是数字电路的基础。各种多姿多彩的逻辑门组合在一起,形成了数字电路的大千世界。实际上,逻辑门反映的是逻辑代数的几种基本运算,只要你能够实现这样的逻辑代数规则,你就能够用其他设备来实现逻辑门的功能,看!

2019-07-23 07:03:30

的。话不多说,上货。 在FPGA中何时用组合逻辑或时序逻辑 在设计FPGA时,大多数采用Verilog HDL或者VHDL语言进行设计(本文重点以verilog来做介绍)。设计的电路都是利用

2023-03-06 16:31:59

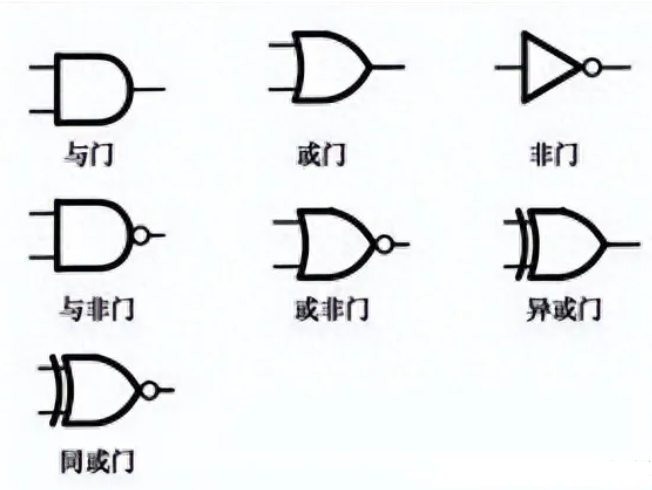

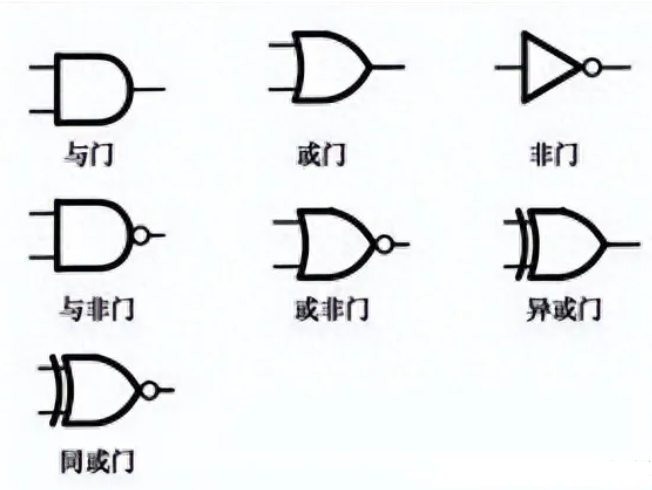

1、集成逻辑门及其基本应用介绍本实验涉及到的基本逻辑门有“与门”、“与非门”、“或门”、“或非门”、“异或门”和“同或门”,功能简单,实验时使用2个拨动开关模拟逻辑门的输入信号,通过LED灯的点亮或

2022-07-01 15:18:51

本文使用符合PCI电气特性的FPGA芯片进行简化的PCI接口逻辑设计,实现了33MHz、32位数据宽度的PCI从设备模块的接口功能,节约了系统的逻辑资源,且可以将其它用户逻辑集成在同一块芯片,降低了成本,增加了设计的灵活性。

2021-05-08 08:11:59

逻辑结构之上运行的高速公路网络一样,为FPGA外部高速接口和内部可编程逻辑的数据传输提供了大约高达27Tbps的超高带宽。作为Speedster7t FPGA器件中的重要创新之一,2D NoC为FPGA

2020-10-20 09:54:00

你好。我是在FPGA上设计系统的初学者。我的fpga是XC7K325T -2 FFG900(knitex - 7系列)我想计算基本15位2输入加法器的逻辑延迟。如果我能检查AND门或OR门的延迟等

2020-05-25 07:28:24

(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。 本文主要介绍的是FPGA的片上资源使用情况,分别是从组合逻辑及时序逻辑来详细的分析

2019-06-17 09:03:28

2GHz)的传输速率运行。NoC为FPGA设计提供了几项重要优势,包括:提高设计的性能。减少逻辑资源闲置,在高资源占用设计中降低布局布线拥塞的风险。减小功耗。简化逻辑设计,由NoC去替代传统的逻辑去做高速

2020-05-12 08:00:00

与否。 4.问题与思考实验中以与门作为例子进行设计,你如何经过简单改动,按照同样的方式来设计或门,非门和以或门并进行仿真验证?逻辑门运算符Verilog算法代码与门&assign y

2015-04-03 11:18:25

现在我需要一个逻辑门器件,与门和或门。要求是在输入时间为100ns的脉冲信号(可调),两个输入,一个输出。然后通过这个逻辑门器件之后可以用示波器检测到。。。新人也不懂 啊,需要什么型号的器件呢?

2018-09-17 16:01:36

套件这个学习工具包将允许用户了解逻辑门是如何工作的,这对初学者来说非常有用。该套件已打开所有逻辑门,并允许用户使用不同的逻辑门进行实验。图 1 是该套件的示意图。(对不起,原理图做得不好)图 1 - 示意图 图 2 是可以制造的 PCB 的图片。图 2 - PCBPCB

2022-09-08 07:42:05

列出4中能做非门的逻辑门(非门除外)

2010-04-29 18:54:58

异成门逻辑符号图/同或门逻辑符号图

2019-10-23 03:49:43

和灵活性,可实时完成运动控制过程中复杂的逻辑处理和控制算法,能实现多轴高速高精度的伺服控制。本文选用DSP与FPGA作为运动控制器的核心部件,设计了通用型运动控制器。其中DSP用于运动轨迹规划、速度控制

2019-07-31 08:15:26

钟控传输门绝热逻辑电路和SRAM 的设计本文利用NMOS管的自举效应设计了一种新的采用二相无交叠功率时钟的绝热逻辑电路---钟控传输门绝热逻辑电路,实现对输出负载全绝热方式充放电.依此进一步设计了

2009-08-08 09:48:05

本文针对磁通门信号采集与处理的具体特点,对基于FPGA的磁通门数字信号处理系统进行了研究。该系统采用A/D转换器对磁通门输出信号进行采样,采样后的数据通过FPGA进行数据

2009-12-23 15:09:09 15

15 1. 把FPGA 基本单元(如LUT+FF,ESB/BRAM)和实现相同功能的标准门阵列比较,门阵列中包含的门数即为该FPGA 基本单元的等效门数,然后乘以基本单元的数目就可以得到FPGA 门数

2010-07-19 16:49:20 22

22 本文针对磁通门信号采集与处理的具体特点,对基于FPGA的磁通门数字信号处理系统进行了研究。该系统采用A/D转换器对磁通门输出信号进行采样,采样后的数据通过FPGA进行数据处理,再

2010-07-21 17:24:58 26

26 异成门和同或门的逻辑符号图:

2009-04-06 23:30:10 4821

4821

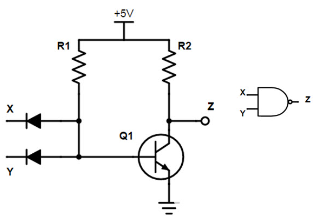

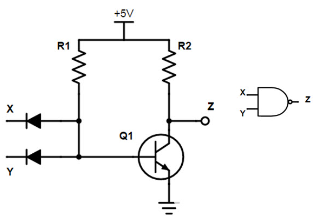

逻辑门是逻辑电路的基本组成部分,可以由晶体管来构成,逻辑门大致可以分为基本门、万用门和延伸门等三种,其中基本门又可以分为与门、或门和非门三种。逻辑门可以使信号的高低电平转化为响应的逻辑信号,从而实现逻辑运算

2017-05-22 14:16:38 61883

61883

众所周知FPGA的硬件资源被划分为若干个不同的bank,Xilinx一些高端的FPGA器件由22个甚至更多个bank组成,这样设计主要是为了提高灵活性。FPGA的I/O支持1.8V、2.5V

2018-06-30 16:29:00 4602

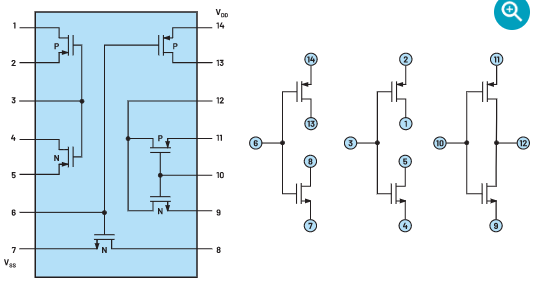

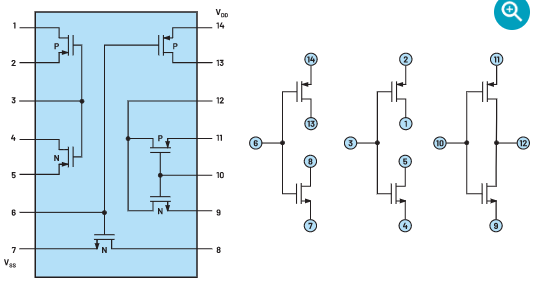

4602 PLD可以是低逻辑密度器件,采用被称为复杂可编程逻辑器件(CPLD)的非易失元件构建;也可以是高密度器件,基于现场可编程门阵列(FPGA)的SRAM查找表(LUT)搭建。在可配置逻辑阵列中,除了

2017-09-12 17:08:30 14

14 逻辑门是数字电路的基础。各种多姿多彩的逻辑门组合在一起,形成了数字电路的大千世界。实际上,逻辑门反映的是逻辑代数的几种基本运算,只要你能够实现这样的逻辑代数规则,你就能够用其他设备来实现逻辑门的功能。

2017-09-19 14:19:18 23

23 随着现场可编程门阵列( FPGA)芯片在商业、军事、航空航天等领域越来越广泛的应用,其可靠性和可测试性也显得尤为重要。本文介绍一种基于SRAM结构FPGA逻辑资源的测试编程方法,并以Xilinx公司的XC4000系列为例,在BC3192V50数模混合集成电路测试系统上,通过从串模式,实现数据的配置和测试。

2017-11-23 14:48:02 5903

5903 布线资源连通FPGA内部的所有单元,而连线的长度和工艺决定着信号在连线上的驱动能力和传输速度。FPGA芯片内部有着丰富的布线资源,根据工艺、长度、宽度和分布位置的不同而划分为4类不同的类别。第一类

2017-12-05 11:48:44 8

8 /A、A/D芯片取代,有利于系统温度稳定性的提到。FPGA内的数字逻辑实现了磁通门信号解算、激励正弦信号发生、D/A、A/D输入/输出串并转换的功能,首先用硬件描述语言(HDL)设计并仿真,然后下载、配置到FPGA中,调试完成后进行实验,通过实时

2018-01-19 22:24:56 2185

2185 现在的FPGA里面有很多存储资源,DSP(数字信号处理)资源,布线通道,I/O资源,当然最根本的还是CLB(Configurable Logic Block)。Xilinx的资源分布采用ASMBL架构。

2018-10-22 11:00:43 6302

6302 本文档的主要内容详细介绍的是数据库概念结构和逻辑结构与物理结构如何进行设计的详细资料免费下载

2018-10-23 16:42:37 17

17 本文档的主要内容详细介绍的是单片机教程之如何进行单片机内部资源的C51编程详细资料免费下载

2018-11-30 18:02:52 21

21 在使用FPGA过程中,通常需要对资源做出评估,下面简单谈谈如何评估FPGA的资源。

2019-02-15 15:09:05 4334

4334 逻辑或门控栅极是数字逻辑“或”门与串联连接在一起的反相器或非门的组合,包含NOR(非或)门的输出为当输入的ANY处于逻辑电平“1”时,它通常处于逻辑电平“1”并且仅“低”到逻辑电平“0”。逻辑NOR门是我们之前看到的包含OR门的反向或“互补”形式。

2019-06-26 14:13:52 35985

35985

数字逻辑门是一种电子电路,它根据输入上存在的数字信号的组合做出逻辑决策.

2019-06-22 08:51:00 15029

15029 在ASIC的世界里,衡量器件容量的常用标准是等效门。这是因为不同的厂商在单元库里提供了不同的功能模块,而每个功能模块的实现都要求不同数量的晶体管。这样在两个器件之间比较容量和复杂度就很困难。

2019-08-21 17:55:27 3736

3736 在数字电路中,所谓“门”就是只能实现基本逻辑关系的电路。最基本的逻辑关系是与、或、非,最基本的逻辑门是与门、或门和非门。逻辑门可以用电阻、电容、二极管、三极管等分立原件构成,成为分立元件门。也可以将门电路的所有器件及连接导线制作在同一块半导体基片上,构成集成逻辑门电路。

2019-11-05 11:28:23 22565

22565

本文档的主要内容详细介绍的是数组中变量取值范围如何进行纠正。

2019-12-17 17:08:16 4

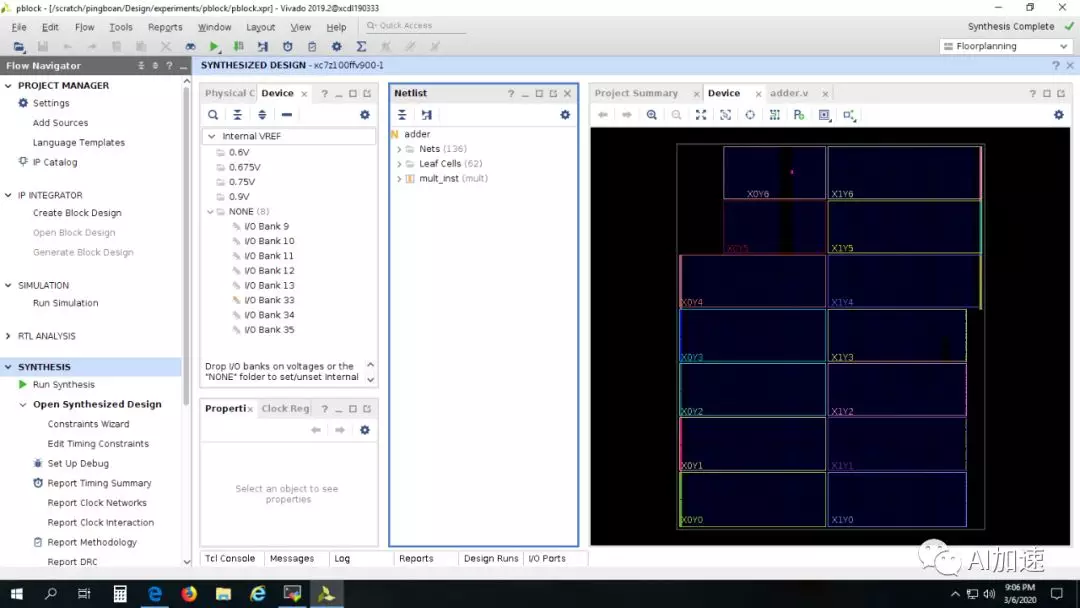

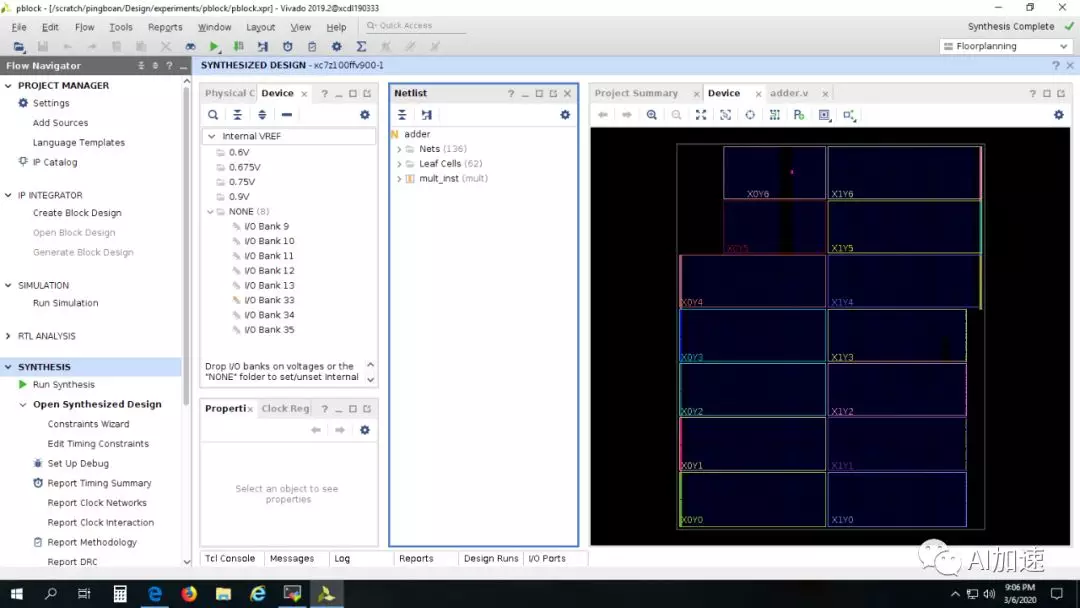

4 的位置限定了逻辑单元在FPGA中的位置。通常一个pblock大小不要超过总设计资源的20%。如果pblock占比资源很大,就要将一个pblock划分给更底层的逻辑。 打开综合后的设计,我们切换到floorplanning选项,这个时候我们可以看到综合后的模块以及device视图。 从netlist中可以看到有两个

2020-10-10 16:03:18 9661

9661

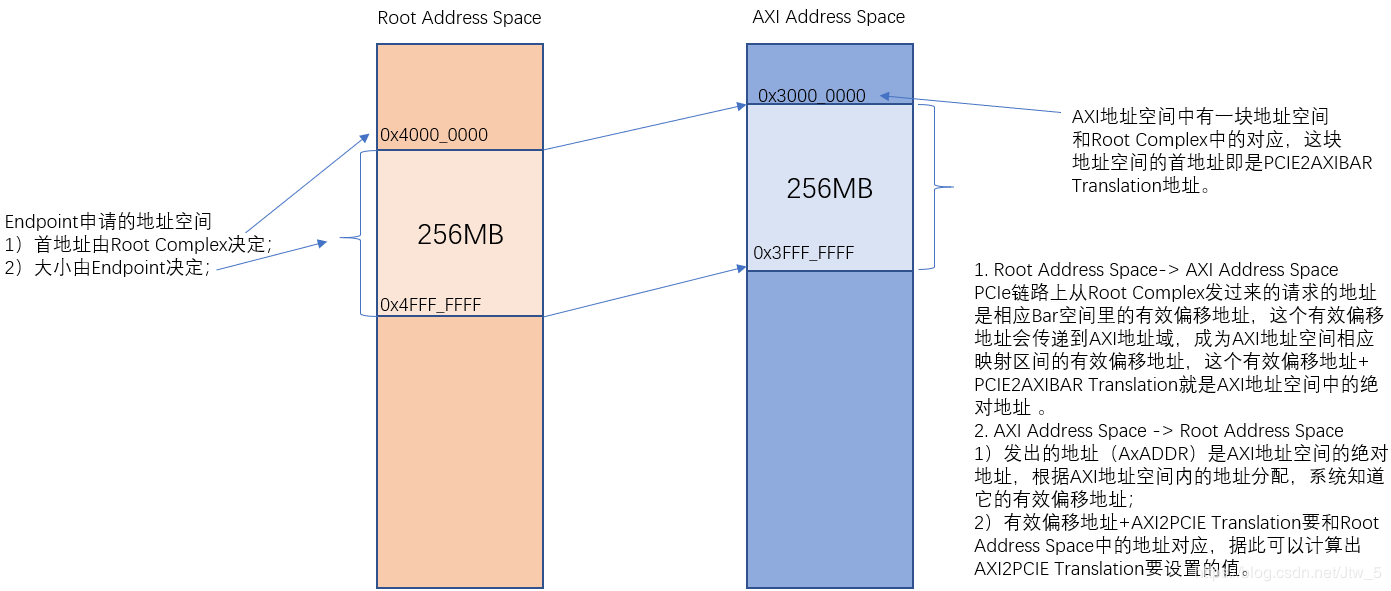

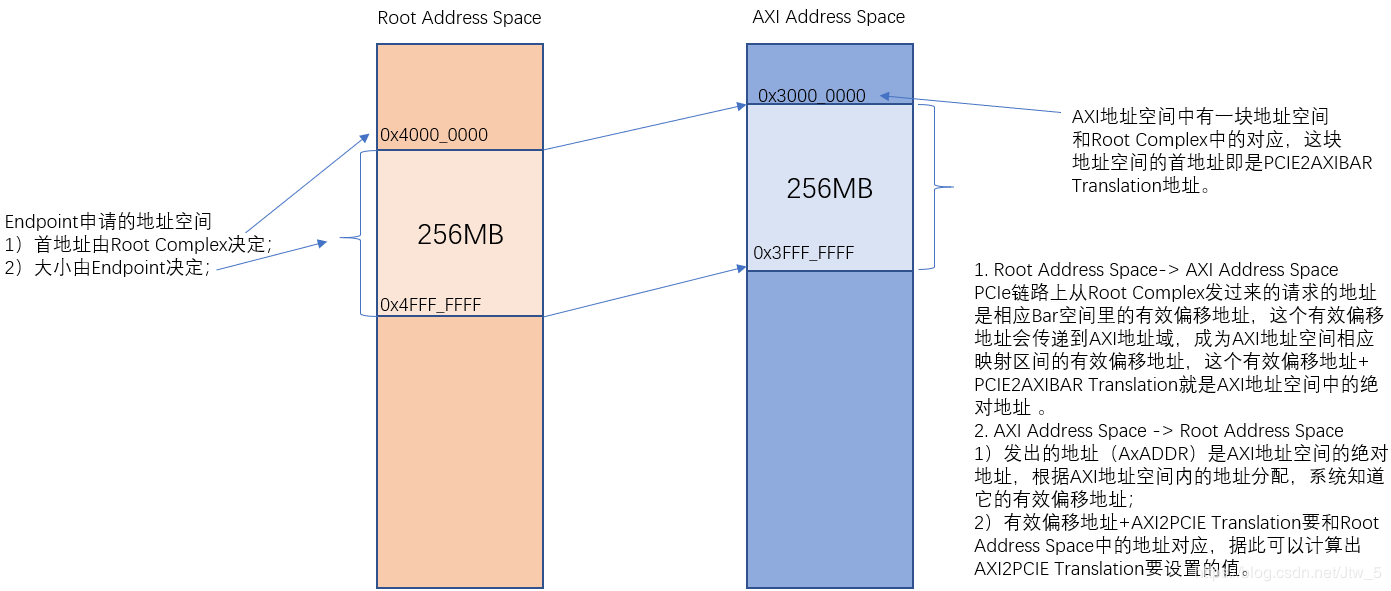

背景与问题 CPU+FPGA架构,CPU做RC、FPGA做EP; FPGA逻辑(Vivado -BD - Address Editor)中如何设置PCIe to AXI Translation

2020-11-20 15:28:52 8159

8159

的 的RAM。 当用户通过原理图或HDL语言描述了一个逻辑电路以后,FPGA开发软件会自动计算逻辑电路的所有可能结果,并把真值表(即结果)事先写入 RAM,这样,每输入一个信号进行逻辑运算就等于输入一个地址进行查表,找出地址对应的内容,然后输出即可。

2020-12-29 16:59:44 4

4 如何进行OPCDCOM配置(四会理士电源技术有限公司招聘)-如何进行OPCDCOM配置

2021-09-18 14:23:09 11

11 上篇文章我们讲解了与逻辑, 缓冲器和非门只差一个圈吗? 而与之对应的就是或逻辑,在数字电路中与、或、非为三大基础逻辑门电路,其后续的与非、或非、同或、异或,都是建立在基础逻辑门电路的基础上边。 那么

2021-10-29 11:09:43 10756

10756

逻辑门使 MPU 和 FPGA 等更复杂的设备能够以最佳方式执行其功能

2022-08-16 11:21:27 789

789

逻辑门是数字世界中的基本元素,之前已经介绍过基本的逻辑门。这些基本的逻辑门可以由通用门构成。数字逻辑中有两个通用门,即与非门(NAND Gate)和或非门(NOR Gate)。

2022-09-12 14:50:00 13786

13786

在Allegro中如何进行skill的安装,下面就以下载FanySkill工具为例。

2022-10-17 11:03:46 6108

6108 采用Ioff的逻辑门和开关——让您进行掉电操作

2022-11-02 08:16:10 1

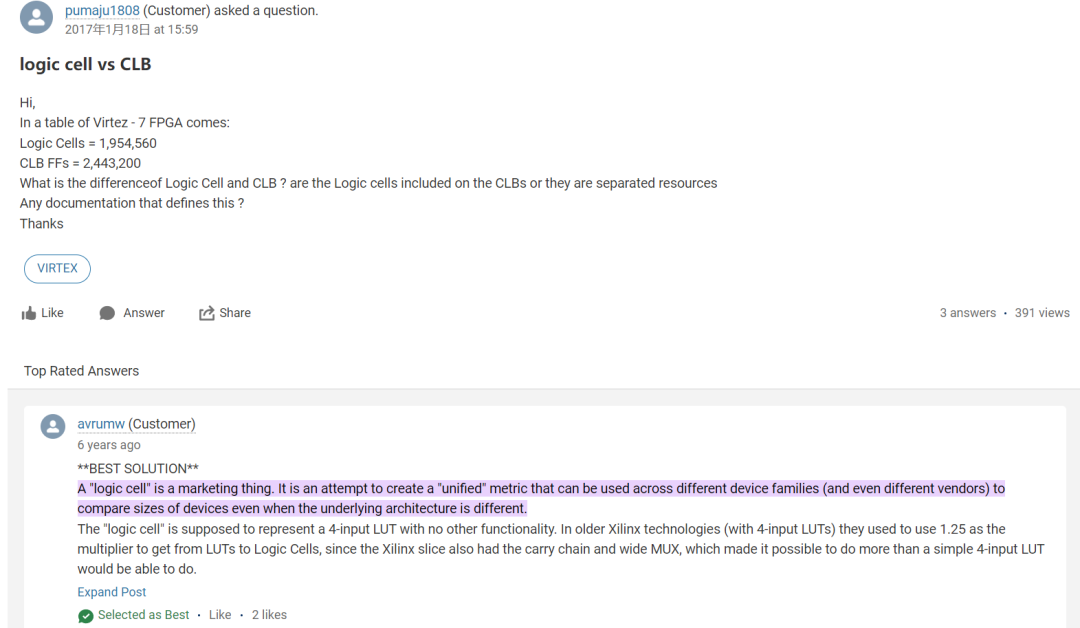

1 而且现在的LUT都是4输入或者6输入,可以做成逻辑门的组合,跟普通的逻辑门个数肯定不会是一对一关系。今天我们来看下这个关系如果对应。

2022-11-11 09:06:23 3556

3556 关于 FPGA 的 IO资源分析共分为三个系列进行具体阐述,分别为: IO资源:分析FPGA IO资源的电气特性; IO逻辑资源:分析FPGA的输入输出数据寄存器、DDR工作方式、可编程输入延时

2022-12-13 13:20:06 3155

3155 ZYNQ拥有ARM+FPGA这个神奇的架构,那么ARM和FPGA究竟是如何进行通信的呢?本章通过剖析AXI总线源码,来一探其中的秘密。

2023-02-16 09:26:57 14889

14889 FPGA设计的五个主要任务:逻辑综合、门级映射、整体功能逻辑布局、逻辑资源互连布线,最后生成FPGA的bit流

2023-04-06 09:39:45 1510

1510 逻辑门(LogicGates)是集成电路设计的基本组件,通过晶体管或MOS管组成的简单逻辑门,可以对输入的电平(高或低)进行一些简单的逻辑运算处理,而简单的逻辑门可以组合成为更复杂的逻辑运算,是超大规模电路集成设计的基础。

2023-04-30 09:14:00 5462

5462

用晶体管制造的逻辑门能够进行“与”“或”“非”等运算。近几十年来,科学家一直在尝试打造与电子门对应的光逻辑门。

2023-05-04 17:38:12 1391

1391

FPGA设计的五个主要任务:逻辑综合、门级映射、整体功能逻辑布局、逻辑资源互连布线

2023-05-23 15:25:21 1045

1045

本实验活动的目标是进一步强化上一个实验活动 “使用CD4007阵列构建CMOS逻辑功能” 中探讨的CMOS逻辑基本原理,并获取更多使用复杂CMOS门级电路的经验。具体而言,您将了解如何使用CMOS传输门和CMOS反相器来构建传输门异或(XOR)和异或非逻辑功能。

2023-05-29 14:17:17 5354

5354

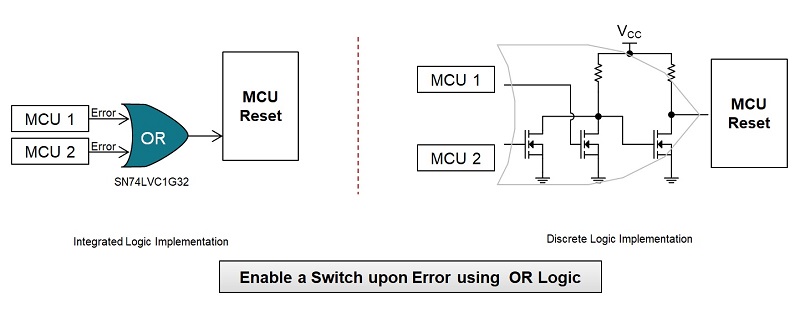

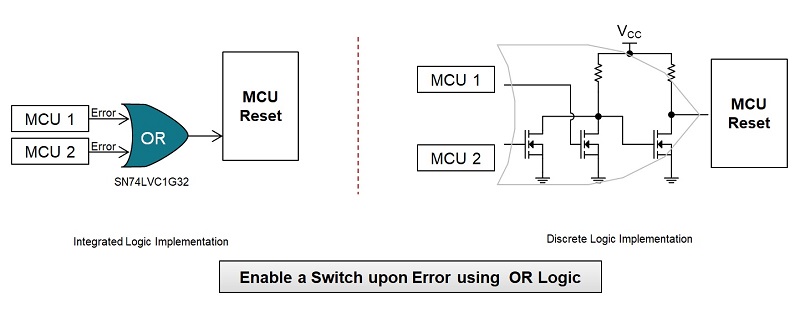

引言:在板极的逻辑控制中,基本逻辑门的使用特别广泛,包括与门,或门和外置信号驱动器,缓冲器等等,基本逻辑门相比于分立元件搭建的逻辑门,抗干扰能力和驱动能力更强,信号质量更好。运用最基本的逻辑门电路,使用逻辑代数可以构建出更复杂的控制逻辑以此满足设计需求。

2023-07-04 15:06:21 8236

8236

本文会用以下测试程序,来演示在bash中,如何进行各种文件重定向

2023-08-25 09:31:46 1947

1947

FPGA的BRAM和LUT等资源都是有限的,在FPGA开发过程中,可能经常遇到BRAM或者LUT资源不够用的情况。

2023-08-30 16:12:04 5313

5313

、异或非门。在大多数逻辑门中,低状态大约为零伏 (0 V),而高状态大约为正五伏 (+5 V)。

现在,我将展示使用 NPN 和 PNP 晶体管的逻辑门输出。

2023-09-25 11:40:35 1579

1579

FPGA,即现场可编程门阵列(Field Programmable Gate Array),是一种可编程逻辑设备,具有灵活性和可重新配置性的特点。它基于可编程逻辑单元(如逻辑门、触发器等)和可编程连线资源,可根据用户需求进行动态配置,实现不同的逻辑功能。

2024-03-14 15:29:10 2659

2659 FPGA,全称是Field Programmable Gate Array,即现场可编程门阵列。这是一种可编程逻辑设备,具有灵活性和可重新配置性的特点。FPGA基于可编程逻辑单元(如逻辑门、触发器等)和可编程连线资源,可根据用户需求进行动态配置,实现不同的逻辑功能。

2024-03-27 14:09:56 2702

2702 如何避免网络出现故障,增强网络安全性?又如何更加合理的规划分配网络资源?这就不得的提到我们需要定期给自家或企业中的IP进行检测了。IP 地址就像是网络世界中设备的“身份证号码”,定时进行检测,能够

2024-07-26 14:09:28 2042

2042

逻辑门是数字电路中的基本构建块,它们执行基本的逻辑运算,如与(AND)、或(OR)、非(NOT)、异或(XOR)等。逻辑门芯片是集成了多个逻辑门的集成电路,广泛应用于计算机、通信、自动化控制等领域

2024-09-24 10:48:10 6719

6719 在数字电子领域,TTL(晶体管-晶体管逻辑)逻辑门是构建复杂数字系统的基石。TTL技术以其可靠性、成本效益和广泛的应用而闻名。 TTL逻辑门的种类 TTL逻辑门可以分为基本的逻辑门和复合逻辑门两大类

2024-11-18 10:36:44 2520

2520

电子发烧友App

电子发烧友App

评论