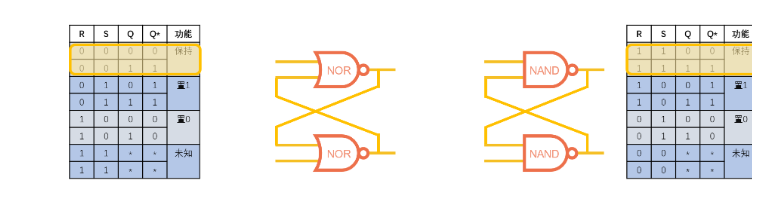

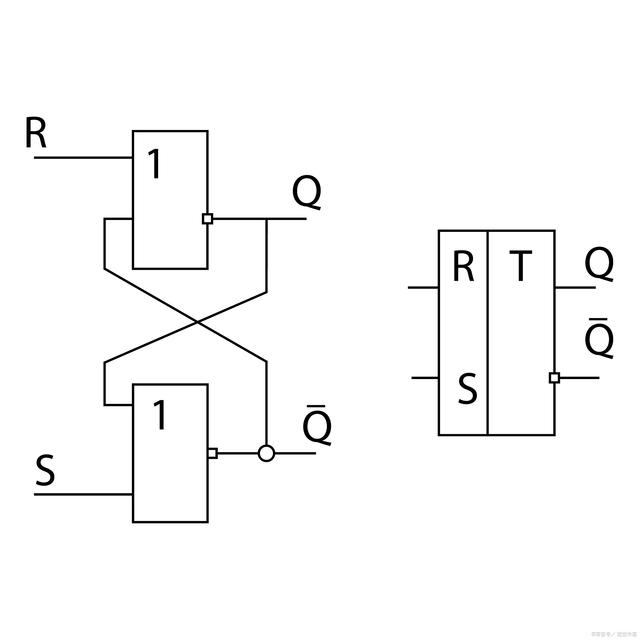

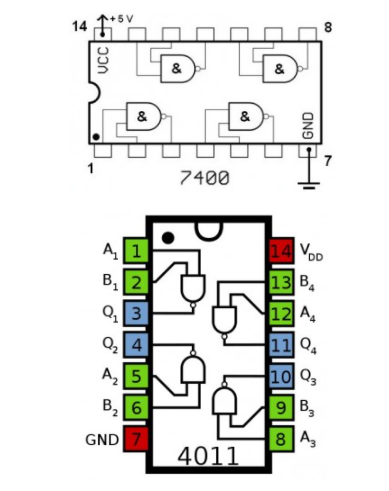

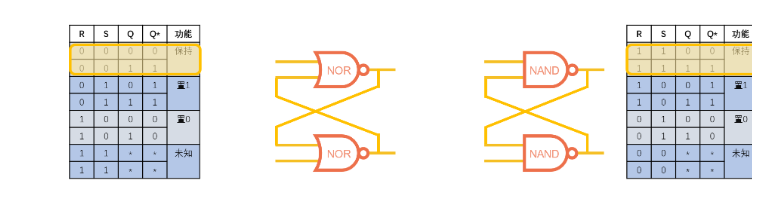

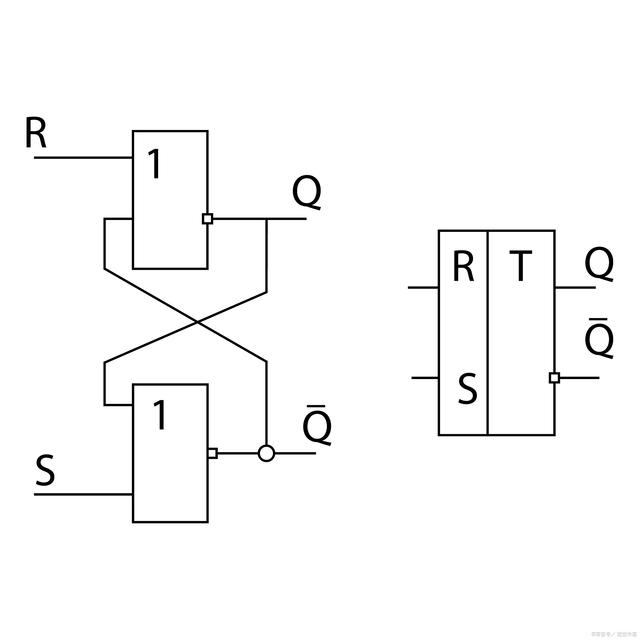

基本的RS触发器是一种使用与非门和或非门构成的存储器元件,它可以存储一个比特的信息并在触发信号的控制下改变状态。与非门和或非门则是用于逻辑运算的基本门电路,它们执行逻辑“与”和“或”运算并输出相应的结果。

2024-03-01 17:22:21 11972

11972

了解半加器、全加器的逻辑功能及三变量表决电路的逻辑功能。实验仪器设备1. 数字集成电路实验板 1块2. 直流稳压电源 1A,5V 1台3. 函数信号发生器 1台4. 示波器 1台5. 附加集成器件双

2008-09-25 17:28:34

串行时钟发生器用来产生 I2C 通信的波特率时钟 SCL。串行时钟发生器采用 PCLK 作为输入时钟,通过 1 个 8bit的计数器计数,输出所需波特率的 I2C 时钟信号。

SCL 时钟频率计

2025-12-15 07:26:02

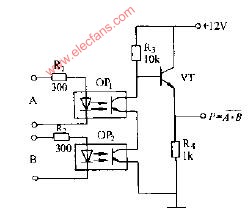

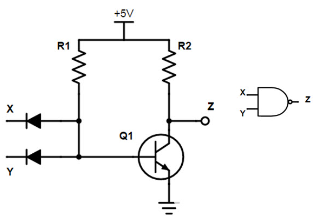

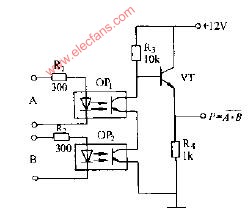

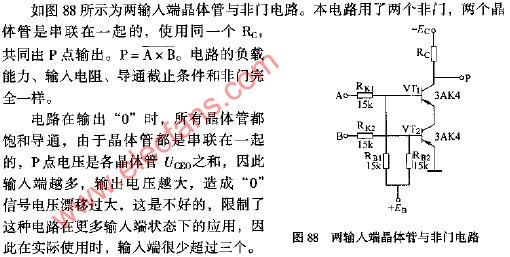

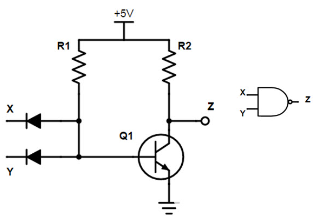

逻辑取反,从而使我们得到布尔值的表达式:AB= Q。然后,我们可以将2输入数字逻辑与非门的操作定义为:“如果A和B都为真,则Q不为真”晶体管与非门可以使用如下所示连接在一起的RTL电阻-晶体管开关构建

2021-01-22 08:00:00

串行时钟发生器用来产生 I2C 通信的波特率时钟 SCL。串行时钟发生器采用 PCLK 作为输入时钟,通过 1 个 8bit的计数器计数,输出所需波特率的 I2C 时钟信号。

SCL 时钟频率计

2025-12-08 08:16:31

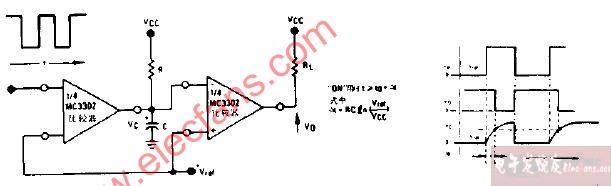

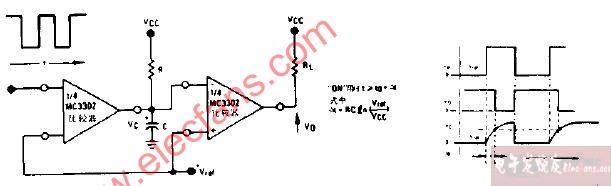

为什么我的pwm波信号一接到与非门上,幅值就会降一半(附电路图)

2018-02-02 21:20:33

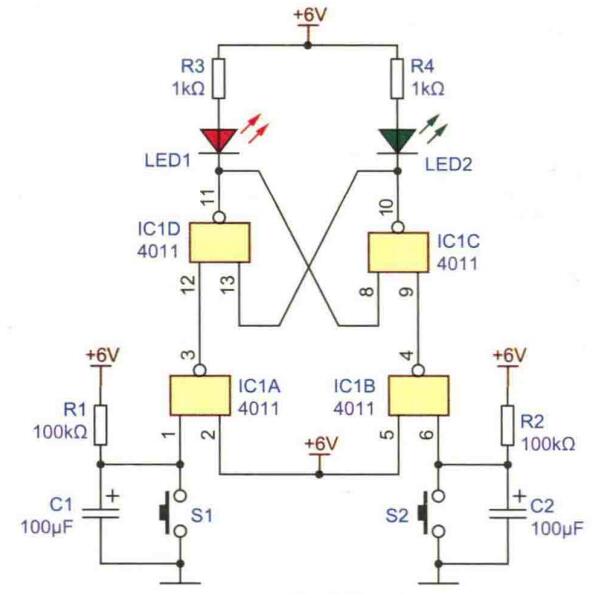

电路图

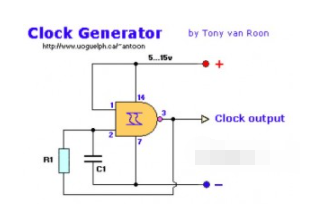

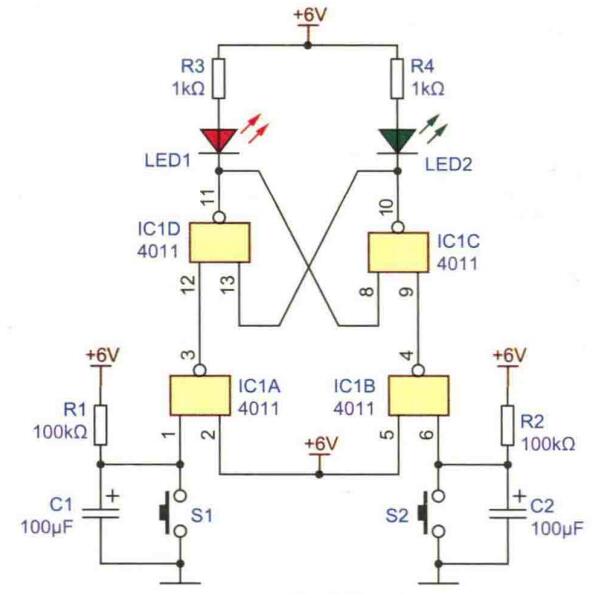

1、使用施密特触发器的方波发生器

施密特触发器方波发生器电路的工作与与非门的实现非常相似。 施密特触发器电路如图所示。这里也由 RC 网络提供时序。 逆变器将其反馈形式的输出作为输入之一

2024-04-02 14:24:15

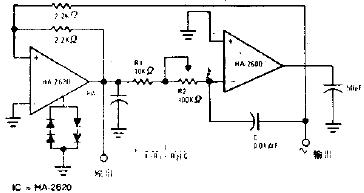

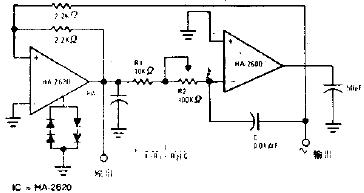

信号发生器电路图

2019-10-09 09:11:01

时钟发生器芯片厂家 时钟芯片是一种基于PLL的时钟发生器,采用ADPLL(全数字锁相环)技术,以实现的高频低相噪性能,并具备低功耗和高PSNR能力,可实现小于0.3ps RMS的相位抖动性能

2023-12-29 09:29:50

时钟发生器芯片厂家 时钟芯片是一种基于PLL的时钟发生器,采用ADPLL(全数字锁相环)技术,以实现的高频低相噪性能,并具备低功耗和高PSNR能力,可实现小于0.3ps RMS的相位抖动性能

2024-02-04 11:41:14

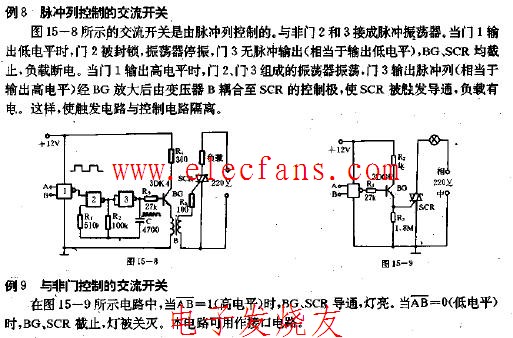

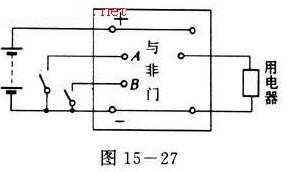

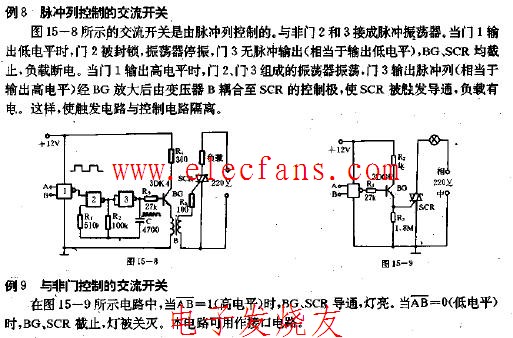

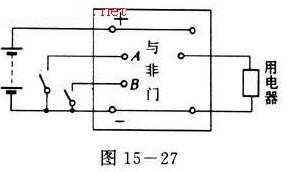

与非门控制的交流开关电路图

2007-12-16 01:26:06 1395

1395

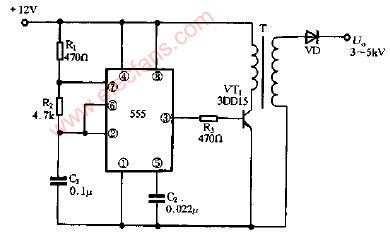

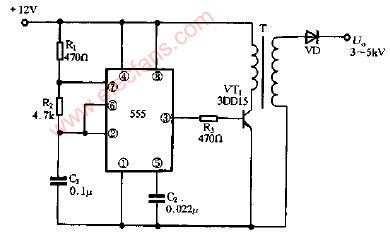

高压发生器电路图,这种高压发生器适用于需要高电压,小电流的场合,可获得数千

2007-12-26 20:27:10 3229

3229

函数发生器电路图,电路由MAX038,EL2001,TL072等元件组成,带电源电路。

2007-12-26 20:57:43 3231

3231

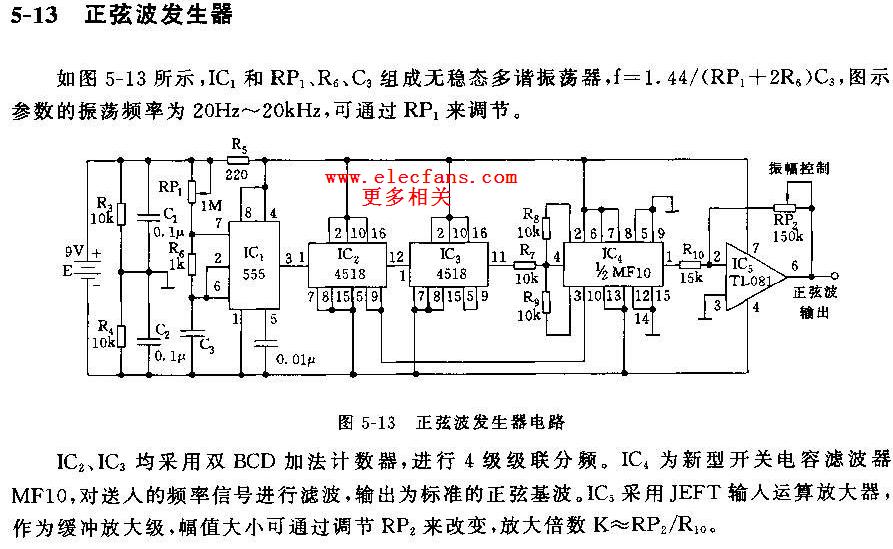

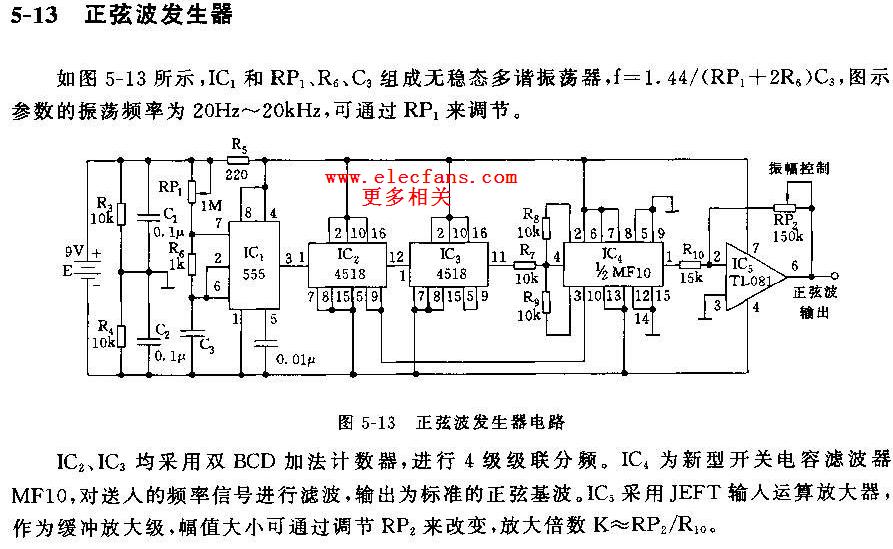

正弦波发生器电路图,电路由IC,TL082组成。

图二:正弦波信号发生器电路图

2008-01-02 19:16:06 4256

4256

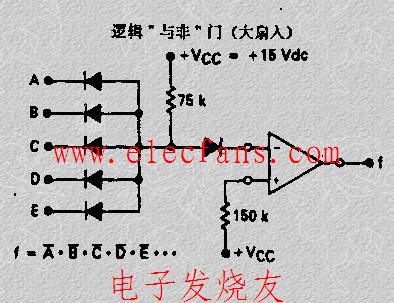

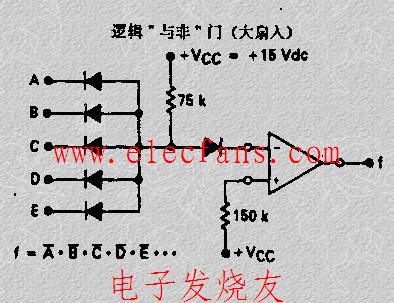

逻辑与非门

2008-06-12 23:24:21 2017

2017

MAX9489/MAX9471多输出时钟发生器构建集成时钟源

摘要:与典型的“本地”时钟方案相比,集成的多输出时钟发生器有许多优势。本文探讨了集中时钟发生器(如

2008-10-04 20:43:25 1179

1179

Si5338 业界首个任意频率、任意输出的时钟发生器

高性能模拟与混合信号领导厂商Silicon Laboratories日前发表全新的时钟发生器和缓冲器系列,可为业

2008-11-10 09:39:44 2208

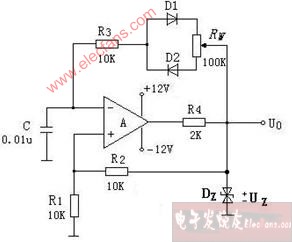

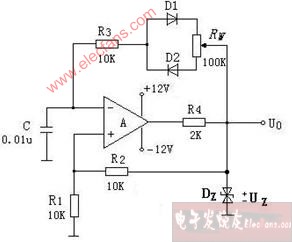

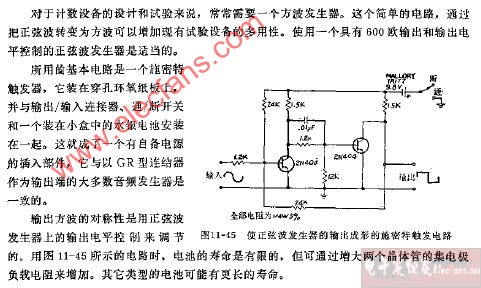

2208 方波发生器电路图

方波发生器电路图如图2所示:由反相输入的滞回比较器

2009-03-15 17:13:35 12292

12292

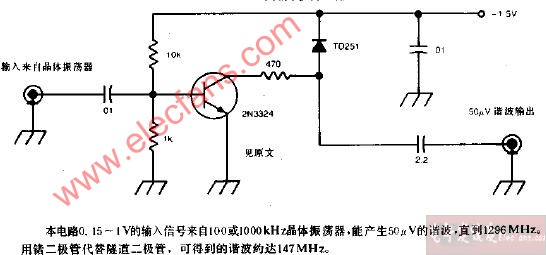

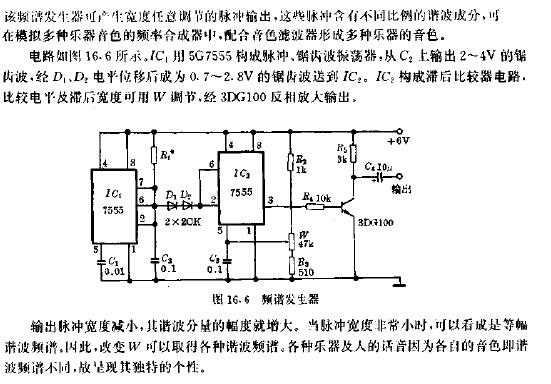

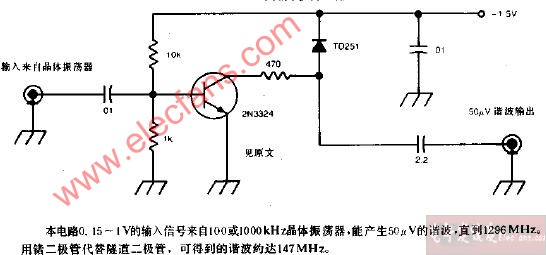

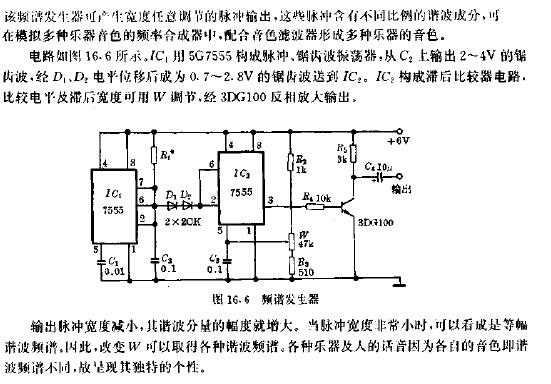

谐波发生器电路图

2009-03-21 08:49:39 3879

3879

精密时钟发生器电路图

2009-03-25 09:35:22 1456

1456

延时发生器电路图

2009-03-28 09:01:14 678

678

与非门逻辑符号

2009-04-06 01:12:18 2929

2929 与非门电路图

2009-04-06 23:12:46 10460

10460

与非门逻辑符号图

2009-04-06 23:13:21 43791

43791

与非门电路原理

(1)电路结构及工作原理 TTL与非门是TTL逻辑门的基本形式,典型的TTL与非门电路结构如图8-16所示。该电路由

2009-04-06 23:14:15 20333

20333

与非门电路介绍图15-26甲是我们实验用的与非门,它也有两个输入瑞A、B,图乙是它在电路中的接法。

2009-04-06 23:17:48 18020

18020

频谱发生器电路图

2009-04-09 12:01:31 1380

1380

振荡器时钟发生器电路图

2009-04-13 08:54:22 934

934

函数发生器电路图

2009-04-15 09:30:41 1773

1773

摘要:MAX9450/MAX9451/MAX9452是集成了VCXO,具有相同PLL内核和三种不同输出(LVPECL, HSTL,LVDS)的高精度时钟发生器。MAX945x时钟发生器具有四个主要的特点:集成VCXO,工作频率范围宽,PLL

2009-04-22 09:42:01 1345

1345

摘要:与典型的“本地”时钟方案相比,集成的多输出时钟发生器有许多优势。本文探讨了集中时钟发生器(如MAX9489和MAX9471)的优点,如:降低系统成本、良好的信号完整性、抑制干

2009-04-22 10:11:53 538

538

摘要:与典型的“本地”时钟方案相比,集成的多输出时钟发生器有许多优势。本文探讨了集中时钟发生器(如MAX9489和MAX9471)的优点,如:降低系统成本、良好的信号完整性、抑制干

2009-05-03 11:07:05 852

852

方波发生器电路图

2009-05-08 14:33:27 4632

4632

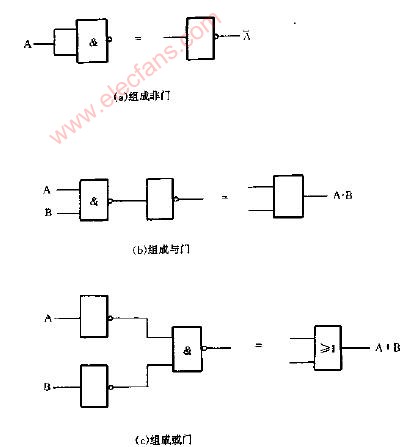

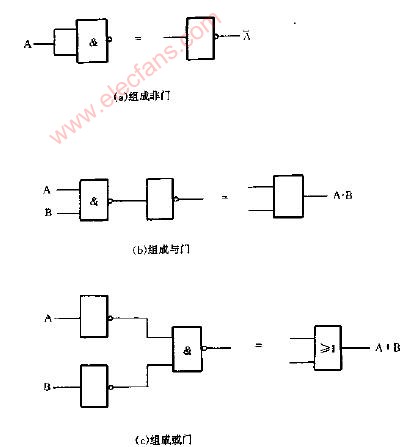

利用与非门组成的一些门电路图

2009-05-08 14:35:10 20348

20348

高压发生器电路图

2009-05-08 14:52:45 3506

3506

继电器与非门电路图

2009-05-08 15:35:18 2483

2483

声控发生器电路图

2009-05-08 15:37:12 671

671

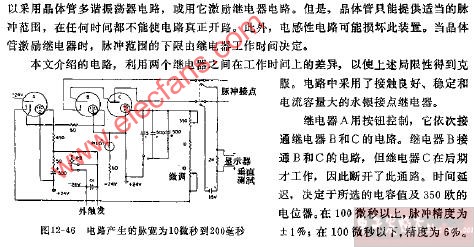

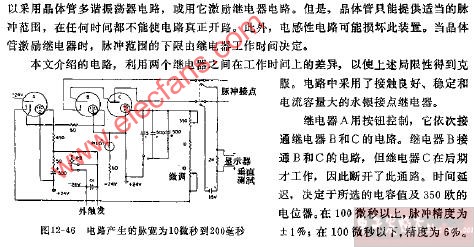

脉冲发生器电路图

2009-05-18 15:57:26 1995

1995

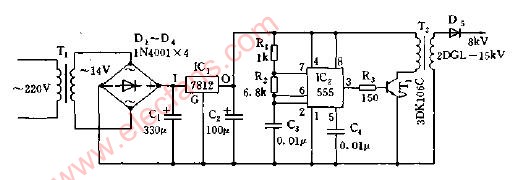

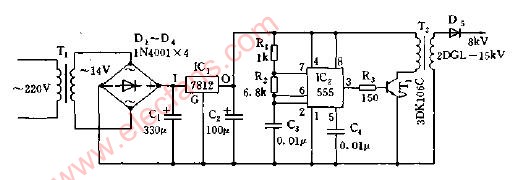

8kV高压发生器电路图

2009-05-30 13:42:17 2564

2564

数控音调发生器电路图

2009-05-30 15:59:04 1192

1192

光耦合器构成的与非门电路图

2009-06-04 16:25:53 5960

5960

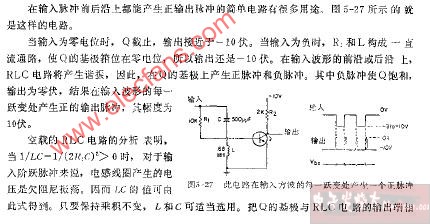

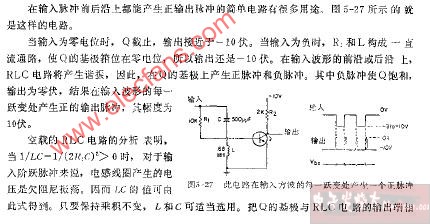

正脉冲发生器电路图

2009-06-26 13:44:58 1246

1246

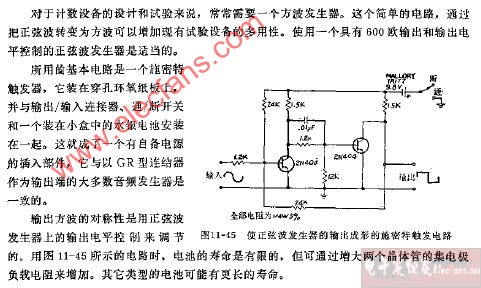

信号发生器的方波插入装置电路图

2009-06-30 13:46:04 767

767

单脉冲方波发生器电路图

2009-07-01 11:47:00 2958

2958

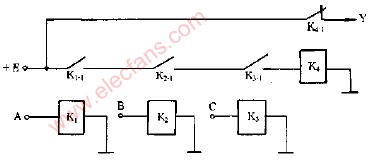

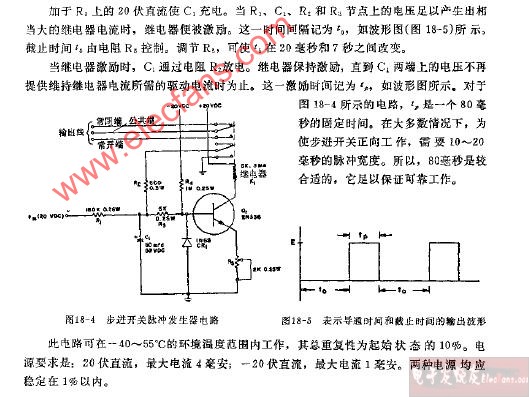

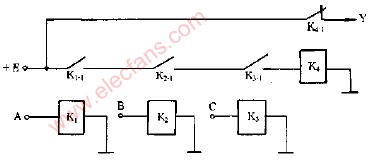

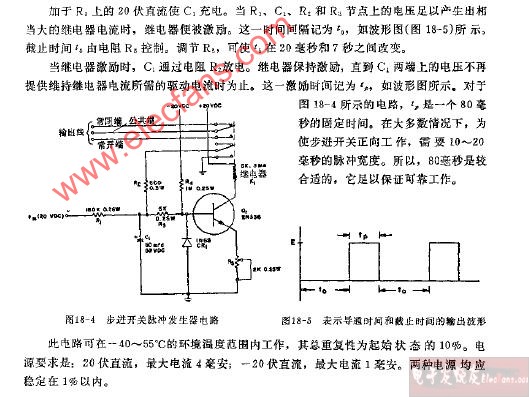

步进开关脉冲发生器电路图

2009-07-03 14:11:08 1141

1141

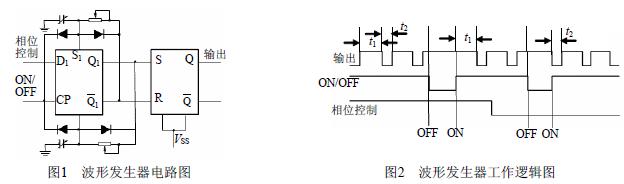

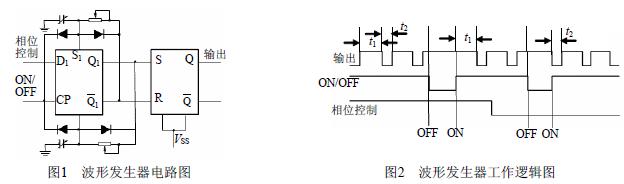

波形发生器电路图

交流驱动电

2009-07-17 18:48:05 5340

5340

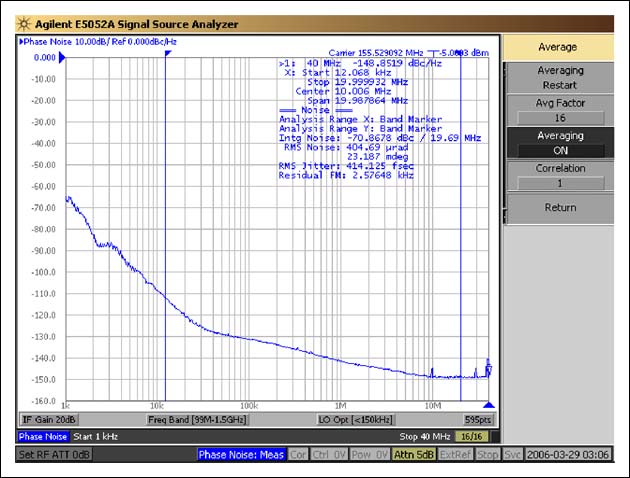

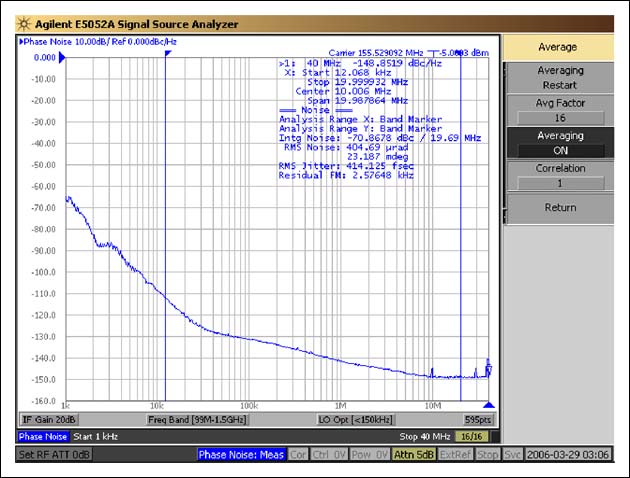

评估低抖动PLL时钟发生器的电源噪声抑制性能

本文介绍了电源噪声对基于PLL的时钟发生器的干扰,并讨论了几种用于评估确定性抖动(DJ)的技术方案。推导出的关系式提

2009-09-18 08:46:32 1853

1853

MAX3625B 抖动仅为0.36ps的PLL时钟发生器

概述

MAX3625B是一款低抖动、精密时钟发生器,优化用于网络设备。器件内置晶体振荡器和锁相环(PLL)

2010-03-01 08:56:18 1615

1615

与非门,与非门是什么意思

DTL与非门电路:

常将二极管与门和或门与三极管非门组合起来组成与非门和或非门电路,以消除在串接时产生的电

2010-03-08 11:41:15 12493

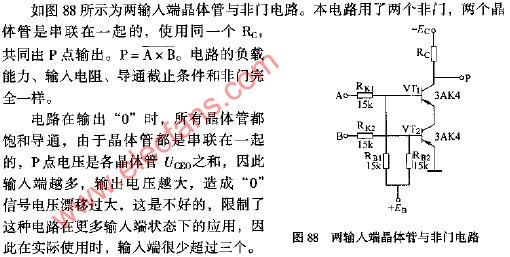

12493 两输入端晶体管与非门电路图

2010-03-29 17:03:19 5168

5168

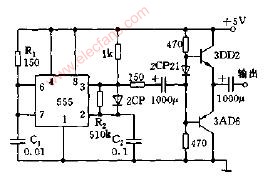

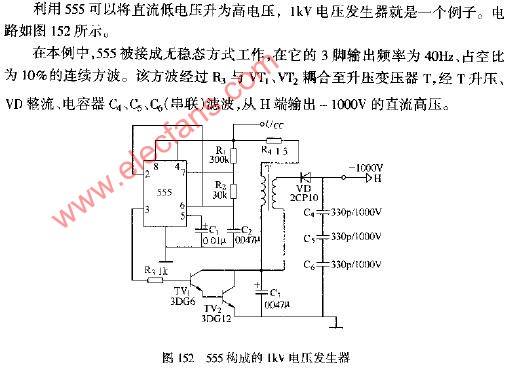

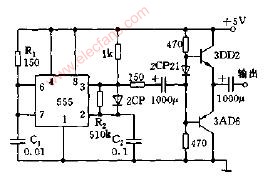

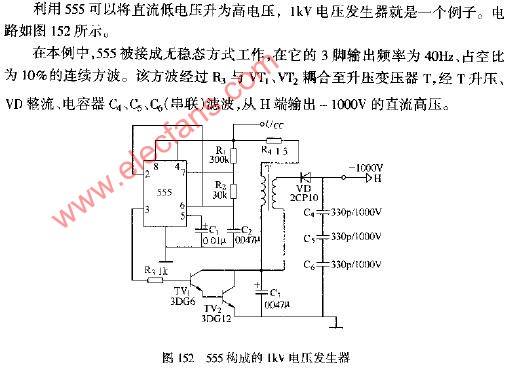

555构成的LKV电压发生器电路图

2010-03-30 15:08:05 1295

1295

MAX3679A高性能四路输出时钟发生器(Maxim)

Maxim推出用于以太网设备的高性能、四路输出时钟发生器MAX3679A。器件采用低噪声

2010-04-14 16:51:49 1150

1150 如何利用GPS OEM来进行二次开发,产生高精度时钟发生器是一个研究的热点问题。在电力系统、CDMA2000、DVB、DMB等系统中,高精度的GPS

2010-07-24 15:45:26 944

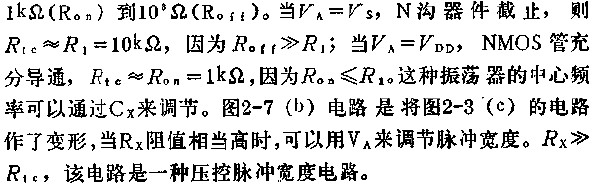

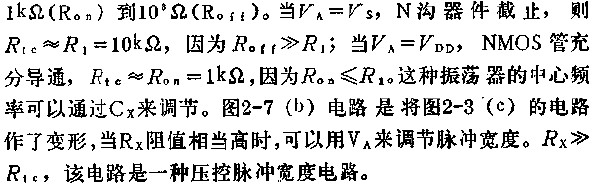

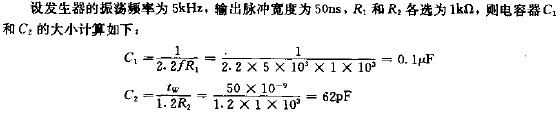

944 图是用CMOS与非门组成的压控振荡器电路。

图示线路类似图C的电路,C由可调的CX代替

2010-09-13 22:26:59 1987

1987

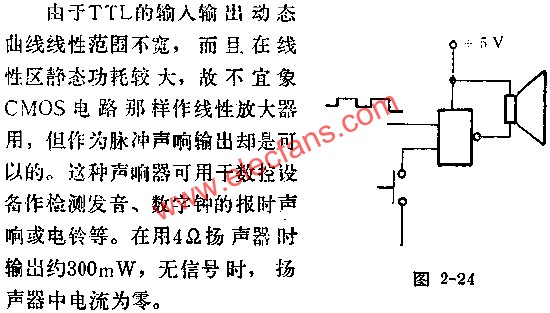

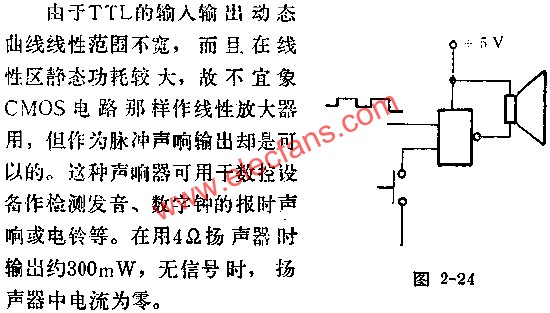

TTL与非门可以直接带动一只4欧或8欧的小扬声器,不用添加任何元件,只需将扬声器由与非门输出接至地端或电

2010-09-14 01:29:45 1012

1012

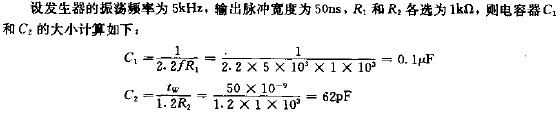

实际上,自激多谐振荡器(图1)和单稳电路可以由集成电路来实现.采用两片四-2输入与非门74LS00的驱动信号发生器,

2010-11-14 12:16:07 1271

1271

MAX3636是一个高度灵活,高精度锁相环(PLL)时钟发生器为下一代网络设备的要求低抖动时钟发生器和强大的高速数据传输的分布进行了优化。

2011-10-11 11:15:22 1699

1699

双环路时钟发生器可清除抖动并提供多个高频输出

2016-01-04 17:41:13 0

0 10GHz扩频时钟发生器的设计_胡帅帅

2017-01-07 21:28:58 1

1 系统设计师通常侧重于为应用选择最合适的数据转换器,在向数据转换器提供输入的时钟发生器件的选择上往往少有考虑。然而,如果不慎重考虑时钟发生器、相位噪声和抖动性能,数据转换器、动态范围和线性度性能可能受到严重的影响。

2017-11-17 02:00:58 1248

1248

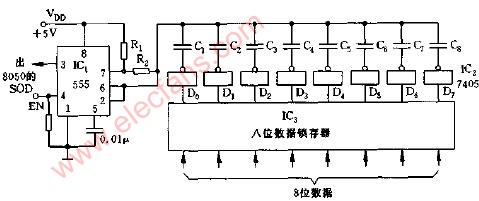

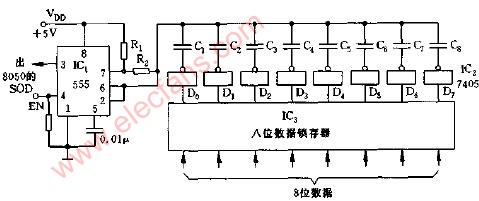

波形发生器原理图+电路图+程序

2017-11-23 09:13:31 34

34 Microchip基于MEMS的时钟发生器

2018-06-07 13:46:00 5525

5525

Microchip基于MEMS的时钟发生器

2018-07-08 01:23:00 4892

4892 关键词:发生器 , 负电源 , 与非门 在电子设备中有时需用一组功率不大的负电源,可用三个与非门按图所示方法连接,即可进行电源极性变换。图示电路中A1、A2组成约4kHz的自激多谐振荡器,A3起

2018-09-16 09:07:01 778

778 据麦姆斯咨询报道,Microchip推出了业界尺寸最小的MEMS时钟发生器DSC613。这款新器件可在电路板上最多替换掉三个晶振和振荡器,从而减少高达80%的时钟元件布板空间。

2018-11-15 16:38:26 4925

4925 AD9523:14路LVPECL/LVDS/HSTL输出 或29路LVCMOS输出 低抖动时钟发生器

2019-07-04 06:18:00 4964

4964 逻辑与非门是数字逻辑与门和非门串联连接在一起的组合,NAND (非与)门具有当输入的ALL处于逻辑电平“1”时,输出通常处于逻辑电平“1”并且仅“低”到逻辑电平“0”。逻辑与非门是我们之前看到的AND门的反向或“互补”形式。

2019-06-26 14:20:46 11836

11836

这是一个由与非门组成的、具有自动复位功能的抢答器实验电路,电路原理图见图4-121-1所示。

2019-09-27 09:21:03 11699

11699

本文档的主要内容详细介绍的是使用Multisim实现与非门测试的实验电路图免费下载。

2020-09-04 16:55:00 20

20 本文档的主要内容详细介绍的是与非门逻辑电路功能测试的原理图免费下载。

2020-10-12 16:18:48 25

25 本文档的主要内容详细介绍的是与非门搭接的逻辑电路原理图免费下载。

2020-10-12 16:18:48 7

7 系统设计师通常侧重于为应用选择最合适的数据转换器,在向数据转换器提供输入的时钟发生器件的选择上往往少有考虑。然而,如果不慎重考虑时钟发生器的相位噪声和抖动性能,数据转换器动态范围和线性度性能可能受到严重的影响。

2020-11-22 11:34:38 3554

3554

AD9525: 8路LVPECL输出低抖动时钟发生器

2021-03-21 15:00:20 0

0 AD9540:655 MHz低抖动时钟发生器数据表

2021-03-22 19:57:57 0

0 AD9571:以太网时钟发生器,10个时钟输出

2021-04-16 10:21:56 3

3 AD9520-5:12 LVPECL/24 CMOS输出时钟发生器数据表

2021-04-27 21:31:55 2

2 AD9516-5:14-输出时钟发生器数据表

2021-04-27 21:41:19 5

5 AD9551:多业务时钟发生器数据表

2021-04-28 10:30:52 0

0 AD9522-5:12 LVDS/24 CMOS输出时钟发生器数据表

2021-04-28 10:53:01 0

0 AD9573:PCI-Express时钟发生器IC,PLL内核,分频器,双输出数据表

2021-05-08 20:05:05 5

5 AD9575:网络时钟发生器,双输出数据表

2021-05-09 11:06:44 1

1 AD9531:3通道时钟发生器,24输出数据表

2021-05-15 15:24:07 11

11 AD9576:双锁相环异步时钟发生器数据表

2021-05-16 12:57:55 0

0 时钟发生器AD9516-0技术手册

2022-01-25 15:59:42 8

8 Cypress时钟发生器应用在车辆、工业生产、消费品和网络服务的EMI降低和非EMI降低时钟发生器。 Cypress具有广泛的时钟发生器组合,兼容700MHz的频率和不超过0.7PS的RMS相位抖动

2022-04-22 09:02:09 1314

1314 这是带有板上芯片(COB)的1Hz时钟发生器电路。通常,为数字时钟和计数器电路应用产生1Hz时钟的电路将IC与晶体和微调电容器等结合使用。

2022-06-07 10:43:50 3854

3854

逻辑门是数字世界中的基本元素,之前已经介绍过基本的逻辑门。这些基本的逻辑门可以由通用门构成。数字逻辑中有两个通用门,即与非门(NAND Gate)和或非门(NOR Gate)。

2022-09-12 14:50:00 13786

13786

超低抖动时钟发生器如何优化串行链路系统性能

2022-11-04 09:50:15 0

0 9ZXL1951D PCIe 时钟发生器评估板用户指南

2023-03-21 19:21:13 1

1 本文讨论电源噪声干扰对基于PLL的时钟发生器的影响,并介绍几种用于评估由此产生的确定性抖动(DJ)的测量技术。派生关系显示了如何使用频域杂散测量来评估时序抖动行为。实验室台架测试结果用于比较测量技术,并演示如何可靠地评估参考时钟发生器的电源噪声抑制(PSNR)性能。

2023-04-11 11:06:39 2462

2462

9ZXL1951D PCIe 时钟发生器评估板用户指南

2023-07-07 19:19:11 0

0 与非门(NAND Gate)是数字电路中的基本逻辑门之一,它实现了逻辑AND(与)操作后再进行逻辑NOT(非)操作。

2023-09-04 15:31:07 7040

7040

时钟发生器由哪些部分组成?锁相环pll的特点是什么?如何用硬件配置pll 时钟发生器是指通过特定的电路设计产生适合各种电子设备使用的时钟信号的器件。时钟发生器由多个部分组成,其中最核心的是锁相环

2023-10-13 17:39:50 2233

2233 时钟合成器和时钟发生器是两种用于产生时钟信号的电子器件,它们在功能和应用上有一些区别。

2023-11-09 10:26:56 1541

1541 的时钟发生器件的选择上往往少有考虑。目前市场上有性能属性大相径庭的众多时钟发生器。然而,如果不慎重考虑时钟发生器、相位噪声和抖动性能,数据转换器、动态范围和线性度性能可能受到严重的影响。...

2023-11-28 14:33:57 0

0 TTL与非门的电压传输特性 TTL与非门的静态输入与输出特性 TTL与非门的动态特性 TTL与非门是一种基本的逻辑门电路,用于将两个输入信号进行逻辑与运算,并输出结果。TTL(双晶体管逻辑)是一种

2024-01-23 13:52:51 7603

7603 时钟发生器,作为一种关键的电子设备,负责生成精确且稳定的时钟信号。这些信号在各类电子系统中作为时间基准,确保系统的正常运行和性能。本文将深入探讨时钟发生器的定义、工作原理、特点及其在实际应用中的广泛案例,以期为相关领域的研究者和工程师提供全面的技术参考。

2025-02-05 17:17:34 1706

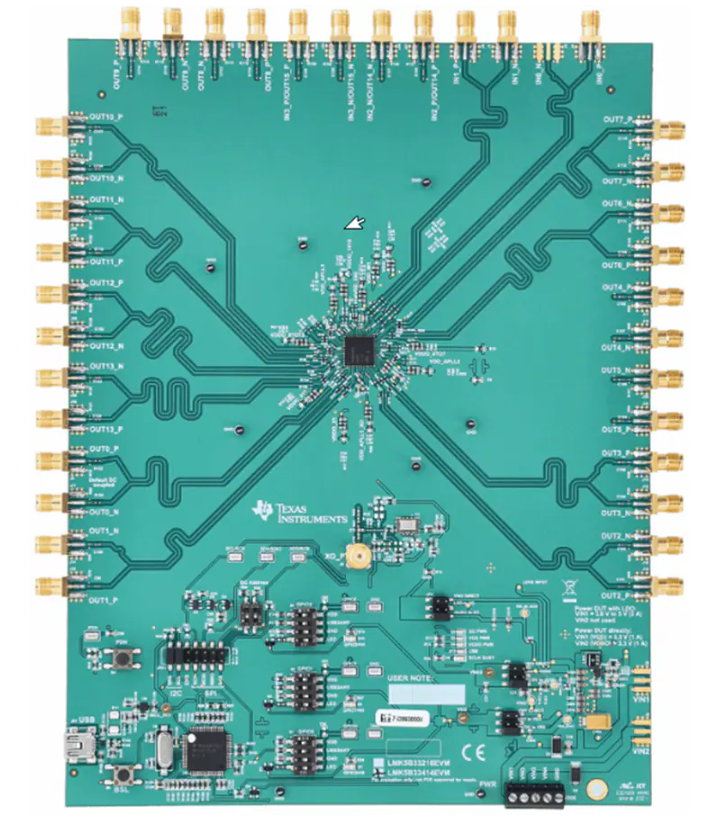

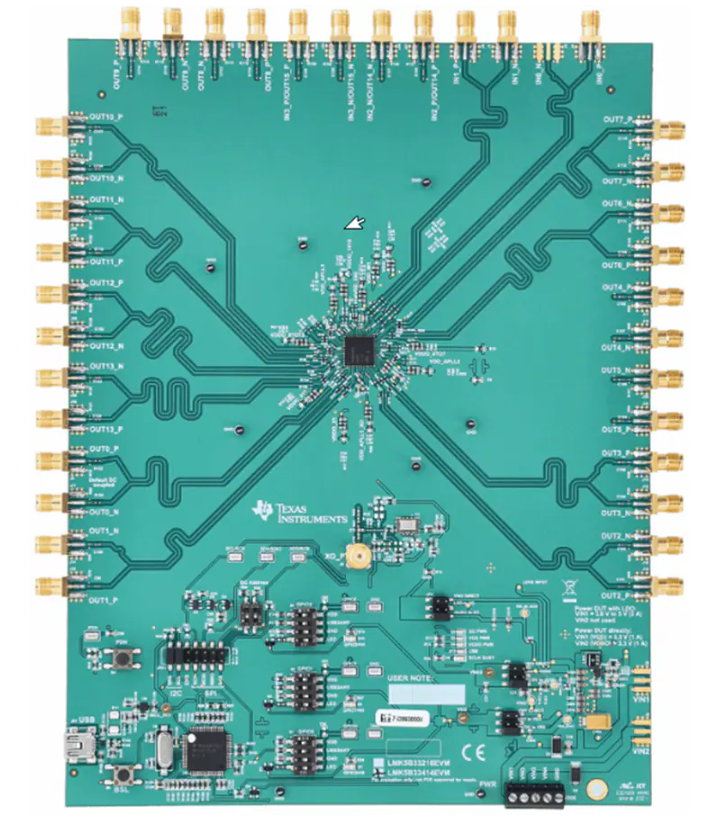

1706 Texas Instruments LMK5B33414EVM时钟发生器和合成器评估模块 (EVM) 是一个用于对LMK5B33414网络时钟发生器和同步器进行器件评估、合规性测试和系统原型设计的平台。

2025-09-08 15:03:16 680

680

的关键因素。技术创新的先锋时钟发生器技术的不断创新是其保持竞争力的首要因素。通过采用前沿的半导体材料和先进的电路设计,现代时钟发生器能够实现更高的频率稳定性和更低

2025-10-23 17:20:30 493

493

电子发烧友App

电子发烧友App

评论