每一个系列的FPGA都有其相应的内部结构),FPGA芯片主要由6部分完成,分别为:可编程输入输出单元、基本可编程逻辑单元、完整的时钟管理、嵌入块式RAM、丰富的布线资源、内嵌的底层功能单元和内嵌专用硬件模块。

2022-10-25 09:01:05 2912

2912 . (2)FPGA处理模块 FPGA采用 Xilinx新一代V5系列芯片,选择型号为:XC5VSX95T-1136C,XC5VLX110T 具有逻辑模块160 x 46 最大RAM模块

2014-06-27 14:58:31

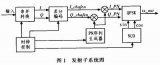

FPGA实现直接数字频率合成(DDS)的原理、电路结构和优化方法介绍了利用现场可编程逻辑门阵列FPGA实现直接数字频率合成(DDS)的原理、电路结构和优化方法。重点介绍了DDS技术在FPGA中的实现

2012-08-11 18:10:11

FPGA实现逻辑函数用的什么电路结构?

2017-01-01 21:49:23

芯片、FPGA1中的数据接口模块、配置模块、测试模块和被测FPGA。软件部分包含对实现FPGA配置部分的代码和实现FPGA测试部分的代码。FPGA1中的各硬件模块通过EDA软件以JTAG接口固化

2020-05-14 07:00:00

,实际上每一个系列的FPGA都有其相应的内部结构),FPGA芯片主 要由6部分完成,分别为:可编程输入输出单元、基本可编程逻辑单元、完整的时钟管理、嵌入块式RAM、丰富的布线资源、内嵌的底层功能单元和内嵌

2017-05-09 15:10:02

一、FPGA的基本结构 FPGA由6部分组成,分别为可编程输入/输出单元、基本可编程逻辑单元、嵌入式摸块RAM、丰富的布线资源、底层嵌入式功能单元和内嵌专用硬核等。 每个单元简介如下: 1.

2016-09-18 11:15:11

常常忽略布线资源。其实布线资源的优化与使用和实现结果有直接关系。 5.底层嵌入功能单元(书上举了很多例子,不过这些东东要看具体哪个厂商的哪种型号的芯片上嵌有什么资源决定) 6.内嵌专用硬核 与“底层嵌入单元”是有区别的,这里指的硬核主要是那些通用性相对较弱,不是所有FPGA器件都包含硬核。

2016-07-16 15:32:39

,所以常常忽略布线资源。其实布线资源的优化与使用和实现结果有直接关系。 5.底层嵌入功能单元(书上举了很多例子,不过这些东东要看具体哪个厂商的哪种型号的芯片上嵌有什么资源决定) 6.内嵌专用硬核 与“底层嵌入单元”是有区别的,这里指的硬核主要是那些通用性相对较弱,不是所有FPGA器件都包含硬核

2019-09-24 11:54:53

,所以常常忽略布线资源。其实布线资源的优化与使用和实现结果有直接关系。 5.底层嵌入功能单元(书上举了很多例子,不过这些东东要看具体哪个厂商的哪种型号的芯片上嵌有什么资源决定) 6.内嵌专用硬核 与“底层嵌入单元”是有区别的,这里指的硬核主要是那些通用性相对较弱,不是所有FPGA器件都包含硬核。

2016-08-23 10:33:54

,所以常常忽略布线资源。其实布线资源的优化与使用和实现结果有直接关系。 5.底层嵌入功能单元(书上举了很多例子,不过这些东东要看具体哪个厂商的哪种型号的芯片上嵌有什么资源决定) 6.内嵌专用硬核 与“底层嵌入单元”是有区别的,这里指的硬核主要是那些通用性相对较弱,不是所有FPGA器件都包含硬核。

2016-10-08 14:43:50

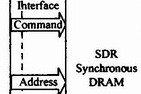

SDRAM文件结构存储控制的FPGA实现面对不同的应用场景,原始采样数据可能包含多种不同样式的信号,这给传统基于连续存储方式的数据缓存系统带来了挑战。除此之外,由于对不同信号的处理往往需要不同的数据

2012-08-13 10:40:40

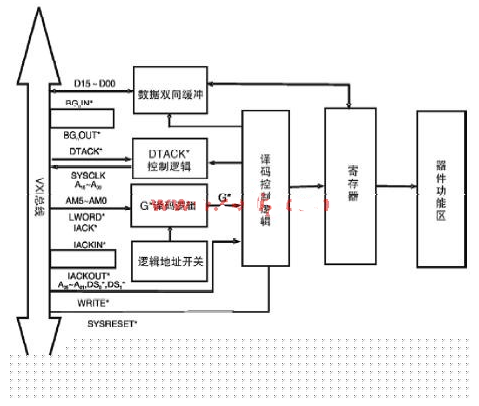

方式总线方式是指严格按图1用FPGA实现相应结构的微型机。本实验采用上海航虹公司的AEDK实验箱,FPGA芯片为Altera公司的EPF10K20TC144-4,软件采用QuartusII4.0

2014-12-04 14:35:41

方式总线方式是指严格按图1用FPGA实现相应结构的微型机。本实验采用上海航虹公司的AEDK实验箱,FPGA芯片为Altera公司的EPF10K20TC144-4,软件采用QuartusII4.0

2014-12-04 14:36:22

)。本文介绍了一种读写器的编解码部分由FPGA来完成的设计方案,由FPGA负责前向链路的PIE编码和后向链路的FM0/miller解码,且解码模块可对标签突发传来的数据立即检测并实施解码,实现了较快的解码速率。FPGA选用的是Altera公司的EP1C3T100C6芯片。

2019-07-26 06:47:39

。满足了飞行员对大尺寸和高清晰视频显示的需求。模块接收显示命令和视频数据,将融合信息加速显示到显示器上,同时接收解码两路高清外视频信号,在FPGA芯片中实现内视频和外视频的运算处理,包括缩放和叠加

2018-11-07 10:42:22

各位大侠,有用FPGA做过旋变解码芯片算法的吗?

2014-03-22 08:23:16

)、离散余弦变换(DCT)、小波变换、数字滤波器(有限脉冲响应(FIR)、无限脉冲响应(IIR)和自适应滤波器)以及数字上下变频器。这些算法中,每一种都有一些结构性的元件可以用并行方法实现。而FPGA

2021-12-15 06:30:00

基于FPGA和视频解码芯片的实时图像采集系统设计

2017-12-26 16:51:49

基于FPGA和视频解码芯片的实时图像采集系统设计,介绍了CCD图像传感器和ADV7181B解码芯片的I2C配置原理。给出了乒乓缓存的原理与实现方法,同时给出了ADV7181B与FPGA等芯片组成视频处理电路的设计和FPGA的程序实现方法。

2017-11-17 13:59:48

文章介绍了一种在FPGA上用PowerPC405实现MP3实时解码SoC系统的方法。通过使用IP核搭建SoC硬件结构,并进行定点MP3解码软件算法移植,完成软硬件协同设计和验证,实现MP3音乐实时

2010-05-28 13:42:09

本文介绍了一种0.13微米CMOS T艺下FPGA中嵌入式存储器模块的设计与实现。

2021-04-09 06:02:09

如何实现一个基于FPGA的红外遥控解码和实现FPGA与PC机的串口通信?

2021-10-14 07:05:06

的技术标准,简称AC′97. AC′97采用双集成结构,即Digital Controller(数字信号控制器)和Audio Codec(音频编解码),使模/数转换器ADC和数/模转换器DAC转换模块独立

2019-10-18 07:18:26

SoC芯片结构及物理实现流程介绍SoC芯片时序约束设计的关键在于功耗管理控制模块的时序约束时钟树设计的内容有哪些?

2021-04-13 06:45:17

AC-Link音频编/解码原理是什么?怎么实现AC-Link数字音频VHDL编/解码的FPGA设计?

2021-05-10 06:46:20

系统软件设计系统软件主要是对系统控制核心的FPGA的编程。整个程序基于模块化、结构化的软件开发思想编写。所用的开发工具是Altera公司出品的FPGA集成开发环境QuartusII,开发语言采用当今

2019-07-17 07:43:08

驱动模块对WM8731写控制字的时序仿真如图8所示。图中各引脚定义如表2所示。 4 结 语 利用FPGA对音频编解码芯片WM8731进行接口电路的设计,实现了控制接口与数字音频接口的统一控制,简化

2019-05-22 05:01:13

主要讲解了fpga设计、方法和实现。这本书略去了不太必要的理论、推测未来的技术、过时工艺的细节,用简明、扼要的方式描述fpga中的关键技术。主要内容包括:设计速度高、体积小、功耗低的体系结构方法

2012-03-01 14:59:23

介绍应用于嵌入式系统的CD-ROM格式数据软解码模块的设计方法;分析CD-ROM格式的数据结构, 给出EDC 及ECC 解码算法的软件实现方法以及该模块的软件流程图。

2009-04-16 10:15:24 12

12 介绍应用于嵌入式系统的CD-ROM格式数据软解码模块的设计方法;分析CD-ROM格式的数据结构, 给出EDC 及ECC 解码算法的软件实现方法以及该模块的软件流程图。

2009-05-15 13:56:06 20

20 本文讨论了一种可在FPGA 上实现的FFT 结构。该结构采用基于流水线结构和快速并行乘法器的蝶形处理器。乘法器采用改进的Booth 算法,简化了部分积符号扩展,使用Wallace 树结构和4-2

2009-09-11 15:46:40 16

16 主要介绍基于现场可编程门阵列(FPGA)的微波接力通信中FFT 模块的设计与实现方案。提出一种全并行流水结构,采用新一代大容量的高速Stratix 系列FPGA 可以在N 个系统时钟之内

2009-11-24 12:13:19 19

19 介绍了一种使用射频技术的无线收发模块的编解码应用设计,自主调制与解调,该方式电路连接简单,传输距离远,且不受方向性约束。选用未经编码的无线模块,通过FPGA实现编

2009-12-18 12:03:57 10

10 介绍了一种采用并行方式构建的多符号可变长码解码器。该解码器通过增加结构的复杂性和对硬件资源的占用,换取可变长码解码的高吞吐量。这种结构突破了可变长码码字之间的

2010-07-17 15:01:19 17

17 介绍了一种使用射频技术的无线收发模块的编解码应用设计,自主调制与解调,该方式电路连接简单,传输距离远,且不受方向性约束。选用未经编码的无线模块,通过FPGA实现编码

2010-07-21 17:40:24 27

27

提出一种将FPGA与PowerPC芯片结合,实现MIL-STD-1553B通信模块的技术方案。详细讨论了该系统的结构、1553B总线协议在FPGA上的实现以及系统的软件结构等关键技术。该系统方案与采

2010-09-10 10:10:27 56

56 本文提出了一种基于文件结构存储方式的数据缓存系统,该系统利用FPGA设计结构化状态机实现对SDRAM的控制,完成

2010-11-25 11:19:03 1442

1442

高级FPGA设计结构

2011-01-10 10:36:50 295

295 本文对扩频芯片关键模块的实现方法进行了阐述,并推导出详细参数,基于ISE 10.1实现了整个系统,最后下载到FPGA芯片中调试成功。

2011-02-25 10:19:57 2117

2117

摘要:为提高8B/10B编解码的工作速度和简化逻辑方法,提出一种基于FPGA的8B/10B编解码系统设计方案。与现有的8B/10B编解码方案相比,该方案是一种利用FPGA实现8B/lOB编解码的模块方

2011-05-26 11:08:20 4329

4329

在本文工作的基础上,可以进一步发挥FPGA的灵活性。如可以利用FPGA实现DSP功能,从而提供音频DSP处理或编码解码;也可以与SoPC相结合,作为音频接口模块,为片上系统提供音频接口

2011-06-24 10:38:33 7982

7982

循环冗余码校验 CRC (Cyclic Redundancy Check) 广泛用于通讯领域和数据存储的数据检错。基于FPGA在通讯领域和数据存储的应用越来越广泛,CRC的编码解码模块已经是FPGA上的常用模块了。采

2011-08-15 11:19:57 40

40 在研究密勒调制副载波序列特点的基础上,提出一种基于FPGA并运用VerilogHDL硬件描述语言实现的密勒调制 副载波 编解码设计方法,并利用Altera公司CycloneI系列EP1C12Q芯片与Verilog HDL硬件描

2011-08-15 11:26:30 33

33 介绍了音频编解码芯片WM8731基于FPGA的 接口电路 的设计,包括芯片配置模块与音频数据接口模块等,使得控制器只通过寄存器就可以方便地对其进行操作。整个设计以VHDL和Verilog HDL语言

2011-09-15 11:42:55 12195

12195

本文讨论了MELP混合线性码激励的FPGA实现的硬件构成,介绍了硬件主要组成芯片及MELP编解码的主要框架,可以用于下一步软件程序的编制。

2011-12-29 09:38:13 1736

1736

高级FPGA设计结构、实现和优化 作者:(美)克里兹著,孟宪元译;出版社:机械工程出版社 学FPGA不一定需要开发板,自己学会modelsim仿真、写testbench,用PC机仿真就能有不少长进。这

2012-11-28 14:03:22 0

0 dac0832ad08098259a,825382508255等芯片的fpga实现及仿真

2016-01-20 15:12:47 13

13 基于FPGA的JPEG解码算法的研究与实现,很好的资料,快来学习吧

2016-02-18 13:53:55 0

0 G.7xx语音编解码模块及在AD218X上的实现,PPT教程。

2016-04-14 17:59:41 0

0 13曼彻斯特码编解码的FPGA设计与实现-9。

2016-04-26 15:12:57 12

12 RS编解码的FPGA实现-说明RS编解码的FPGA实现-说明。

2016-05-04 15:59:44 21

21 高级FPGA设计 结构、实现和优化,适合于FPGA的进阶学习。

2016-05-11 16:40:55 15

15 高级FPGA设计 结构、实现和优化,适合于学习FPGA的进阶学习。

2016-05-11 16:40:55 14

14 基于FPGA的JPEG解码算法的研究与实现

2016-08-29 16:05:01 11

11 基于FPGA的JPEG实时图像编解码系统

2016-08-29 16:05:01 16

16 一种高速卷积编解码器的FPGA实现

2017-02-07 15:05:00 22

22 基于FPGA的高速DSP与液晶模块接口的实现

2017-10-19 13:46:23 3

3 数字存储示波器采用ARM 与FPGA 双处理器结合的嵌入式系统设计方案,重点介绍在FPGA 中如何实现对外围芯片的通信与驱动,采用VHDL 语言,以逐层描述的设计模式,分成ARM 接口通信控制模块

2017-11-18 05:47:29 3203

3203

每个FPGA芯片(FPGA)是由有限个带有可编程连接预定义资源组成。这些互连资源通过LabVIEW FPGA模块实现用户设计的数字电路。用户创建FPGA VI时设计一个电路示意图,以说明FPGA逻辑

2017-11-18 05:57:01 1138

1138

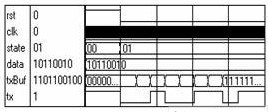

设计,详述了各子模块的设计思路和方法,给出了它们的仿真时序图。综合实现后,将程序下载到FPGA芯片中,运行正确无误。又经长时间发送和接收测试,运行稳定可靠。

2017-11-18 11:33:01 6257

6257 的兼容性。 这里详细介绍了Virtex 系列FPGA 芯片的数据流大小及结构。Virtex支持一些新的非常强大的配置模式,包括部分重新配置,这种配置机制被设计到高级应用中,以便通过芯片的配置接口能够访问及操作片内数据。但想要配置芯片,对它的数据流结构的了解是必不可少的。

2017-11-18 11:37:38 2960

2960 和通用性上都不理想。针对RICE算法中自适应熵编码的特点,设计了一种基于有限状态机和查找表的并行RICE解码结构,可在FPGA上完成8比特宽度的并行解码,解码速度最高可达176 MB/s;同时,该解码结构适用于编码参数足变化的情况,具有很强的通用性。

2017-11-20 14:21:55 8

8 操作的延迟,我们在设计中还引入了流水线操作方式、码表分割等技术,这些技术有利于并行操作的实现。在文章的最后一部分,我们给出了FPGA的仿真结果,结果显示这种结构的解码器完全能够满足MPEG-4的可变长数据的解码需求。

2018-04-23 15:09:09 10

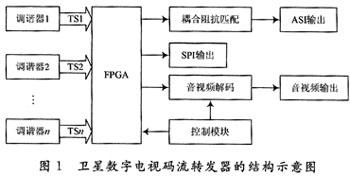

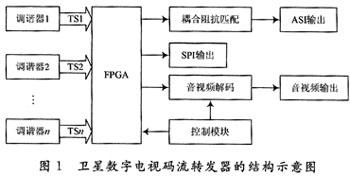

10 的数据链路层的具体实现、SPI输出以及TS流的转接到音视频解码芯片上;控制部分主要负责码流路由选择和音视频解码部分的控制。其内部结构如图1所示。

2018-12-21 07:59:00 4498

4498

三坐标测量机做为一种高精度测量仪器,在机械工业、汽车工业、航空航天等领域具有广泛的应用。本套通讯系统采用FPGA为主要通讯芯片,使用FPGA实现各通讯模块对数据的收发,配合单片机对数据进行编码、解码

2019-04-30 08:25:00 1986

1986

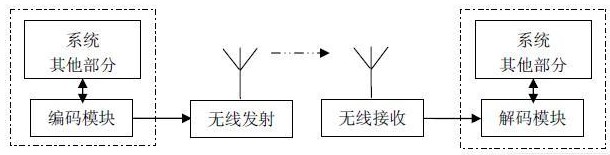

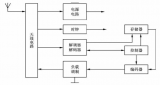

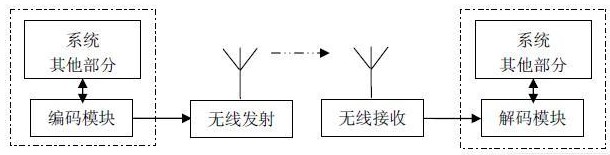

系统分为接收和发射两部分,使用非编码的无线发射模块和接收模块进行无线数据的传输,发送和接收部分各自具有独立的逻辑模块进行编码或解码,可以和系统其他部分进行数据交互,如图 1。

2019-05-10 08:30:00 3265

3265

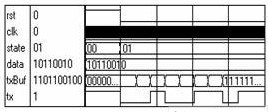

的实现方法,具体描述了发送、接收等模块的设计,恰当使用了有限状态机,实现了FPGA上的UART的设计,给出仿真结果。

2020-07-07 17:28:03 10

10 介绍了一种读写器的编解码部分由FPGA来完成的设计方案,由FPGA负责前向链路的PIE编码和后向链路的FM0/miller 解码,且解码模块可对标签突发传来的数据立即检测并实施解码,实现了较快的解码速率。FPGA选用的是Altera公司的 EP1C3T100C6芯片。

2020-07-28 18:54:00 2

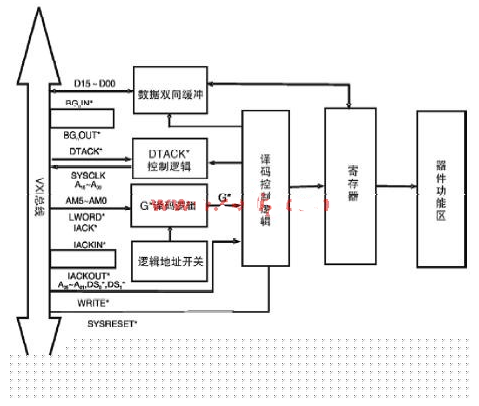

2 采用;另一种是利用中、小规模电路基PAL、GAL、CPLD和FPGA实现。通过利用FPGA实现模块与VXI总线接口的设计过程中,总结出一些通用的设计思路。

2020-07-27 18:11:22 1417

1417

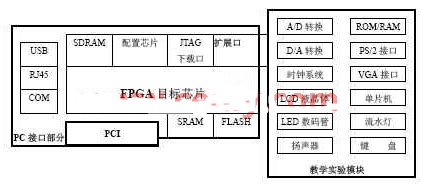

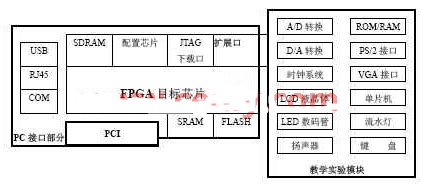

随着FPGA技术的不断发展和EDA工具软件的完善,在FPGA芯片上实现的各种复杂算法和构建SOPC系统成为研究的热点。在很多科研和教学开展的实验中,都需要为大规模FPGA芯片提供高速的计算机接口以及

2020-08-06 17:46:26 1534

1534

Programable Gate Array)的简称,两者的功能基本相同,编程等过程也基本相同(烧写文件不一样,但是是由软件自动产生的),只是芯片内部的实现原理和结构略有不同。 CPLD CPLD主要由可编程I

2020-09-25 14:56:33 14416

14416

在本辅导教材中,将重点讲解如何将一个设计项目物理地实现于FPGA 芯片中。我们将展示如何用手工的方法选择器件封装的引脚,并且把这些引脚用做电路的输入和输出信号,此外还将描述如何使用Quartus II 编程器模块把编译完的电路传送到所选择的FPGA芯片中。

2020-10-27 16:26:00 20

20 本文接续上一篇《FPGA杂记基础篇》,继续为大家分享IP例化和几个基于FPGA芯片实现的Demo工程。IP例化IP即是一个封装好的模块,集成在相应的开发环境里面,以安路的TD软件为例,不同系列的芯片集成了不同的IP模块,可以通过软件例化调用

2020-12-24 12:58:51 1803

1803 本文档的主要内容详细介绍的是FPGA模块化设计与AlteraHardCopy结构化ASIC。

2021-01-20 17:03:51 7

7 可编程门阵列)设计流程的基础上,从总体规划的角度提出了整个系统结构的设计思想,对JPEG解码器各部分算法进行了深入的研究,接着对各个模块的设计进行了详细的描述。采用了Verilog硬件描述语言对JPEG基本模式硬件解码器的各主要模块进行设计实现,并给出了功能仿真波形图及测试结果。

2021-01-29 15:27:00 13

13 研究了基于MIL—STD一1553B协议远程终端的FPGA硬件设计方法。给出了设计原理和实现流程,硬件结构主要由接口管理模块、位流控制模块、寄存器和内存管理模块、编码器和解码器组成,通过位流控制模块

2021-02-03 15:21:33 10

10 非常严格,因此,在设计解码器时采用了H.264解码专用芯片的设计方案。对一个大的设计项目,一般采用由顶向下(TOP-DOWM)的设计方法,把各功能模块划分为子模块。

2021-03-17 10:10:50 3277

3277

基于FPGA的UART模块设计与实现介绍说明。

2021-06-01 09:43:30 20

20 和通用性上都不理想。针对RICE算法中自适应熵编码的特点,设计了一种基于有限状态机和查找表的并行RICE解码结构,可在FPGA上完成8比特宽度的并行解码,解码速度最高可达176MB/s;同时,该解码结构适用于编码参数k变化的情况,具有很强的通用性。

2021-06-01 09:51:55 6

6 随着微电子工艺技术和IC设计技术的不断提高,整个系统都可集成在一个芯片上,而且系统芯片的复杂性越来越高。为了提高效率,复用以前的设计模块已经成为系统世馘 (SOC)设计的必上之路。SOC的实现基本上有两种方法,一种是用ASIC芯片实现,另一种是FPGA或PLD芯片实现。后一种实现也称为SOPC实现。

2021-06-11 15:55:26 2808

2808

FPGA_ASIC-S698MSoC芯片中EDAC模块的设计与实现(第四届星载电源技术学术研讨会)-该文档为FPGA_ASIC-S698MSoC芯片中EDAC模块的设计与实现总结文档,是一份很不错的参考资料,具有较高参考价值,感兴趣的可以下载看看………………

2021-09-15 11:05:19 6

6 FPGA-SoC芯片中EDAC模块的设计与实现(深圳市宇衡源电源技术)-该文档为FPGA-SoC芯片中EDAC模块的设计与实现简介文档,是一份还算不错的参考文档,感兴趣的可以下载看看,,,,,,,,,,,,,,,,,

2021-09-27 14:32:18 13

13 基于FPGA的IRIGBDC码解码(开关电源技术教程课后习题答案)-该文档为基于FPGA的IRIGBDC码解码讲解文档,是一份还算不错的参考文档,感兴趣的可以下载看看,,,,,,,,,,,,,,,,,

2021-09-27 15:16:58 22

22 这一要求,目前主流的 FPGA 芯片仍是基于 SRAM 工艺的查找表结构。 FPGA 芯片参数指标:包含可编程逻辑模块的数量、固定功能逻辑模块(如乘法器)的数目及存储器资源(如嵌入式 RAM)的大小。 在最底层的可配置逻辑模块(如片上的逻辑单元) 上,存在着基本的两

2022-11-19 13:45:02 1757

1757 FPGA 可编程的特性决定了其实现数字逻辑的结构不能像专用 ASIC 那样通过固定的逻辑门电路来完成,而只能采用一种可以重复配置的结构来实现, 而查找表(LUT)可以很好地满足这一要求,目前主流的 FPGA 芯片仍是基于 SRAM 工艺的查找表结构。

2022-11-29 10:10:57 5648

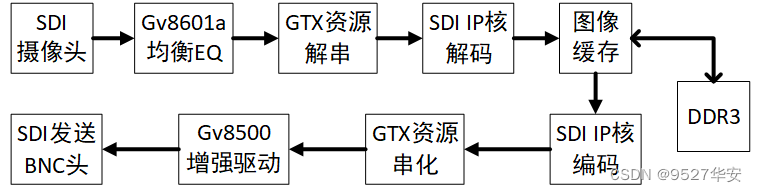

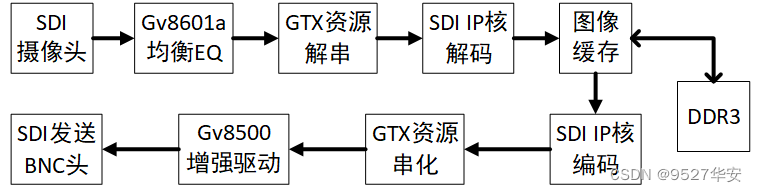

5648 一是使用专用编解码芯片,比如典型的接收器GS2971,发送器GS2972,优点是简单,比如GS2971接收器直接将SDI解码为并行的YCRCB,

2023-06-14 14:48:28 1828

1828

FPGA IP核(Intellectual Property core)是指在可编程逻辑器件(Field-Programmable Gate Array,FPGA)中使用的可复用的设计模块或功能片段。它们是预先编写好的硬件设计代码,可以在FPGA芯片上实现特定的功能。

2023-07-03 17:13:28 8969

8969 电子发烧友网站提供《密勒调制副载波编解码器的FPGA实现.pdf》资料免费下载

2023-10-26 11:10:21 1

1 FPGA芯片的工作原理主要基于其内部的可配置逻辑单元和连线资源。包括以下工作原理: 首先,FPGA内部包含可配置逻辑模块(CLB)、输出输入模块(IOB)和内部连线(Interconnect)三个

2024-03-14 17:17:51 3091

3091 电子标签芯片电路复杂而精细,其结构主要包括电源电路、时钟电路、解调器、编解码器、控制器、存储器和负载调制电路等模块

2024-03-25 11:45:33 2313

2313

遥控编解码芯片是无线遥控系统中的重要组成部分,它们负责编码和解码信号,以实现遥控功能。以下是一些常见的遥控编解码芯片: PT2262/PT2272 : PT2262是一种编码芯片,而PT2272

2024-09-30 14:21:10 4337

4337 概述: 利用FPGA实现AD芯片的时序,进一步实现与AD芯片数据的交互,主要熟悉FPGA对时序图的实现,掌握时序图转换Verilog硬件描述语言技巧后与其它芯片进行数据的交互也是类似的。 说明

2024-12-17 15:27:00 1613

1613

型的芯片,它们在结构、功能、应用场景等方面存在显著差异。 结构与灵活性 FPGA :FPGA是一种可编程逻辑器件,其内部由大量的可编程逻辑单元(CLB)、输入/输出模块(IOB)、可编程互连资源

2025-02-01 14:57:00 3322

3322

电子发烧友App

电子发烧友App

评论