完善资料让更多小伙伴认识你,还能领取20积分哦,立即完善>

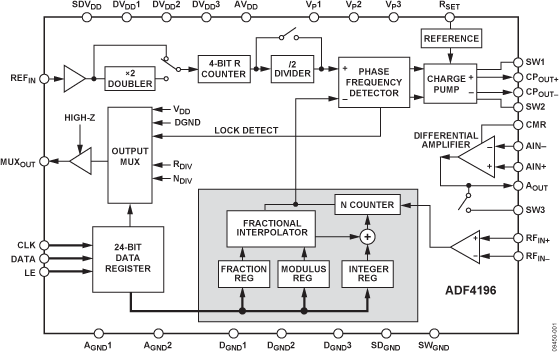

ADF4196由低噪声数字鉴频鉴相器(PFD)和精密差分电荷泵组成。还有一个差分放大器,用来将电荷泵的差分输出转换为外部电压控制振荡器(VCO)的单端电压。Σ-Δ型小数插值器与N分频器一起使用,能够实现可编程模数小数N分频。此外,4位参考(R)分频器和片内倍频器允许PFD输入端的参考信号(REFIN)频率为可选值。

如果频率合成器与外部环路滤波器和VCO一起使用,则可以实现完整的锁相环(PLL)。开关结构确保PLL能在GSM时隙保护期间内建立,而无需第二PLL及相关的隔离开关。与以前的乒乓式GSM PLL结构相比,这种结构能节省成本,降低复杂度,减小PCB面积,并减少屏蔽和特性测试工作。