MAX2880:高性能分数/整数-N PLL的全面解析

在当今的电子设计领域,频率合成器是众多系统中不可或缺的关键组件。MAX2880作为一款高性能的锁相环(PLL),能够在整数-N和分数-N模式下工作,为各种应用提供了精确且灵活的频率合成解决方案。本文将对MAX2880进行详细的介绍,包括其特性、应用、工作原理以及寄存器配置等方面。

文件下载:MAX2880.pdf

一、MAX2880概述

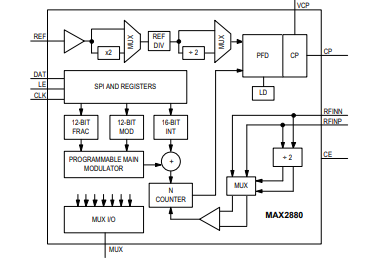

MAX2880是一款高性能的PLL,与外部参考振荡器、环路滤波器和压控振荡器(VCO)结合,可形成超低噪声和低杂散的频率合成器,能够接受高达12.4GHz的射频输入频率。它由高频低噪声鉴相器(PFD)、精密电荷泵、10位可编程参考计数器、16位整数N计数器和12位可变模数分数调制器组成。该器件通过3线串行接口进行控制,兼容1.8V控制逻辑,采用无铅、符合RoHS标准的20引脚TQFN封装,工作温度范围为 -40°C至 +85°C。

二、应用领域

MAX2880具有广泛的应用领域,包括:

- 微波点对点系统:为微波通信提供稳定的频率源,确保信号的准确传输。

- 无线基础设施:在基站等无线设备中,为射频信号的处理提供精确的频率合成。

- 卫星通信:满足卫星通信对高稳定性和低噪声频率源的需求。

- 测试与测量:为测试设备提供准确的频率参考,保证测量结果的准确性。

- 射频DAC和ADC时钟:为数模和模数转换器提供合适的时钟信号。

三、特性与优势

3.1 工作模式

具备整数和分数-N两种模式,可根据不同的应用需求进行灵活选择。

3.2 宽带射频输入

支持250MHz至12.4GHz的宽带射频输入,适应多种频率范围的应用。

3.3 低噪声性能

- 归一化带内噪声地板:整数模式下为 -229dBc/Hz,分数模式下为 -227dBc/Hz。

- 低噪声鉴相器:分数模式下为125MHz,整数模式下为140MHz。

3.4 宽输入灵敏度

输入灵敏度范围为 -10dBm至 +5dBm,能够适应不同强度的输入信号。

3.5 其他特性

- 参考频率高达210MHz。

- 工作电源范围为 +2.8V至 +3.6V。

- 具备周期滑差减少和快速锁定功能,提高锁定速度和稳定性。

- 支持软件和硬件关机功能,降低功耗。

- 软件锁定检测功能,方便监测锁定状态。

- 片上温度传感器,可实时监测芯片温度。

- 兼容 +1.8V控制逻辑,便于与其他电路集成。

- 支持相位调整功能,可对射频输出相位进行精确调整。

四、电气特性

4.1 绝对最大额定值

- 电源电压(VCC_): -0.3V至 +3.9V

- 电荷泵电源(VCP): -0.3V至 +5.8V

- 其他引脚电压: -0.3V至 (VCC_ + 0.3V)

- 射频输入功率: +10dBm

4.2 直流电气特性

- 电源电压(VCC_):2.8V至3.6V

- 电荷泵电源(VCP):VCC_至5.5V

- 电源电流:不同条件下有所不同

4.3 交流电气特性

- 输入频率:250MHz至12.4GHz

- 输入功率: -10dBm至 +5dBm

- 参考输入频率范围:10MHz至210MHz

五、引脚描述

MAX2880共有20个引脚,各引脚功能如下:

- GND_CP:电荷泵接地,连接到电路板地,而非焊盘。

- GND_SD:Σ-Δ调制器接地,连接到电路板地,而非焊盘。

- GND_PLL:PLL接地,连接到电路板地,而非焊盘。

- RFINP:预分频器的正射频输入,如不使用,通过电容交流接地。

- RFINN:预分频器的负射频输入,通过耦合电容连接到VCO输出。

- VCC_PLL:PLL电源,尽可能靠近引脚放置去耦电容。

- VCC_REF:参考电源,尽可能靠近引脚放置去耦电容。

- REF:参考频率输入,为高阻抗输入,标称偏置电压为VCC_REF/2,交流耦合到参考信号。 9、10 GND:接地,连接到电路板地,而非焊盘。

- CE:芯片使能,逻辑低电平使器件掉电。

- CLK:串行时钟输入,数据在CLK线的上升沿锁存到32位移位寄存器。

- DATA:串行数据输入,串行数据先加载最高有效位(MSB),3个最低有效位(LSB)标识寄存器地址。

- LE:加载使能输入,当LE变为高电平时,移位寄存器中存储的数据加载到相应的寄存器。

- MUX:复用I/O,具体功能可参考相关表格。

- VCC_RF:射频电源,尽可能靠近引脚放置去耦电容。

- VCC_SD:Σ-Δ调制器电源,尽可能靠近引脚放置去耦电容。

- VCP:电荷泵电源,尽可能靠近引脚放置去耦电容。

- RSET:电荷泵电流范围输入,连接外部电阻到地以设置最小电荷泵电流。

- CP:电荷泵输出,连接到外部环路滤波器输入。

- EP:外露焊盘,连接到电路板地。

六、工作原理

6.1 参考输入

参考输入级配置为具有从输入到输出的并联电阻的CMOS反相器。在关机模式下,该输入设置为高阻抗,以防止对参考源的负载影响。参考输入信号路径还包括可选的x2和÷2模块,可根据需要调整参考输入频率。

6.2 计数器关系

- 鉴相器频率(fPFD):由外部参考输入频率(fREF)、参考倍频器模式(DBR)、参考二分频模式(RDIV2)和可编程参考计数器值(R)共同决定,计算公式为fPFD = fREF x [(1 + DBR)/(R x (1 + RDIV2))]。

- VCO频率(fVCO):由鉴相器频率(fPFD)、N计数器值(N)、分数模数(M)、分数除法值(F)和射频输入预分频器控制(PRE)决定,计算公式为fVCO = fPFD x (N + F/M) x (PRE + 1)。

6.3 整数-N/分数-N模式

- 整数-N模式:通过设置寄存器3的bit 10(INT)为1来选择,同时需要设置寄存器3的bit 9(LDF)为1以设置锁定检测为整数-N模式。

- 分数-N模式:通过设置寄存器3的bit 10(INT)为0来选择,同时设置寄存器3的bit 9(LDF)为0以设置分数-N锁定检测模式。当分数除法值F = 0时,若寄存器4的bit 29(F01)为1,器件可自动切换到整数-N模式,以避免不必要的杂散。

6.4 鉴相器和电荷泵

电荷泵电流由引脚RSET到地的电阻值和寄存器2的bits 27:24(CP)的值决定,计算公式为ICP = 1.63/RSET x (1 + CP)。在分数-N模式下,用户可调整电荷泵线性度(CPL)位以优化带内噪声和杂散水平;在整数-N模式下,CPL必须设置为0。若需要在整数-N模式下实现更低的噪声操作,可设置电荷泵输出钳位位(CPOC)为1以防止泄漏电流进入环路滤波器;在分数-N模式下,CPOC设置为0。电荷泵输出可通过设置寄存器3的bit 4(TRI)为1进入高阻抗模式,设置为0时为正常模式。鉴相器极性可根据环路滤波器拓扑进行调整。

6.5 MUX和锁定检测

MUX是一个多用途测试输出,用于观察MAX2880的各种内部功能,也可配置为串行数据输出。MUX位(寄存器0的bits 30:27)用于选择所需的MUX信号。数字锁定检测取决于合成器的模式,在分数-N模式下设置LDF = 0,在整数-N模式下设置LDF = 1。

6.6 周期滑差减少和快速锁定

- 周期滑差减少:通过设置寄存器2的bit 28(CSR)为1来启用,在此模式下,电荷泵必须设置为最小值。

- 快速锁定:通过设置寄存器4的bits 20:19(CDM)为01来启用,同时需要将电荷泵电流设置为CP = 0000,MUX位配置为1100,并将环路滤波器的并联电阻部分分割为两部分。快速锁定激活后,电荷泵自动增加到最大值,并联环路滤波器电阻减小到总电阻的1/4。

6.7 射频输入

差分射频输入连接到高阻抗输入缓冲器,驱动一个多路复用器以选择两个射频输入频率范围:250MHz至6.2GHz和6.2GHz至12.4GHz。当射频输入频率为250MHz至6.2GHz时,通过设置PRE为0绕过固定二分频预分频器;当射频输入频率为6.2GHz至12.4GHz时,通过设置PRE为1选择固定二分频路径。支持的输入功率范围为 -10dBm至 +5dBm。对于单端操作,通过100pF电容将未使用的射频输入端接地。

6.8 相位调整

锁定后,射频输出的相位可以以P(寄存器1的bits 14:3)/M(寄存器2的bits 14:3)x 360°的增量进行改变。在对齐多个器件的相位时,可通过特定的步骤进行操作。

6.9 分数模式

MAX2880为Σ-Δ调制器提供三种模式:低噪声模式以牺牲杂散为代价提供较低的带内噪声,低杂散模式以牺牲噪声为代价提供较低的杂散。通过设置寄存器2的bits 30:29(SDN)来选择不同的模式。

6.10 温度传感器

器件配备了片上温度传感器和7位ADC。通过特定的步骤可以读取温度传感器的数字化输出,并将其转换为实际温度。

七、寄存器配置

MAX2880的工作模式通过5个读写寄存器和1个只读寄存器进行控制。寄存器编程顺序应为地址0x04、0x03、0x02、0x01和0x00。部分位为双缓冲,以同时更新设置。各寄存器的详细位定义可参考相关表格。

八、总结

MAX2880作为一款高性能的分数/整数-N PLL,具有丰富的功能和优异的性能,能够满足多种应用领域的需求。通过合理配置寄存器和外部电路,工程师可以充分发挥其优势,实现精确的频率合成和信号处理。在实际设计中,需要根据具体的应用场景和要求,仔细选择工作模式、调整参数,以达到最佳的性能表现。你在使用MAX2880的过程中遇到过哪些挑战呢?欢迎在评论区分享你的经验和见解。

-

频率合成器

+关注

关注

5文章

368浏览量

33875 -

pll

+关注

关注

6文章

989浏览量

138360

发布评论请先 登录

探索MAX2871:超宽带PLL频率合成器的卓越性能与应用

MAX2870:23.5MHz 至 6000MHz 分数/整数 N 合成器/VCO 深度解析

ADF4252双分数N/整数N频率合成器技术剖析

ADF4153A 分数 N 频率合成器的全面解析与应用

深入剖析ADF4155:强大的整数 - N/分数 - N PLL合成器

ADF4150:高性能分数/整数N锁相环合成器的设计与应用

高电压分数N/整数N PLL合成器ADF4150HV技术解析

ADF4152HV:高性能分数/整数N PLL合成器的技术剖析

MAX520/MAX521:高性能2线串行8位DAC的全面解析

深入剖析LMX2470:高性能Delta - Sigma分数N PLL的全方位解读

剖析TRF3761系列整数 - N PLL频率合成器:优势、应用与设计要点

LMX2492/LMX2492 - Q1:14 GHz低噪声分数N PLL的全面解析

集成整数 N 分频 PLL 和 VCO 的 350-5000 MHz 宽带接收混频器 skyworksinc

MAX2870 23.5MHz至6000MHz分数/整数N分频合成器/VCO技术手册

MAX2880:高性能分数/整数-N PLL的全面解析

MAX2880:高性能分数/整数-N PLL的全面解析

评论