1.USB硬件资源介绍1.1两种USB模式EASYEAINano-TB开发板支持2种USB工作模式:默认模式:USB资源默认在设备树被配置成【2路USB2.0HOST】和【ADB】。USB3.0模式

2026-01-01 09:30:00 3707

3707

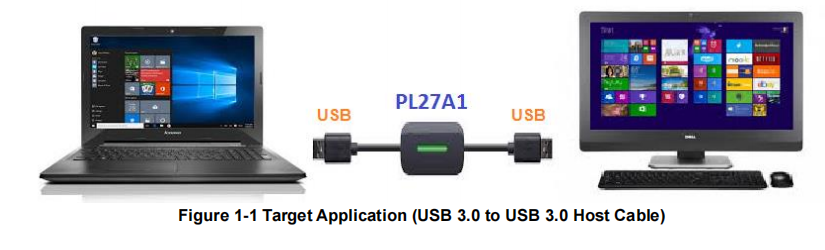

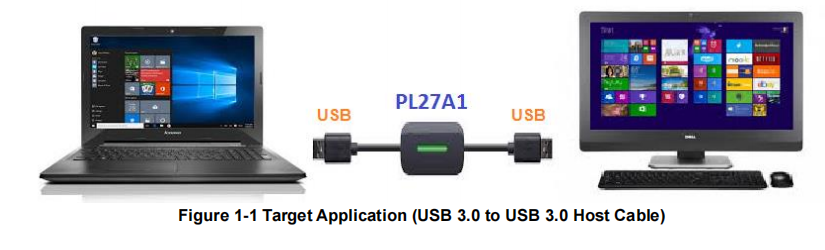

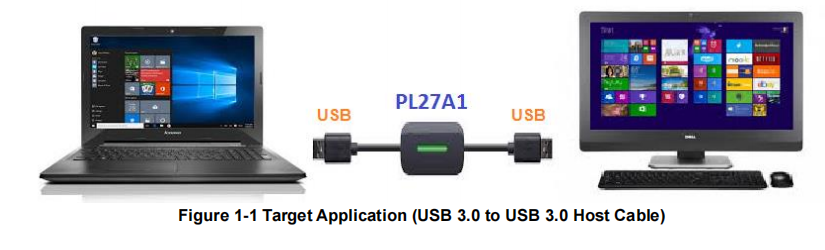

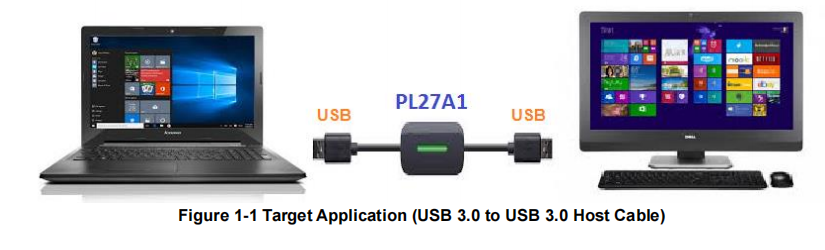

PL27A1是一款专为USB主机间数据传输设计的单芯片SuperSpeed USB 3.0主机间桥接控制器。SuperSpeed USB的带宽最高可达5Gbps ,性能比Hi-Speed USB

2025-12-27 13:48:57 1

1 高达5Gbps,性能比高速USB 2.0(480Mbps)提高了10倍。超高速 USB向下兼容,可与所有USB3.0/USB2.0/USB1.1主机、设备和集线器互操作。PL27A1纯数据对拷方案

2025-12-16 16:02:49

在嵌入式系统设计中,MCU单片机的性能直接决定了终端产品的功能高度。以英尚微电子代理的沁恒CH569为例,这款MCU单片机凭借其高度集成的设计,为移动存储与数据安全领域带来了创新解决方案,尤其在USB3.0超高速U盘及蓝牙锁功能应用中表现突出。

2025-12-15 15:23:21 184

184 旺玖PL27A1是一款USB 3.0主机到主机桥接控制器芯片,专为高速数据传输设计。它支持USB 3.0协议,理论传输速率可达5Gbps,向下兼容USB 2.0和1.1标准。该芯片常用于USB对拷线方案中,实现两台电脑之间的直接数据传输、键鼠共享等功能,无需额外软件驱动即可即插即用。

2025-12-15 00:16:58 538

538

力不从心。在此背景下,基于USB3.0和PCIe接口的工业图像采集卡应运而生,并凭借其高速的数据传输能力、广阔的兼容性以及便捷的部署方式,在各个领域展现出强大的优势

2025-12-03 15:31:17 584

584

Cypress赛普拉斯512Kbit FRAM凭借微秒级写入、10^14次擦写寿命及151年数据保留,为车载黑匣子EDR提供高可靠数据存储。其-40℃~105℃车规级工作范围确保碰撞数据完整记录,满足汽车安全法规严苛要求。

2025-12-01 09:47:00 245

245

;

}

/**

* @brief写字节函数

* @paramrb_ptr 缓冲区结构体地址,data 写入数据

* @retvalNone

* @noticeNone

*/

void

2025-12-01 08:16:15

默认缓冲区配置

CW32L052的UART模块支持硬件FIFO(通常为16字节),但HAL库或用户代码需手动管理接收缓冲区。若未显式分配足够大的软件缓冲区,可能导致数据溢出。

HAL库缓冲区管理

2025-11-24 06:40:59

PL27A1是一款SuperSpeed USB 3.0主机间桥接控制器芯片,支持5Gbps高速数据传输,兼容USB3.0/2.0/1.1规范。其内置多系统驱动程序和RNDIS协议,可连接两台

2025-11-20 10:59:27 137

137

。1.3.2.2 主动刷新内核缓冲 有些场景需要立刻将数据写入磁盘设备,此时就需要使用特定的函数(fsync、fdatasync、sync)去刷新内核缓冲区的方法。1.3.2.3 标准IO缓冲 标准I

2025-11-19 16:24:10

硬件消抖是通过电路设计消除机械开关(如按键、继电器等)在闭合或断开时产生的抖动信号。以下是常见硬件消抖方案及其元件参数计算方法:

1. RC滤波消抖(低通滤波)

原理:利用电容的充放电特性,延缓

2025-11-19 06:31:59

)。对于输出流,当fwrite写入文件的数据填满缓冲区时,才调用系统I/O(write)将stdio缓冲区中的数据刷入内核缓冲区;对于输入流,每次读取stdio缓冲区大小的字节数据。普通磁盘上的常规

2025-11-14 09:02:30

台湾旺久PL27a1是一款超高速USB 3.0主机到主机桥接控制器芯片,主要用于设计USB3.0数据对拷方案的设计开发,来实现两台电脑之间数据之前的对拷,可以随意编辑文件、拖拽文件且共享一套鼠键设备,还可以定制画中画等功能。

2025-11-12 17:09:51 618

618

PL27A1是一款专为USB主机间数据传输设计的单芯片SuperSpeed USB 3.0主机间桥接控制器。SuperSpeed USB的带宽最高可达5Gbps ,性能比Hi-Speed USB

2025-11-09 16:59:22 1233

1233

电子发烧友网站提供《PL27A1超高速USB3.0数据对拷线芯片资料.pdf》资料免费下载

2025-10-16 16:49:53 0

0 模块深度测评:高频率数据传输的缓冲区陷阱与优化方案

本文记录了在实际项目中使用620 LoRa模块时遇到的一个隐蔽却关键的问题,以及完整的排查和解决方案。

问题现象:高频率发送数据时的异常行为

2025-10-15 19:29:03

在前面的内容中,我们了解了负载开关IC的基本定义、独特优点、实用功能及其操作,今天作为【负载开关IC】系列的最后一篇内容,芝子将带着大家了解一下负载开关IC数据表中相关术语和功率损耗计算方法。

2025-10-15 16:54:50 1406

1406

使用ART-PI2板子串口1DMA接收数据,buf的大小为64,只能累计接收64字节,如果扩大到256字节,也只能累计接受到256字节。数据及时读取,缓冲区应该是没有溢出的,应用程序移到F4的板子是正常,求解

2025-09-12 07:56:31

代码在运行的时候,只有lvgl线程用于刷新,另一个线程只有一个串口打印。

当运行一段时间后,发现,程序会在LVGl中,lv_refr.c这个库下面第625行代码,

在这一直判断,看介绍说是在等待释放缓冲区,求大神给个思路

2025-09-09 07:28:40

FS:多达 25 个可配置端点,1.5KB 缓冲区

USB 2.0 HS:多达 12 个可配置端点,4KB 缓冲区

丰富的示例代码

广泛的包装选项:包括紧凑型 QFN48 (5x5)

新唐的USB

2025-09-05 06:51:33

该文章介绍USB3.0的布局布线要求及走线规范

2025-08-19 16:50:39 2

2 需≥v1.4.0)。

调整缓冲区大小:在分析仪软件中增大接收缓冲区(如从1MB增至10MB),避免数据溢出。

四、高级调试技巧:精准定位干扰源1. 分段隔离法

步骤:

断开DUT与主机的连接,仅用

2025-08-01 15:00:38

在使用USB设备时候,除去USB 内部的缓冲区,是否有一些简单方法,能够将数据不通过USB缓冲区,而是通过SPI发送给下位机。

2025-08-01 08:27:09

我参考 USB3.0 官方 API 文档编写了一段代码,旨在实现设备的循环回送功能,即通过 Bulk Out 端点发送数据,再由 Bulk In 端点接收数据。代码完整地涵盖了创建事件对象、设置

2025-07-28 07:26:14

我需要调用 USBDevice->BulkInEndPt->XferData 来获取 USB IN 缓冲区的数据大小(按字节),但这样做会导致数据被传递到主机。目前,我

2025-07-28 06:52:41

赛普拉斯2 Mbit FRAM FM25V20A-DG以40 MHz SPI总线、10¹²次擦写寿命和100 krad(Si)抗辐射能力,取代呼吸机中EEPROM与SRAM加电池的传统方案,为智能生命支持系统提供原子级可靠的数据存储基石。

2025-07-24 11:25:44 520

520

调用 USBDevice->BulkInEndPt->XferData 可获取 USB IN 缓冲区的数据大小(按字节),但数据会被传至主机。目前,我先要判断 USB

2025-07-23 08:21:48

本次演示用的是USB3.0芯片-CYPRESS CYUSB3014(下称 FX3),该芯片是标准的USB3.0 PHY,可以大大简化使用USB通信时FPGA的设计,主需要使用状态机进行FIFO的读写

2025-07-21 16:20:22 6360

6360

:

1.哪个函数可以读取USB端口缓冲区数据的实际字节数?

2. 哪个函数可以读取 GPIF II 上 DMA 缓冲区数据的实际字节数?

3、GPIF II 接口的标志信号会受 USB 端口状态的影响吗?会怎样,然后又会产生怎样的影响?

2025-07-21 07:27:08

该芯片是CYUSB3014。工作模式下:GPIF II接口作为生产者,USB接口作为消费者。数据从外部FPGA进入GPIF II接口,然后通过USB 3.0接口发送到计算机软件。

请问:

1

2025-07-18 07:58:16

USB缓冲区中的内容满了之后,是否有标志位进行反馈。

2025-07-17 07:13:24

在使用USB软件获取数据是,下位机给我发送了13个32位数据到USB IN缓冲区,为什么我调用API函数想要第一次取1个32位数据,取完之后再取12位数据,程序会卡死。

2025-07-16 08:12:04

我想要使用usbdStatus.h来对usb设备运行的状态进行判断。我预期是希望通过这个函数来进行USB缓冲区是否有数的判断(图1),但函数的返回值只有SUCCESS(),我无法进行判断。

2025-07-15 07:32:18

通常具有:

1x 或 2x HID 接口

视频输入( BULK ,GPIF 具有多个16KB缓冲区大小)

音频输入( ISO ,1ms,GPIF 具有多个192B缓冲区大小)

音频输出( ISO

2025-07-15 07:08:51

USB3.0视频采集模块通过LVDS接口连接机芯,自动识别机芯高清视频格式。支持720P,1080I,1080P各种帧率,让SONY FCB一体化摄像机芯所拍摄图像即刻显示在电脑屏幕中。

2025-07-09 10:22:36 717

717

=73882cd30422e7942d630b1024b22055

一、功能简介:

1转7的USB3.0 HUB(上行5G,1转7路USB3.0);

电流功率可视化(电流采样,功率计算,实时更新显示,并可上传电脑,后期可设计升级上位机);

通道电源独立可控(可

2025-06-28 00:23:02

索尼FCB-EV9520L搭配USB3.0视频采集模块,以其卓越的性能、便捷的操作和广泛的应用,成为了各行业视频传输的理想选择。它不仅为用户提供了高效、稳定、高质量的视频传输解决方案,还为各行业

2025-06-23 13:52:34 533

533

和 ttl 级) ,从300波特到1兆波特(rs232)。

•256字节的接收缓冲区和128字节的传输缓冲区利用缓冲平滑技术,以允许高数据吞吐量。

•在大多数情况下,ftdi 免版税的 vcp 和 d2xx 驱动程序取消了 usb 驱动程序开发的要求。

2025-06-23 10:12:19

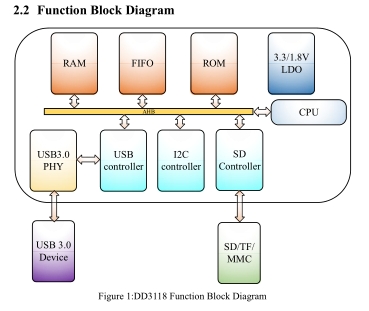

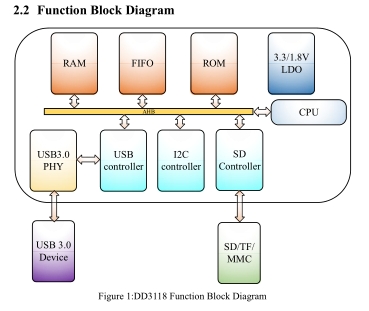

抖胆科技推出的DD3118是一款无晶振的USB3.0 Dua/Single LUN卡读取器控制器,采用40纳米低功耗技术制造的高性能、高集成度读卡器控制芯片可支持各种类型的存储卡,如Secure

2025-06-19 15:52:06 865

865

我在测试视频通话时 发现丢帧特别严重 进行了一些列的排查 发现socket本身似乎有问题

通过测试代码发现了大量的缓冲区溢出我尝试换了不同的服务器

我还分别测试了wifi网卡和4G网卡 全都这样

2025-06-19 06:34:51

作为读卡器的核心功能模块,DD3118支持USB3.0、SD3.0和eMMC4.5标准协议,能够稳定访问存储在内存卡中的数据,并实现数据传 输功能。

创惟GL3213S与国产DD3118的bom对比

2025-06-11 15:43:34

)%MAX_BUFFER_LEN;//防止尾部越界

uart_queue.len++;//环形缓冲区中数据长度

return QUEUE_SUCCESS;

}

static QUEUE queue_read(uint8_t

2025-06-11 10:24:45

type-c正接的时候可以正常识别usb2.0、usb3.0。

APP_EVT_TYPEC_ATTACH_WAIT->APP_EVT_TYPEC_ATTACH->

2025-06-03 09:19:53

我们使用CYUSB3014作为USB3.0数据传输方案,目前处于试产阶段。试产过程中偶尔出现板卡连接至PC后,USB3.0无法识别的情况。

固件使用的官方SlaveFifoSync固件。问题板卡上电

2025-05-29 06:48:21

二进制文件转换实用程序

版权所有 (c) 2012-2013,赛普拉斯半导体公司。

错误:输入图像太大,无法输出文件大小。Addr = 0xe000,len = 0x 20。

我不知道错误在哪里,如果有人 CAN 给我一个完美的示例项目,谢谢。

2025-05-29 06:35:01

抖胆DD3118高性价比USB3.0读卡器芯片,替代GL3213S,DD3118无需晶体振荡器;采用40nm低功耗工艺制造,专为读卡器设计。它支持USB 3.0、SD 3.0和eMMC 4.5标准

2025-05-27 17:28:04

CYPD7191-40LDXS? 它似乎无法选择CYPD7191-40LDXS 器件。

Q3) 还是可以使用赛普拉斯编程器选择器件?

Q4)是否使用 ModusToolBox 为 CYPD7191-40LDXS 开发 FW?

Q5)是否有任何与上述 CCG7S 有关的计划编制材料?

请回答每个问题(Q1 ~ Q5)

2025-05-23 06:09:28

如何用QT开发一个USB3.0上位机

2025-05-21 06:54:16

我们在使用CYPD4266+TUSB1064 实现USB3.0 UFP 2lane +DP 2lane 传输,

1.当DP mode Parameters ->Modes

2025-05-21 06:15:45

CANFD模块的缓冲区机制,帮助工程师更高效地管理CAN消息,提高系统性能。(下面的内容主要涉及RZN2L CANFD外设手册的解读,篇幅较长,感兴趣的读者可以收藏,以备日后不时之需)

2025-05-20 13:53:22 1062

1062

在 FX3 被枚举为 \"赛普拉斯 FX3 引导加载器设备 \"后,如果我重启电脑,该设备会显示为未知设备。 为什么?

2025-05-20 07:22:35

你好,我们使用的是具有 USB 启动模式的赛普拉斯 3014 USB 芯片。 我的电脑可以在设备管理器中检测到 3014,但 USB 芯片无法与板上的 FPGA 通信。 电源电压似乎正常。 3014

2025-05-20 07:09:47

在工业自动化、智能交通、机器人等领域,CANFD(CAN with Flexible Data-Rate)技术正逐步取代传统CAN,以适应更高的数据速率和更复杂的通信需求。本文将深入解析RZ/N2L CANFD模块的缓冲区机制,帮助工程师更高效地管理CAN消息,提高系统性能。

2025-05-19 14:13:52 1231

1231

在工业自动化、智能交通、机器人等领域,CANFD(CAN with Flexible Data-Rate)技术正逐步取代传统CAN,以适应更高的数据速率和更复杂的通信需求。本文将深入解析RZ/N2L CANFD模块的缓冲区机制,帮助工程师更高效地管理CAN消息,提高系统性能。

2025-05-19 14:10:50 1053

1053

我目前正在使用配置2048x1200 RAW10 30FPS测试Denebola RDK板,并且遇到了有关帧大小和数据包大小的问题。 以下是详细信息:

DMA 缓冲区大小:0x5FF0

输出日志

2025-05-19 08:09:49

运行 ubuntu 23.10。

在赛普拉斯评估板CY4603上(请注意,这是一个 3.0 集线器,但来自同一系列)我没有收到这些错误。

我觉得奇怪的是,我在使用评估板时没有遇到这个错误。 我是否在集线器上连接了错误的东西?这是一个已知问题吗?有没有什么解决办法?

2025-05-19 07:32:42

使用cyusb.dll(NET), USBDeviceList枚举USB设备,可以正常访问,当我用外在部件将其从USB3.0强制到USB2.0后如何高效重新打开设备,重复调用USBDeviceList,会出现效率低下

2025-05-19 06:15:30

我想使用 Hailo-15 SoC USB3.0 接口将 OV5647 传感器通过 CYUSB3065 连接到 SoM。

是否可以将 CYUSB3065 与 Hailo-15 SoC 作为 USB

2025-05-16 08:10:33

FX3_Programmers_Manual 文档的第 10 章提到“每个缓冲区的缓冲区切换开销为 550 - 900 ns”。

Getting_Started_with_EZ-USB_FX3 文档

2025-05-16 07:51:28

2 次传输,再次卡住的时间更短,然后顺利传输数据。

Buffers working until they get stuck缓冲器在卡住之前一直在工作

前两个缓冲区的标志 A(上)和 B(下),然后

2025-05-16 07:18:39

我正在使用CX3065来捕获图像,我发现有些USB3.0接口无法找到分辨率,现在我尝试了几台笔记本电脑,我发现USB3.0接口提供关机充电,它可以识别CX3设备分辨率。 我保存了是或否的USB接口图片。 我猜想改变 CX3 防火墙的设置可以解决这个问题。 我需要一些帮助,非常感谢!

2025-05-15 08:26:37

调试CX3 USB3.0兼容USB2.0出图的问题,我们在调试一款sensor,需要输出全分辨率1124x1364,USB3.0调试可以出图,但是在调试USB2.0时,无法调试出图,在裁剪分辨率之后

2025-05-15 08:18:41

。

-----------------------------hextoi2c 命令--------------------------------------

C:赛普拉斯USBCY3684_EZ-USB_FX2LP_DVK1.1Binhex2bix -i -f 0xC2 -o cmosRdSlv.iic cmosRdSlv.hex

2025-05-13 07:49:16

,它可以很好地工作,但是使用 USB3.0 时,会出现错误,设备会挂起并在看门狗超时后重置,我不知道原因。

2025-05-13 07:05:34

的 PC 请求读取时出现错误,然后我尝试从 FPGA 连续发送到 PC。

最后,我意识到 PC(主机)只能读取 1024 个字节。 非常糟糕,如何将小于1024字节的缓冲区从FPGA发送到PC?

2025-05-09 08:18:20

_EP_BULK;

epCfg.burstLen = 16;

epCfg.流 = 0;

epCfg.pckt大小 = 1024;

/* 从属 FIFO P_2_U 通道缓冲区计数 */

#定义

2025-05-09 07:31:04

在automaster和autoslave项目中如何配置参数,来满足usb3.0和usb2.0的数据传输,因为一边检测到是usb3.0, 一边是usb2.0。

2025-05-09 06:26:56

请问我的DMA缓冲区设置为48K,如果没有写满48K,数据会自动被发送出去吗。2.有没有清空DMA缓冲区的函数,我直接调用CyU3PUsbFlushEp()不起作用。

2025-05-09 06:21:42

我们的SoM iMX8提供一个USB3.0 接口。 但在我们的应用中我们需要一个完整的USB3.0 端口以及USB2.0端口。 在路由 USB3.0 的同时,是否可以与 USB2.0 集线器

2025-05-08 07:38:23

时,它可以正确连接并识别 FX3。

以下是我连接到 USB3.0 端口时的打印内容

[370.996088] USB 1-1: 使用 xhci-hcd 新建高速USB设备编号 4

2025-05-08 07:30:17

状态;

CY_DATA_BUFFER 读取缓冲区;

读取缓冲区.缓冲区 = 读取数据;

读取缓冲区.长度 = 读取数据长度;

读取缓冲区.传输计数 = 0;

//0x071e3c18

状态

2025-05-08 07:01:47

我正在设计一个系统,通过 USB 3.0 将图片数据从 PC 下载到 FPGA,然后 FPGA 在 LCD 上显示图像。 我需要一种方法让 FPGA 将状态(下载了多少图像以及 LCD 上显示了

2025-05-08 06:56:58

和数量改为34kb,6。rgb24 1080p@60fps无法出图?

dma缓冲区大小和数量是否有什么说法吗?需要对应?

fx3可用的dma大小为多少?

根据usbcap抓取数据以及demo来看

2025-05-06 13:42:13

我开发了一款CYUSB3014硬件,但是我在烧录了syncfifo示例代码后,板卡只能被识别为USB2.0设备。我确认我的线材是支持USB3.0的,并且我检查了19.2Mhz的晶振工作正常

2025-04-30 07:24:54

USB3.0工业采集卡是一种专为工业环境设计的高速数据采集设备,主要用于实时采集传感器、摄像头、模拟信号(如电压、电流)或数字信号(如开关量、脉冲信号)等数据,并通过USB3.0接口传输至计算机进行

2025-04-08 15:21:01 972

972

();}审核后emWin 多缓冲 - SEGGER Wiki,我认为 “GUI_MULTIBUF_Begin()” 在从前到后复制帧缓冲区方面效率不高。

有没有办法优化 “GUI_MULTIBUF_Begin()” 或使其使用 i.MX RT 的功能来更快地复制帧缓冲区?

2025-04-03 07:21:08

我正在使用带有 epdc 显示子卡 (IMXEBOOKDC5) 的 IMX8ULP EVK。使用 Linux 映像引导后,epdc 显示无法使用帧缓冲区进行更新。当检查显示 pmic 的电源使能引脚

2025-04-01 06:41:26

ioctl VIDIOC_QUERYBUF 获取 4 个缓冲区,然后像这样 mmap 它们:

void *data = mmap( NULL, buffer.m.planes[0].length

2025-03-28 07:28:19

解析其原理、特点、使用方法及注意事项,助你进阶掌握这一关键技术。

一、流缓冲区是什么?为什么需要它?

流缓冲区是FreeRTOS中基于环形缓冲区实现的字节流传输机制,其核心作用是动态管理数据的读写

2025-03-24 11:37:29

捷美USB3.2移动硬盘拷贝机专为大规模硬盘复制设计,一次可同时复制40颗硬盘,仅需3.5小时完成,比传统计算机拷贝快500%。采用一键式操作,无需人工监控,降低人力成本。内建bit to bit比对功能,确保数据完整性和安全性。独立运行,开机即用,无需计算机或额外软件,适合企业高效数据管理。

2025-03-18 17:16:57 1267

1267

我根据L9663 Datasheet这个手册,想使用这个配置“通过带有上行数据缓冲区的SPI触发。微控制器发送相应的SPI命令以发送同步脉冲。然后,同步脉冲触发发生器根据上行数据缓冲区中的值在内部

2025-03-13 08:15:12

本期来认识软件漏洞的“常客”——缓冲区溢出,C/C++开发者尤其要注意!全面了解该漏洞的成因、类型、常见示例,以及如何借助Klocwork、Helix QAC等SAST工具进行防护。

2025-03-04 16:39:10 1929

1929

我利用DLP3010evm的displayboard和自己做的一块底板连接。

去除了底板上的MSP430,直接将赛普拉斯芯片与dlpc连接。赛普拉斯芯片配置和evm一样。

可以烧录固件,但是GUI

2025-02-27 08:07:54

USB3.0规范

2025-02-25 17:43:07 1

1 4K USB3.0编码采集模块以其高速传输、双4K输出接口设计、强大的兼容性和控制功能,成为了视频采集领域的新星。它不仅满足了当前市场对4K超高清视频采集的需求,还以集成化的特点,为用户提供了更高性价比的解决方案。

2025-02-21 16:29:14 1038

1038 VL817-Q7S是由VIA Labs(威锋电子)设计生产的一款现代USB 3.1 Gen 1集线器控制器。它主要用于将一路USB3.0/3.1信号扩展为多个接口,使得设备如手机或笔记本电脑能够通过

2025-02-15 10:40:48 2306

2306

SAFERTOS中的流缓冲区(Stream buffer)机制,可以实现任务到任务或中断到任务之间的通信。字节流是由发送方写入缓冲区,接收方读取缓冲区数据。流缓冲区作为队列的轻量级级替代方案,适合单读单写场景,写者在流缓冲区中放置任意数量的字节,读者读取任意数量的字节。

2025-02-14 11:33:16 1074

1074

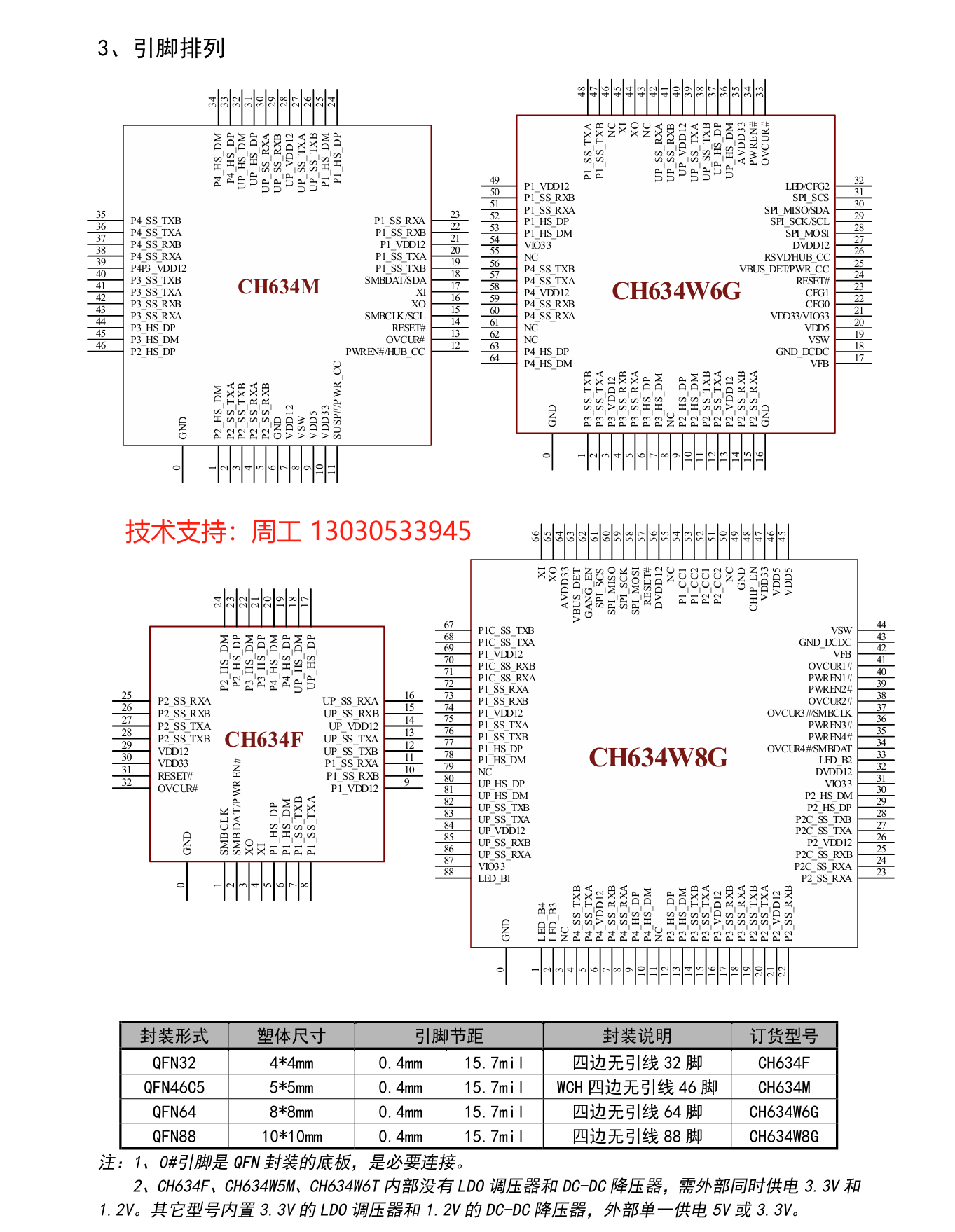

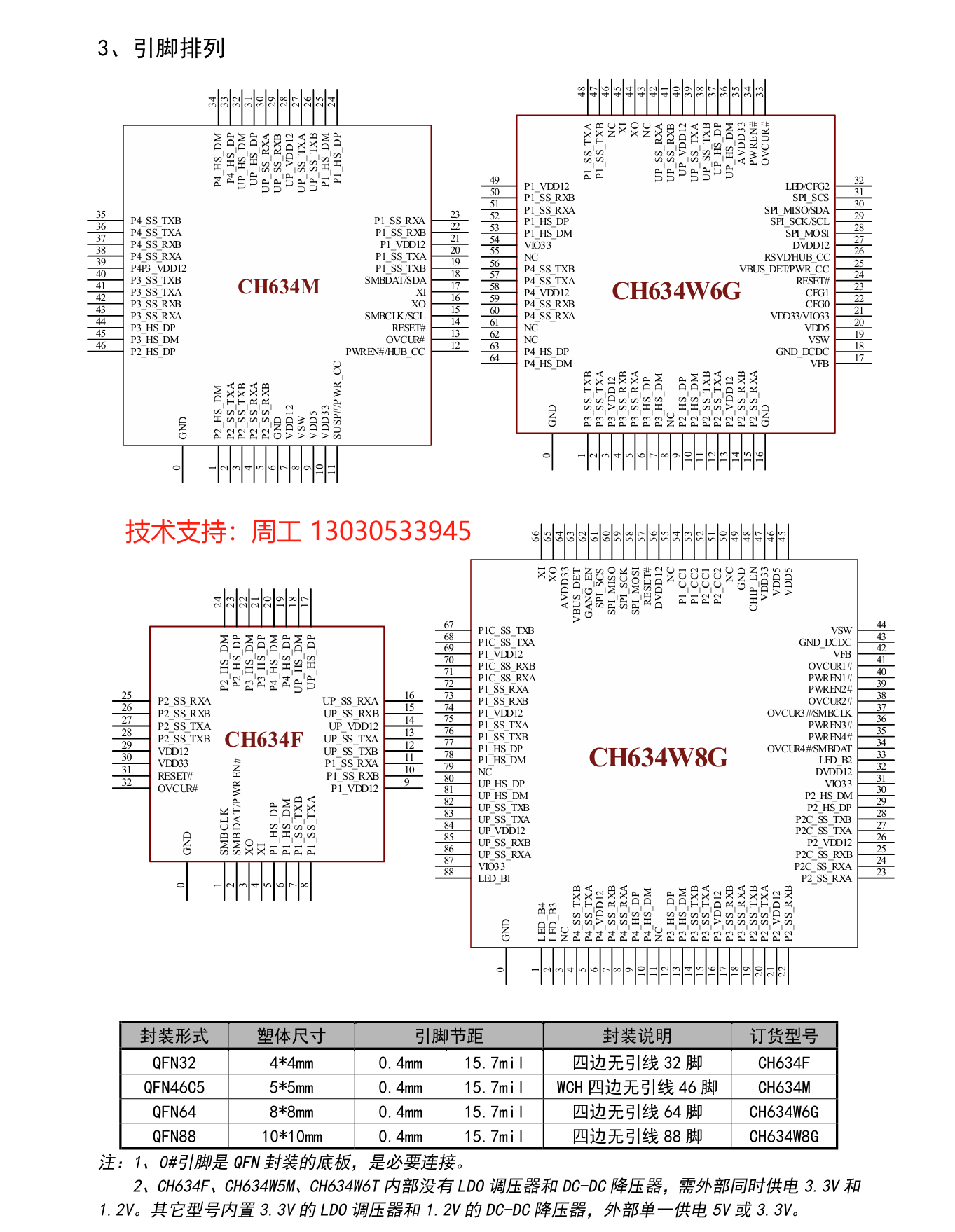

Delivery)功能,为用户提供超高速、灵活且可靠的USB连接解决方案。 一、核心特性 高速数据传输: CH634的上行端口支持USB3.0超高速5Gbps数据传输速率,同时兼容USB2.0高速

2025-02-07 16:07:46 4358

4358

舜铭存储铁电存储器SF25C20能否替换赛普拉斯FM25V20A

2025-01-23 09:03:29 953

953

一个基于FT600Q芯片 的USB3.0设计,进行高速传输,使用的是Micro usb3.0的接口,但是连接PC端口,显示无法识别该设备,请教各位大佬,这种情况是接口的设计有问题吗?下面是我的原理图。*附件:FTDI_FPGA.pdf

2025-01-20 14:48:57

在现代电子设备中,HDMI2.0接口已成为连接高清视频和音频信号的重要桥梁,而USB3.0接口则成为高速数据传输和多功能连接的核心枢纽;然而,这些接口也容易受到静电放电(ESD)和浪涌电压的影响,可能导致设备损坏或性能下降。上海雷卯电子

2025-01-15 09:44:16 950

950

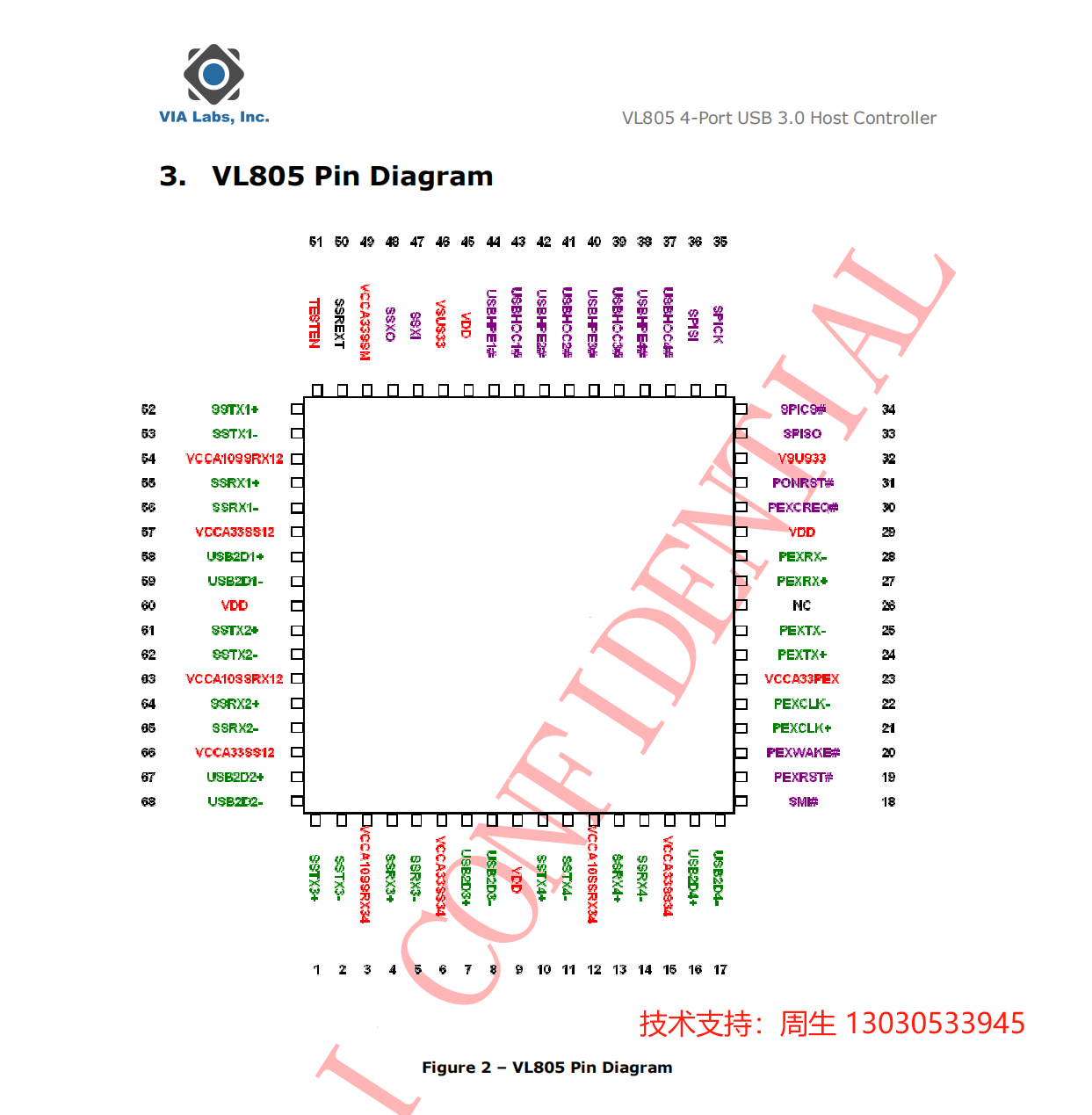

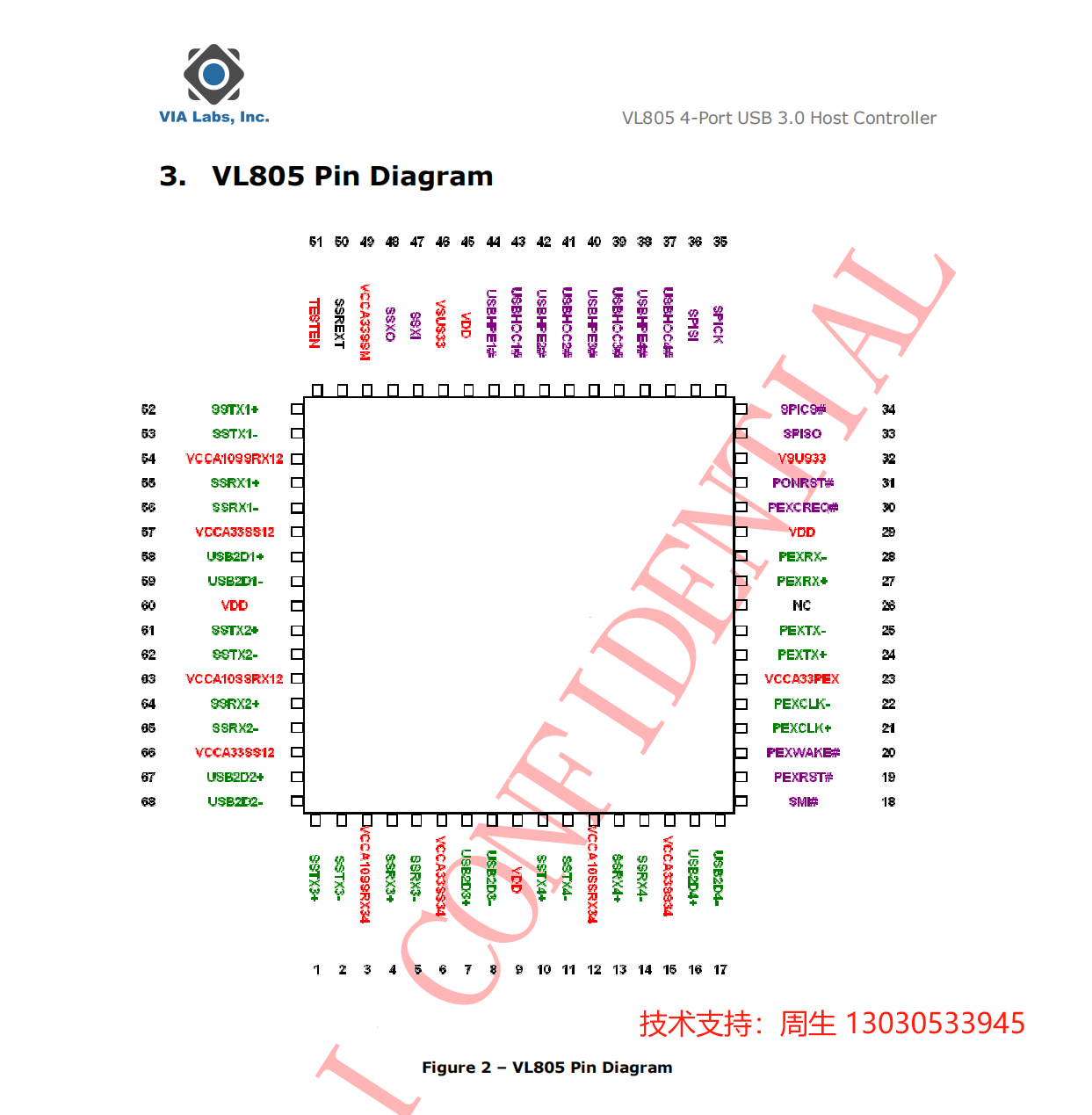

一、概述 VL805-Q6是一款由威盛(VIA)公司推出的单芯片USB 3.0主机控制器。该芯片启用了PCI Express接口,支持USB 3.0的5 Gbps超高速数据传输,并且向下兼容USB

2025-01-08 09:16:01 2464

2464

电子发烧友App

电子发烧友App

评论