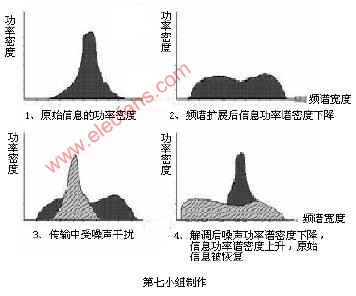

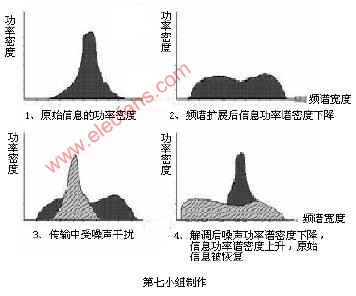

直接序列扩频(DSSS) 发送端直接采用高码率的扩频码序列去扩展信号频谱,接收端通过同样的扩频码序列还原信号。直接序列扩频将信号扩展成很宽的频带,其功率频谱密度比噪声还要低,使信号能隐蔽在噪声中,提高信号保密性。

2023-10-10 16:42:59 130

130

,这篇文章将会详细介绍它们之间的差异。 单脉冲时钟信号是指在短时间内以一定的速率发生较短、高速峰值的脉冲信号。它们通常用于时序控制,计数和精确时钟测量系统中。一般而言,单脉冲信号所用的频率比较高,可达数百MHz级别,这比其他

2023-09-15 16:28:23 195

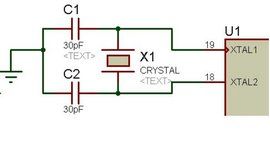

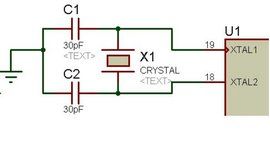

195 时钟信号怎么产生的 时钟信号是一种重要的信号,它在电子设备中广泛应用。时钟信号的产生与传输是现代电子设备中不可或缺的基础技术之一。时钟信号的精确性和准确性是现代电子设备能够实现高速计算等复杂操作

2023-09-15 16:28:22 377

377 芯片为什么需要时钟信号? 在我们日常生活中,我们所使用的各种电子设备都需要一个时钟信号来进行计时和同步,例如:手机、电脑、电视、汽车、机器人、智能家居等设备都需要时钟信号。对于各种这些电子设备

2023-09-15 16:28:14 368

368 时钟信号和脉冲信号有区别吗? 时钟信号和脉冲信号虽然在某些方面可能有相似之处,但它们在本质上是不同的。本文将深入探讨这两种信号的特点、应用和区别。 1.时钟信号 时钟信号是一种用于同步处理器

2023-09-15 16:28:12 375

375 现一系列问题,如串扰、反射波、时钟抖动等。为了确保高速信号传输的稳定和可靠性,需要进行仿真串扰。本文将详细介绍高速信号仿真的串扰以及为什么需要进行仿真。 对于高速信号来说,串扰是一种令人头疼的问题。串扰是指高速信

2023-09-05 15:42:31 249

249 芯片为什么要时钟信号 芯片是现代电子设备的核心组成部分,广泛应用于计算机、手机、电视等各个领域。芯片内部有着复杂的电子元件和电路结构,这些元件和电路结构需要进行同步操作,以实现正确的工作。因此,芯片

2023-09-01 15:38:11 568

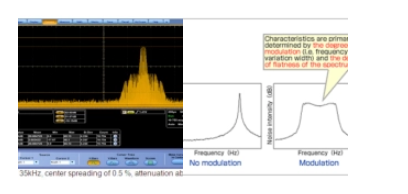

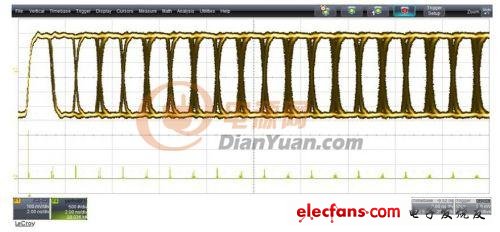

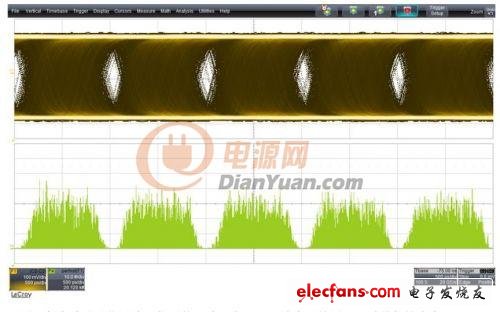

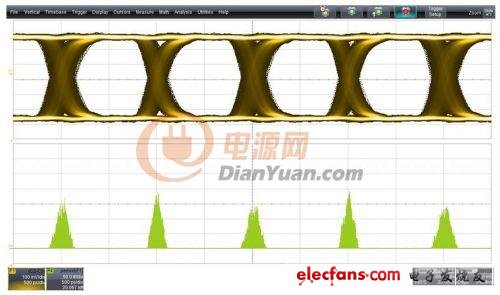

568 与系统之间的高速连接,由于不同设备可能由不同的厂商提供,为了保证设备之间可靠的互联互通,必须对其接口进行一致性测试。同时高速串行信号容易对系统内部或者外部产生EMI辐射和干扰,PCIE标准定义了SSC

2009-04-08 08:32:33

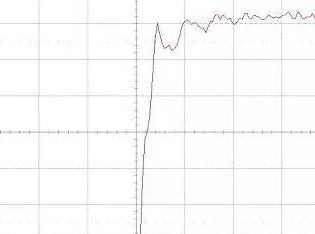

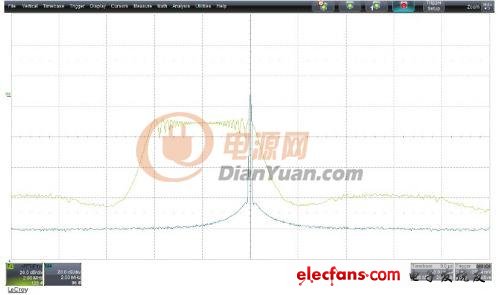

本文结合实际测试中遇到的时钟信号回沟问题介绍了高速信号的概念,进一步阐述了高速信号与高频信号的区别,分析了25MHz时钟信号沿上的回沟等细节的测试准确度问题,并给出了高速信号测试时合理选择示波器的一些建议。

2023-06-13 11:02:52 362

362

随着集成电路技术的发展,高速信号的设计技术指标不断更新,系统中的数据传输速率已经提高到数十 Gbit/s 乃至数百 Gbit/s,这就给测试系统、测试硬件设计、测试信号传输质量等带来了新的挑战和更高

2023-06-02 13:43:05 551

551

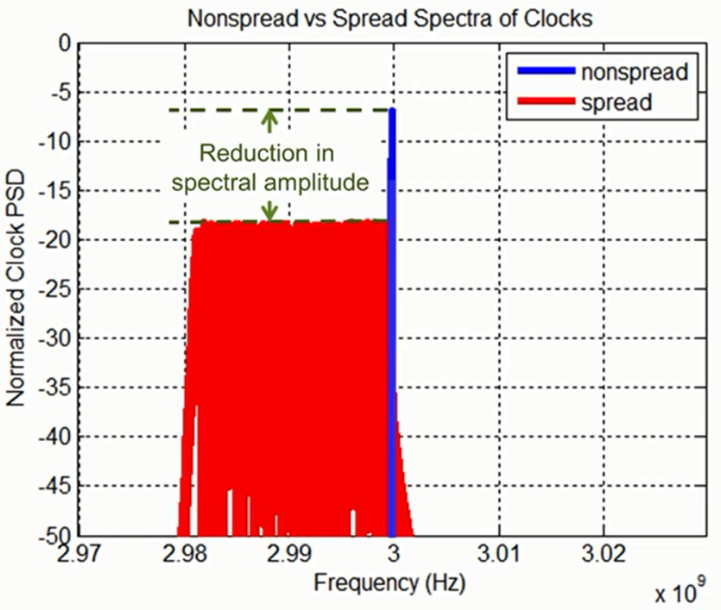

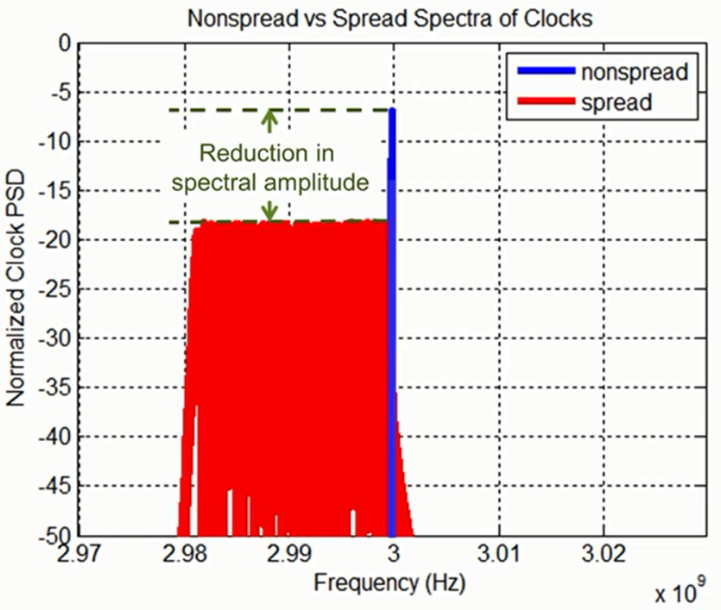

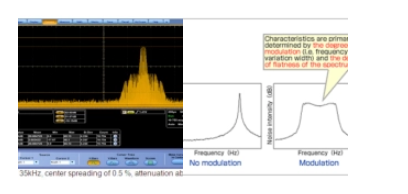

扩频时钟是以受控方式对系统时钟进行抖动以降低峰值能量含量的过程。SSC技术用于最小化电磁干扰(EMI)和/或通过联邦通信委员会(FCC)的要求。

2023-05-26 16:51:37 2510

2510

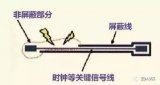

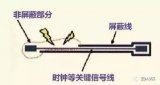

解决。 高速信号走线屏蔽规则 如上图所示:在高速的PCB设计中,时钟等关键的高速信号线,则需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都是会造成EMI的泄漏。 建议屏蔽线每1000mil打孔接地 。 高速信号的走线闭环规则 由于PCB板的密度越来越高,很多PCB

2023-05-22 09:15:58 509

509

扩频通信的主要目的是提高通信信号的抗干扰性和保密性。通过在发送信号时对其进行频率扩展,使得信号在宽带频谱上占用更大的带宽,从而可有效抵消窄带干扰信号对于通信信号的影响。

2023-05-10 17:52:32 978

978 扩频技术是一种利用噪声来实现通信的方法,它可以在一定程度上抵消干扰信号对于通信信号的影响,同时也可以使得被窃听的信号更难被解读和破解。

2023-05-05 16:28:27 2645

2645 功能单元测试测试中非常重要的一项是信号完整性测试,特别是对于高速信号,信号完整性测试尤为关键。

2023-02-23 09:20:06 744

744 RF DAC的无杂散动态范围受到严重的数字do主开关的限制,这会干扰模拟输出信号。介绍了一种扩频时钟发生器(SSCG)的设计、布局和仿真。SSCG调制用于切换DAC数字块的时钟频率,以减少DAC

2023-02-14 16:43:56 0

0 功能单元测试测试中非常重要的一项是信号完整性测试,特别是对于高速信号,信号完整性测试尤为关键。

2023-02-13 15:10:24 1495

1495 在高速信号的设计中,一般考虑的并不是信号的周期频率F,一般是有效频率F1,T代表信号的时钟周期,T1代表信号的10%-90%的上升时间。

2022-12-26 10:50:42 1540

1540 来源:罗姆半导体社区 提到“高速信号”,就需要先明确什么是“高速”,MHz速率级别的信号算高速、还是GHz速率级别的信号算高速? 传统的SI理论对于“高速信号”有经典的定义。SI:Signal

2022-12-12 16:56:35 4588

4588 AN4850_STM32扩频时钟生成原理、性能与实现

2022-11-21 17:06:48 0

0 在无线通信系统中,普遍使用扩频通信技术,因此扩频技术对通信系统具有重要的现实意义。直接序列扩频技术是应用最广的一种扩频技术,FPGA具备高速度的并行性特点在无线通信系统中的优势日益增强,利用FPGA实现直接序列扩频技术,可增大传输速率,可以使扩频技术有更好的发展与应用。

2022-10-31 08:58:22 855

855 本章的主要内容: 分析时钟驱动器、时钟信号的特殊布线 改进时钟信号分配的特殊电路

2022-09-20 14:55:40 0

0 如果用单独的时钟信号板,一般采用什么样的接口,来保证时钟信号的传输受到的影响小?

2022-09-16 08:58:49 1507

1507

本文结合实际测试中遇到的时钟信号回沟问题介绍了高速信号的概念,进一步阐述了高速信号与高频信号的区别,分析了25MHz时钟信号沿上的回沟等细节的测试准确度问题,并给出了高速信号测试时合理选择示波器的一些建议。

2022-09-14 09:20:17 2417

2417 AD9577:带双锁相环、扩频和余量的时钟发生器数据表

2021-04-29 20:06:50 8

8 MB86R02“ Jade-D”中集成了一个可配置的扩频时钟发生器单元,以便能够提供调制时钟信号(作为选择,与内部PLL单元的输出并行),供GDC内部使用。

2021-04-14 16:51:07 1873

1873

信号回沟,即波形边缘的非单调性,是时钟的大忌,尤其是出现在信号的门限电平范围内时,由于容易导致误触发,更是凶险无比。所以当客户测试发现时钟信号回沟,抱着一心改板的沉痛心情找到高速先生时,高速先生

2020-11-26 09:58:01 6459

6459 当你需要测量高速时钟频率时,可能选择价位昂贵的台面仪器。而实际上,使用低价位数字测试仪器的数字捕获能力,再加上一些DSP软件函数即可测试高速时钟。下文介绍了具体的实现办法。

2020-08-18 14:32:46 524

524

规则一:高速信号走线屏蔽规则 如上图所示: 在高速的PCB设计中,时钟等关键的高速信号线,走需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都是会造成EMI的泄漏。 建议屏蔽线,每1000mil,打孔

2020-02-14 11:53:40 11426

11426 所有的高速信号必须有良好的回流路径,尽可能地保证时钟等高速信号的回流路径最小,否则会极大的增加辐射,并且辐射的大小和信号路径和回流路径所包围的面积成正比。

2019-04-03 09:30:51 6723

6723

本文介绍了时钟扩频技术的原理、分类,结合它在摄像头的具体应用案例,与传统EMI抑制手段的实际效果进行对比,突显时钟扩频技术在抑制时钟EMI上的优势。目前,时钟扩展频谱技术被广泛使用在图像采集、图像

2018-05-18 02:13:00 1883

1883

EMI限制的遵守往往是一个挑战。扩频时钟通常用于最小化EMI。调制周期信号(时钟和数据)的效果是通过在一个频率范围内传播能量来降低峰值发射。

2018-05-17 16:19:08 8

8 在高速信号发生应用中,带宽和分辨率是关键要求。新型信号发生应用运用高速数模转换器(DAC)来产生各种不同类型的波形,包括单音直至具数百兆赫兹带宽、复杂的多通道波形。这些应用要求高速DAC足够快,以在

2017-11-15 10:48:54 4

4 一、高速串行总线基本知识 并行总线之所以在高速传输上被串行总线取代的原因就在于:第一,系统时钟的瓶颈;第二,总线间的串扰。要达到上Gbps的传输速率,对于并行总线而言,势必时钟频率要达到GHz

2017-11-14 15:42:05 23

23 什么是扩频通信技术?扩频通信技术是一种信息处理传输技术。扩频通信技术是利用同域传输数据(信息)无关的码对被传输信号扩展频谱,将信号调制到多个载波频率的技术。使之占有远远超过被传送信息所必需的最小带宽

2017-11-13 10:40:24 30655

30655 SvstemView是一个功能齐备的系统仿真软件,主要用于各种通信系统的设计和分析。本文使用SvstemView构建扩频通信仿真系统,模拟信号在扩频通信中的传输过程中,并通过分析比较信号在扩频

2017-11-10 16:13:24 14

14 。文章对扩频技术应用原理及影响因素进行分析,结合车载电子终端中频辐射骚扰测试实例,证明时钟扩频技术可以有效地改善车载电子电磁兼容性能。

2017-11-09 16:21:33 7

7 本文结合实际测试中遇到的时钟信号回沟问题介绍了高速信号的概念,进一步阐述了高速信号与高频信号的区别,分析了25MHz时钟信号沿上的回沟等细节的测试准确度问题,并给出了高速信号测试时合理选择示波器的一些建议。

2017-09-19 07:41:00 21613

21613

了解高速ADC时钟抖动的影响将高速信号数字化到高分辨率要求仔细选择一个时钟,不会妥协模数转换器的采样性能(ADC)。 在这篇文章中,我们希望给读者一个更好的了解时钟抖动及其影响高速模数转换器的性能

2017-05-15 15:20:59 13

13 高速信号完整性测试和验证技术

2017-01-14 02:53:59 23

23 10GHz扩频时钟发生器的设计_胡帅帅

2017-01-07 21:28:58 1

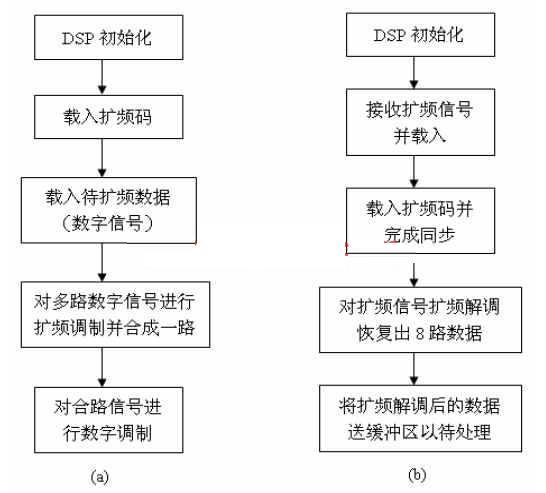

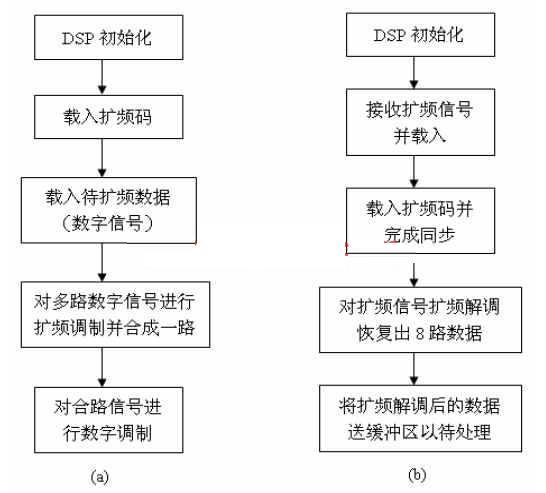

1 一种基于高速数字信号处理器(DSP)的扩频电台基带处理模块的设计研制。该模块利用无线局域网成熟的扩频通信技术,具有抗干扰能力强、数据传输速率高、性能稳定可靠等特点。模块采用DSP开发扩频电台的通信和控制协议,软件设计灵活,为软件的升级和通信功能的扩展提供了方便并取得了良好的实验效果。

2016-11-05 09:20:31 836

836

您在测试 ADC 的SNR时,您可能会连接一个低抖动时钟器件到转换器的时钟输入引脚,并施加一个适度低噪的输入信号。如果您并未从您的转换器获得SNR产品说明书标称性能,则说明存在

2011-10-12 12:00:09 2577

2577

在有效抑制EMC 干扰的扩频时钟发生器(SSCG)中内置FRAM 的新产品MB88R157A 被纳入富士通的产品阵容。针对10MHz ~ 50MHz 的输入频率,该产品的输出时钟频率可以在1MHz ~ 134MHz 范围内任意设

2011-08-31 17:26:32 40

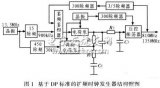

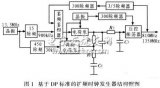

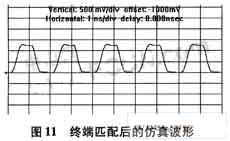

40 这里设计一种基于DP标准采用μ工艺的发射端扩频时钟发生器。合理设计锁相环路,采用外加滤波器对压控振荡器的控制电压进行三角波调制,得到所需的扩频时钟。

2011-08-31 10:17:32 1623

1623

本内容提供了基于扩频技术的测井信号长距离传输系统,希望对大家有所帮助

2011-06-22 15:39:06 21

21 信号编码技术 数据、信号和传输的模拟与数字之分 信号编码准则 数字数据与模拟信号 模拟数据与模拟信号 模拟数据与数字信号 扩频技术 差错控制技术

2011-03-31 12:19:38 38

38 引言

随着电子技术的不断发展,数据的传输速度越来越快,高速时钟的应用日益广泛,如何保证时钟在高速跳变过程中的信号完整性、抖动、功耗等问题,已

2010-11-03 11:05:01 1561

1561

继“深入浅出谈高速串行信号测试(一)”获得大家鼓励后,也有网友以及来自客户拜访中对于抖动的提问,使我萌发了写下篇的念头。在这篇博文中我们深入讨论一下高速信号

2010-10-16 17:43:32 16

16 多路测量信号扩频传输的DSP系统设计

1. 引 言

在测控领域,通常要求对多路检测信号进行传输。信号的传输过程中常受到周围复杂环境的干扰会产生较大的失真。

2010-03-19 10:44:55 878

878

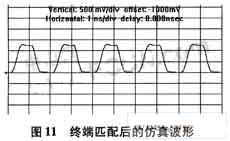

本文对多路测量信号的扩频传输系统进行了研究,提出了对所传输信号的频谱进行扩展并利用码分复用实现多路信号的复用传输的方法。分析了多路测量信号扩频传输系统的DSP系统实

2010-02-24 14:22:18 13

13 基于FPGA的直接序列扩频发射系统研究

现代通信系统尤其是扩频系统需要完成快速复杂的信号处理,对电路的处理速度提出了更高的要求.根据FPGA高速并行的处

2010-02-22 14:58:54 25

25 高速并行总线信号完整性测试技术张楷 泰克科技(中国)有限公司摘要:随着信号速度的显著提高,信号完整性问题已经成为高速数字设计中的关键。本文介绍了一种新的信

2009-12-17 14:38:21 23

23 该文研究的是在未知扩频序列的情况下,实现多序列直扩信号(也称软扩频信号)的解扩。对于传统直扩信号来说,主模解扩法(DMDS)被证明是一种有效的盲解扩方法,但是它并不适用于

2009-11-24 14:35:24 12

12 高速并行总线信号完整性测试技术:随着信号速度的显著提高,信号完整性问题已经成为高速数字设计中的关键。本文介绍了一种新的信号完整性分析技术,通过集成逻辑分析仪和

2009-10-17 17:11:55 44

44 高速信号、时钟及数据捕捉:数据转换系统背后的运作原理— 作者:Ian King 美国国家半导体公司应用技术工程师随着仿真/数字转换器的数据转换取样率提高至每秒千兆个取

2009-09-25 10:42:19 13

13 扩频通信技术及应用:扩频通信,即扩展频谱通信技术(Spread Spectrum Communication),它的基本特点是其传输信息所用信号的带宽远大于信息本身的带宽。除此以外,扩频

2009-05-22 00:57:35 116

116 直接序列扩频(DSSS)基本概念:所谓直接序列扩频, 就是在发端直接用具有高码率的扩频码序列对信息比特流进行调制, 从而扩展信号的频

2009-05-21 14:37:08 40993

40993

CDMA的扩频增益,什么是扩频增益

通常在衡量扩频系统抗干扰能力的优劣时

2009-05-20 10:48:29 5696

5696

什么是扩频通信,扩频通信的定义

扩频通信,即扩展频谱通信技术(Spread Spectrum Communication),它的基本特点是其传输信息所用信号

2009-05-20 09:55:38 6433

6433 摘要:降低电磁干扰(EMI)是电子系统设计人员需要考虑的一个重要因素,扩频时钟(CLK)为降低EMI提供了一个有效途径。本文给出了扩频CLK的定义和估算EMI抑制性能的简单公式。所提供

2009-05-05 10:58:36 974

974

摘要:降低电磁干扰(EMI)是电子系统设计人员需要考虑的一个重要因素,扩频时钟(CLK)为降低EMI提供了一个有效途径。本文给出了扩频CLK的定义和估算EMI抑制性能的简单公式。所提供

2009-05-03 11:04:39 652

652

摘要:降低电磁干扰(EMI)是电子系统设计人员需要考虑的一个重要因素,扩频时钟(CLK)为降低EMI提供了一个有效途径。本文给出了扩频CLK的定义和估算EMI抑制性能的简单公式。所提供

2009-04-22 10:10:41 306

306

如何实现高速时钟信号的差分布线

在高速设计中,如何解决信号的完整性问题?差分布线方式是如何实现的?对于只有一个输出端的时钟信号线,如何实现差分布线?

2009-04-15 00:26:37 2963

2963 扩频通信调制器的FPGA设计与仿真

近年来,随着经济的高速增长,无线通信得到了飞速地发展。由于扩展频谱信号具有抗干扰、保密、抗侦破和抗衰落等特点,扩频通信

2008-10-16 08:56:02 708

708

电子发烧友App

电子发烧友App

评论