FPGA/ASIC技术

电子发烧友本栏目为FPGA/ASIC技术专栏,内容有fpga培圳资料、FPGA开发板、FPGA CPLD知识以及FPGA/ASIC技术的其它应用等;是您学习FPGA/ASIC技术的好栏目。turn开发板(尺寸 63x102mm,包括 HDMI、 以太网、 USB等外设)

作者:Steve Leibson, 赛灵思战略营销与业务规划总监 Z-turn开发板是米尔科技推出的一款开发板。它基于Xilinx Zynq-7010 SoC,为系统评估和原型验证提供了良好的平台。在你的嵌入式设计中,它也可以...

2017-02-09 457

DornerWorks将在赛灵思Zynq UltraScale+ MPSoC上支持Xen Hypervisor

作者:Steve Leibson, 赛灵思战略营销与业务规划总监 上周,Xilinx发布了 Zynq UltraScale+ MPSoC,此款产品拥有一个ARM Cortex-A53四核CPU,一个双核的ARM Cortex-R5 CPU,一个GPU,并在Xilinx 16纳米的UltraScale+可编...

2017-02-09 621

移动设备设计需求快速变迁软件定义仪器提高测试弹性

行动电子装置日新月异,产品测试需求也不断变迁。在此一发展趋势下,传统以硬体为主且功能有限的仪器将逐渐不敷使用,而采用软体定义架构且具备功能扩充弹性的自动化测试系统,在未来...

2017-02-09 273

我与赛灵思FPGA的故事”:本科生的FPGA之路

之前已经写了一份博文,不过提交出了问题,就没有后续了,然后突然想到之前有答应分享自己的FPGA经历,所以,还是决定抽时间再写一下,把这份分享补上。 FPGA全名现场可编辑门阵列,现在...

2017-02-09 390

关于FPGA开发手记之UART接口的开发

以下内容均以Xilinx的Nexys3作为开发板 1. UART简介 UART(即Universal Asynchronous Receiver Transmitter 通用异步收发器)是广泛使用的串行数据传输协议。UART允许在串行链路上进行全双工的通信。 串行外设...

2019-10-06 1285

7000应用开发技巧:模拟设备驱动(Mocking)

Neil Johnson – 首席顾问 – XtremeEDA Soheil Salehian – 助理研究员 – 卡尔加里大学 模拟(Mocking)是嵌入式系统开中用于单元测试和测试驱动的一种技术。模拟的好处在于通过删除不相关的从属代码...

2017-02-09 749

4K视频有哪些优点? 现实分辨率如何? 在2014年NAB大会上参展的佳能与索尼对此

如果当你问技术人员,为什么需要4K视频,您会以为答案总是与帧分辨率、色域、以及其他以功能为中心有关。但如果您问从事设计实际使用4K设备的人们,他们对4K视频有更好理解。以下为我参...

2017-02-09 593

殿堂级嵌入式高手的建议:如何保证你项目顺利?

1971年微处理器刚刚出现时,我的好朋友Jack Ganssle已经站立在嵌入式硬件与软件的交叉路口上,当我第一次碰到他时是二十世纪八十年代,Jack拥有一家专门从事电路模拟的公司。在我看来,现在...

2017-02-09 328

Trenz Electronic GmbH推出支持4 个 MGT链路、基于Z

Trenz Electronic GmbH 的 TE0715 是 4 x 5cm 封装系列的最新产品。它是一款基于 Xilinx Zynq SoC 的工业级 SoM ,具有 4 个 MGT 链路、一个千兆位以太网收发器、 32 位宽 1 Gb DDR3 SDRAM 、一...

2017-02-09 305

Xen开源管理程序为 Zynq Ultrascale+ MPSoC 实现虚拟化

Xilinx 选择联盟高级会员 DornerWorks 在 Zynq MPSoC 上支持开源 Xen 管理程序,从而可在 4 核 ARM® Cortex®-A53 上实现虚拟化。 DornerWorks 不仅将为构建基于管理程序的系统提供综合客户支...

2017-02-09 551

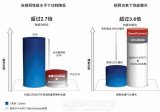

Xilinx 16nm UltraScale+器件实现2至5倍的性能功耗比优势

作者:Mike Santarini 赛灵思公司赛灵思杂志发行人 mike.santarini@xilinx.com 台积公司的16nm FinFET工艺与赛灵思最新UltraRAM和SmartConnect技术相结合,使赛灵思能够继续为市场提供超越摩尔定律的价值优势...

2017-02-09 2281

7 FPGA原型设计系统,支持达28800万个ASIC门的容量

Aldec 的 HES-7 (HES7XV12000BP) 在 FLG1925 封装中包含 6 个 Xilinx Virtex-7 2000T FPGA ,每款电路板可提供多达 7200 万个 ASIC 门的容量。 FPGA 原型设计系统通过添加多达 3 个附加电路板,...

2017-02-09 506

Enclustra Zynq SoC 模块的 Android 4.3.1 版现已在 GitHub 上提供

曾经想在 FPGA 上玩愤怒的小鸟吗? Enclustra Mars ZX3 片上系统 (SoC) 模块可让您如愿以偿。该模块建立在 Xilinx Zynq-7020 SoC 基础之上,可采用行业标准 SO-DIMM 封装提供完整的系统解决方...

2017-02-09 348

Xilinx升级Vivado 2014.3的FPGA功率优化

参加 FPGA 功率优化班,将帮助您创建更高电源效率的 FPGA 设计。通过本课程的学习,将有助于您的设计满足更小型化的 FPGA 器件,降低 FPGA 功耗,或在更低的温度下运行 FPGA 。另外...

2017-02-09 364

Xilinx推出有关 Zynq SoC 加速器的最新培训课程

为期 1 天的加速器开发流程介绍主要讲解如何测量系统性能、确定什么软件功能应该移至硬件,如何使用 Vivado® HLS 工具装配一款定制加速器,如何将该定制加速器添加至 Zynq SoC 设计,...

2017-02-09 585

东芝工业1080P60摄像头模块现已提供

该摄像头模块具有东芝 TCM3232PB 全高清( 1080p 高清)图像传感器。该传感器针对安全监控应用进行了全新设计,可使用东芝高动态范围 (HDR) 技术提供 60 帧每秒 (fps) 的高质量视频采...

2017-02-09 287

Avnet的MicroZed嵌入式视觉载卡套件

MicroZed™ 嵌入式视觉载卡套件建立在 MicroZed SOM 基础之上,提供视频专用载卡。套件包含开发定制视频应用程序所需的硬件、软件以及 IP 核。该载卡套件包括嵌入式视觉载卡,载卡具有...

2017-02-09 415

2015冬季版 Xcell 杂志现已推出!

Xcell 杂志第 90 期封面报道从系统层面报道了 Xilinx 最新推出的 UltraScale+™ 产品系列 FPGA 、 3D IC 及其第二代 Zynq® 全可编程 SoC (Zynq UltraScale+ MPSoC) 以及如果通过 28nm 7 系列器件...

2017-02-09 326

Xilinx UltraScale FPGA 帮助实现海量 DDR4 内存带宽

内存缓冲是高性能设计过程中的常见处理瓶颈。应用开发人员现已将目光投向了比 DDR3 更高的内存带宽、电源效率及成本降低水平。查看本期的实战论坛,其中电子工程杂志的 Amelia Dalton ...

2017-02-09 1217

加速 Zynq 全可编程 SoC 的开发进程

运行时间软件可能是嵌入式开发过程中的一个巨大瓶颈。无论您需要了解如何通过 Xilinx SDK 调试 U-Boot 代码,如何编写 U-Boot 脚本(存储和恢复这些脚本),还是需要了解如何配置和运...

2017-02-09 267

如何引爆您的浮点运算?加块Zynq

作者:Steve Leibson, 赛灵思战略营销与业务规划总监 Zynq使Intel四核CPU浮点运算性能提高1.7倍 Topic Embedded的产品总监Inge Rutten最近在Linked In(领英)发表了一篇文章,文章介绍了基于Zynq的Miami SOM(...

2017-02-09 1692

EEJournal的“用软件来定义一切”涉及了新的SDSoC设计环节

作者:Steve Leibson, 赛灵思战略营销与业务规划总监 EEJournal刚刚刊登了Kevin Morris的文章,名字叫做用软件来定义一切:Xilinx推出SDSoC,文章描述了作者关于新的SDSoC设计环境的构想。 软件SDSoC提供...

2017-02-09 366

Xilinx:SDSoC让硬件工程师变“软”

众所周知,FPGA是一种以硬件描述语言(Verilog或VHDL等)所完成的电路设计硬件可编程逻辑器件。可是随着技术的不断发展,Xilinx(赛灵思)却正在不断让FPGA变“软”。 近日,赛灵思推出了面向全可编...

2017-02-09 425

关于FPGA将带来至多25倍单位功耗性能提升的分析和介绍

很久没有看FPGA了,本来想继续学习HLS,就上Xilinx的网站看了看。结果发现了SDx 开发环境,很新的一个东西。由于我对这方面了解不多,本篇博文仅仅只是资料的整合和介绍。 Xilinx官网这样解释...

2019-10-06 1325

Vivado+Zedboard之入门实例精选

继续介绍vivado+zedboard入门实例。均为参照教程实际操作验证成功的实例,在此拿出来与大家分享。由于教程中步骤已经非常清晰,本文只是简单介绍实例以及试验时的修正记录,具体的教程及个...

2017-02-09 1083

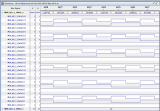

Xilinx VDMA 24位流输出与32位AXI总线的内存流数据关系

测试方法采用了VDMA仅有MM2S通道, 内存中的图像帧是用MicroBlaze核写入的一个colorbar. VDMA的mhs部分如下, 因为我的输出用了Digilent的HDMI核,而这个HDMI核是32位的,我自己写了个axis_24_32的位宽转换的ip...

2017-02-09 975

Xilinx Zynq Linux内核源码编译过程

1.交叉编译环境的安装配置 1) +Xilinx+Tools 2.uboot的编译 1)下载uboot源代码 下载uboot源代码,务必要下载tar.gz格式的文件,地址: https://github.com/Xilinx/u-boot-xlnx/releases 进入u-boot目录下tools目录,添加...

2017-02-09 1127

Zynq7000系列之芯片引脚功能综述

很多人做了很久的FPGA,知道怎么去给信号分配引脚,却对这些引脚的功能及其资源限制知之甚少;在第一章里对Zynq7000系列的系统框架进行了分析和论述,对Zynq7000系列的基本资源和概念有了大...

2017-02-09 6504

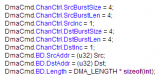

Zynq DMA第七篇:Adam Taylor 玩转MicroZed 系列29

前期博客中介绍了 Direct Memory Access,本博客将主要介绍利用简单示例演示如何设置和使用DMA。要演示这个示例,我使用一个DMA控制器通道将一个内存位置转移到另一个存储器位置。 与我们在本...

2017-02-09 412

高速ADC和DAC如何与FPGA配合使用

许多数字处理系统都会使用FPGA,原因是FPGA有大量的专用DSP以及block RAM资源,可以用于实现并行和流水线算法。因此,通常情况下,FPGA都要和高性能的ADC和DAC进行接口,比如e2vEV10AQ190低功耗四通...

2017-02-09 2404

编辑推荐厂商产品技术软件/工具OS/语言教程专题

| 电机控制 | DSP | 氮化镓 | 功率放大器 | ChatGPT | 自动驾驶 | TI | 瑞萨电子 |

| BLDC | PLC | 碳化硅 | 二极管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 无刷电机 | FOC | IGBT | 逆变器 | 文心一言 | 5G | 英飞凌 | 罗姆 |

| 直流电机 | PID | MOSFET | 传感器 | 人工智能 | 物联网 | NXP | 赛灵思 |

| 步进电机 | SPWM | 充电桩 | IPM | 机器视觉 | 无人机 | 三菱电机 | ST |

| 伺服电机 | SVPWM | 光伏发电 | UPS | AR | 智能电网 | 国民技术 | Microchip |

| 开关电源 | 步进电机 | 无线充电 | LabVIEW | EMC | PLC | OLED | 单片机 |

| 5G | m2m | DSP | MCU | ASIC | CPU | ROM | DRAM |

| NB-IoT | LoRa | Zigbee | NFC | 蓝牙 | RFID | Wi-Fi | SIGFOX |

| Type-C | USB | 以太网 | 仿真器 | RISC | RAM | 寄存器 | GPU |

| 语音识别 | 万用表 | CPLD | 耦合 | 电路仿真 | 电容滤波 | 保护电路 | 看门狗 |

| CAN | CSI | DSI | DVI | Ethernet | HDMI | I2C | RS-485 |

| SDI | nas | DMA | HomeKit | 阈值电压 | UART | 机器学习 | TensorFlow |

| Arduino | BeagleBone | 树莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 华秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |