FPGA/ASIC技术

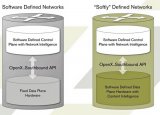

电子发烧友本栏目为FPGA/ASIC技术专栏,内容有fpga培圳资料、FPGA开发板、FPGA CPLD知识以及FPGA/ASIC技术的其它应用等;是您学习FPGA/ASIC技术的好栏目。“软”定义规范环境(SDNet)扩展至数据层实现高速SDN

一个月前Xilinx 新兴技术研究会上,斯坦福大学计算机科学系教授Nick McKeown教授说“未来的SDN芯片看起来将类似FPGA或某种可以在FPGA上构建的器件。...

2017-02-10 1088

一个FPGA中现在可集成多少32位RISC处理器?

Jan Gray是在FPGA中集成32位RISC处理器的专家,他写了一篇博客叫作FPGA CPU 新闻,副标题为 “使用FPGA开发并行计算机体系架构”。...

2017-02-10 2460

IIoT风潮兴 开放式软硬件设计平台身价涨

工业物联网(IIoT)应用商机蓬勃。包含空气污染、食品安全、智慧交通、远程医疗、信息化教育、智能工厂等领域都可透过物联网的布建,达到降低能耗/营运成本、提升操作效率等目标,因此工...

2017-02-10 917

SDAccel突破编程局限 实现FPGA应用加速

近年来,云计算和大数据应用呈爆发式增长,在推动数据中心产业升级的同时,也为数据中心的应用开发与运行维护带来了一系列问题。...

2017-02-10 1600

抢攻数据中心 赛灵思发布OpenCL开发工具

赛灵思(Xilinx)推出首款支持OpenCL的开发工具。现场可编程门阵列(FPGA)厂商正积极推出可支持OpenCL设计工具的新一代解决方案,期能协助FPGA深入到主流异质架构运算领域,并加速软件定义数据中心...

2017-02-10 1506

ZedBoard上的点灯签名实验(六)驱动开机自启动及OLED签名

写好了驱动,也就是留好了API的接口,接下来就可以在应用层面上调用API接口,从而实现对LED的操作了。为此我们要做一个准备工作,我们希望驱动开机自动加载,省去手动执行insmod命令,从而...

2017-02-10 1452

使用Vivado HLS创建一个EDK PCore

由于Zedboard是ARM+FGPA的架构,所以在使用的时候经常会涉及到关于FPGA设计方面的知识,对于像我这样对FPGA一窍不通的人来说,这是一个不可逾越的障碍(至少目前是)。...

2017-02-09 2110

从ISE启动ModelSim时遇到的问题及解决办法

从Windows的Start Menu开始,Xilinx ISE Design Suite 13.4 —〉EDK —〉Tools —〉Compile Simulation Libraries...

2017-02-09 5053

zynq使用自带外设IP让ARM PS访问FPGA(八)

参考超群天晴的博客 ,使用XPS为PS 处理系统 添加额外的IP。从IP Catalog 标签添加GPIO,并与ZedBoard板子上的8个LED灯相连。当系统建立完后,产生bitstream,并对外设进行测试。以后还有一个很重要...

2017-02-09 2632

此通用电路可以实现任意奇数分频电路

最近正在准备找工作,由于是做FPGA开发,所以verilog实现技术分频电路是一道经常出现的题目,三分频,五分频电路等等;经过一下午时间总结出了一个通用电路,可以实现任意奇数分频电路。...

2017-02-09 2990

轻松实现PL“打包”PS的功能

因为MicroZed是个低成本的开发套件,所以在板子上除了给PS(33.3333 MHz)、DDR、SPI FLASH、microSD卡接口和USB提供时钟信号外,并没有为PL部分提供单独的晶振。...

2017-02-09 5123

如何单独打开Xilinx SDK项目工程

.PPR文件是PLANAHEAD的工程文件,在WINDOWS下面可以直接双击打开,PROJECT.cache PROJECT.data是项目产生的临时文档,可以不用管。...

2017-02-09 7087

Digilent公司发布新款FPGA开发板

Digilent公司宣布了新款FPGA开发板,归属于其Nexys产品线——Nexys4——板上集成一个赛灵思Artix-7100T FPGA。...

2017-02-09 1858

基于新400Gbps CDFP2.0规范的模块

通过将100Mbps的CFP4光模块替换到基于新400Gbps CDFP2.0规范的模块,您将能够将1U前面板网络程控交换机的带宽从1.6Tbps提升到4.4Tbps。这种新的规范,今天刚由CDFP多源协议(MSA)公布——定义了使用...

2017-02-09 2519

基于FPGA开放流程的SDN转发引擎

博主Greg Ferro在其Ethereal Mind网页上发布了一则关于 Corsa Technology简短博客信息,提到Corsa公司制作了一对基于FPGA开放流程的SDN转发引擎。Ferro同时简单讨论了此引擎是否适用于WANs网络。...

2017-02-09 1309

ADI发布的AD9625器件可以帮你解决这一问题

直接采样RF信号需要很高的速度,ADI发布的AD9625器件可以帮你解决这一问题,因为该器件支持一个JESD204B接口,它的采样速率可以达到2Gsamples/sec,它可以和Xilinx All Programmable器件的JESD204 LogiCORE...

2017-02-09 2533

两款开发板卡开启您先进的全新的系统设计

尽管它是KintexUltraScale FPGA系列芯片中体积排名第二小的成员,但是这款20nm KintexUltraScale KU040 FPGA提供系统设计者更多的片上资源,在比较注重功耗的7系列产品系列中,这款新型的FPGA芯片比大部...

2017-02-09 2011

OKI IDS和Xylon成为合作伙伴进军日本的ADAS

两大赛灵思联盟成员,OKI IDS和Xylon成为合作伙伴进军日本的ADAS(先进型驱动辅助系统)市场。 Xylon的 logicBRICKS IP核库包括众多优化过的图形和视频处理IP块,用于赛灵思All Programmable器件,并在...

2017-02-09 1339

TECH:基于FPGA的高速以太网适配器卡必备的PCIe Gen3技术

INVEA-TECH公司制作了基于FPGA的硬件加速以太网接口卡(HANICs)。本周,该公司在加利福尼亚圣克拉拉以太网技术峰会上展示了两款高速以太网适配器卡—COMBO 80G和最近发布的COMBO 100G,它们都着重...

2017-02-09 1963

Xilinx FPGA普通IO作PLL时钟输入

普通IO可以通过BUFG再连到PLL的时钟输入上,但要修改PLL的设置 input clk的选项中要选择"No Buffer";...

2017-02-09 7749

骨灰级音响发烧友如何打造随身DAC兼耳扩?

Chord电子产品Hugo,一种专为骨灰级音响发烧友打造的电池供电的随身DAC兼耳扩,使用赛灵思 Spartan-6 FPGA.(使用了1/2的单元)实现了一个32位、26K抽头的WTA插值滤波器,为音乐爱好者创建了通往音乐...

2017-02-09 1754

ADI章新明:软件定义无线电助推RF器件层面革新

在近日举行的“易维讯第四届年度ICT媒体论坛”上,ADI公司技术大拿、高级客户应用经理章新明发表演讲,纵论了软件定义无线电技术(SDR)在RF器件层面的创新应用。...

2017-02-09 1394

赛灵思携手BEEcube推出全球首款毫米波原型设计平台解决方案

致力于支持5G应用创新开发,集成在BEEcube BEE7基带平台上的赛灵思256QAM毫米波调制解调器IP为宽带回程原型设计提供完整的开箱即用型解决方案...

2017-02-09 2069

用现有的Cat 5e/6传输设备将数据中心带宽和吞吐量提高5倍?

将1Gbps以太网线缆提高到2.5或者5Gbps承诺的数据中心带宽效率和吞吐量,并在低成本投入下实现高带宽, 这就是新NBASE-T Alliance的目的,这刚由创世成员思科、Aquantia、飞思卡尔和赛灵思宣布。...

2017-02-09 2923

FMC板扩展了基于Zynq的Avnet ZedBoard的网络性能

来自Opsero ElectronicDesign的以太网FMC卡接入基于 Zynq的 Avnet ZedBoard的LPC(低引脚数)FMC连接器,在板子的外设上添加了4个千兆以太网端口。板子本身有4个Marvell 88E1510千兆以太网PHY和带有集成磁件的...

2017-02-09 3228

使用FPGA,NPU或者多核处理器来实现高性能包处理?

作者:Steve Leibson, 赛灵思战略营销与业务规划总监 你想对FPGA、NPU和多核CPU在包处理中的优缺点有个清晰认识吗?在圣克拉拉的Linley Processor Conference 2014上赛灵思的AtulShinde发表了为最佳载体以太...

2017-02-09 871

2400 PHY同时又能确保FPGA需要的I/O灵活性?

来自赛灵思的Adrian Cosoroaba和Terry Magee在圣克拉拉会议中心的Memcon中发表了关于高性能DDR4接口和FPGA灵活性的主题演讲。赛灵思首席工程师Magee,设计了用于新赛灵思UltraScale All Programmable FPGA的DD...

2017-02-09 421

启动流程分析及各环节文件生成流程(ZedBoard为例)

1. ZYNQ的启动流程 Zynq7000就如同他的名字一样,Zynq-7000 Extensible Processing Platform,是一个可扩展处理平台,简单说就是有个FPGA做外设的A9双核处理器。 所以,它的启动流程自然也和FPGA完全不同,...

2017-02-09 1766

关于PWM发生器的性能分析和应用介绍

在这篇实例之前,说点自己的两点感受。 一、这个zynq开发流程基本上是这样一个节奏:PlanAhead为软硬件结合的载体,在此可以设计硬件,然后将硬件导出到软件设计。基本流程如图: 这里三个...

2019-10-06 2672

Verilog实现UART之二:发送模块

当并行数据准备好后,如果得到发送指令,则将数据按UART协议输出,先输出一个低电平的起始位,然后从低到高输出8个数据位,接着是可选的奇偶校验位,最后是高电平的停止位; 由于发送时...

2017-02-09 1048

编辑推荐厂商产品技术软件/工具OS/语言教程专题

| 电机控制 | DSP | 氮化镓 | 功率放大器 | ChatGPT | 自动驾驶 | TI | 瑞萨电子 |

| BLDC | PLC | 碳化硅 | 二极管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 无刷电机 | FOC | IGBT | 逆变器 | 文心一言 | 5G | 英飞凌 | 罗姆 |

| 直流电机 | PID | MOSFET | 传感器 | 人工智能 | 物联网 | NXP | 赛灵思 |

| 步进电机 | SPWM | 充电桩 | IPM | 机器视觉 | 无人机 | 三菱电机 | ST |

| 伺服电机 | SVPWM | 光伏发电 | UPS | AR | 智能电网 | 国民技术 | Microchip |

| 开关电源 | 步进电机 | 无线充电 | LabVIEW | EMC | PLC | OLED | 单片机 |

| 5G | m2m | DSP | MCU | ASIC | CPU | ROM | DRAM |

| NB-IoT | LoRa | Zigbee | NFC | 蓝牙 | RFID | Wi-Fi | SIGFOX |

| Type-C | USB | 以太网 | 仿真器 | RISC | RAM | 寄存器 | GPU |

| 语音识别 | 万用表 | CPLD | 耦合 | 电路仿真 | 电容滤波 | 保护电路 | 看门狗 |

| CAN | CSI | DSI | DVI | Ethernet | HDMI | I2C | RS-485 |

| SDI | nas | DMA | HomeKit | 阈值电压 | UART | 机器学习 | TensorFlow |

| Arduino | BeagleBone | 树莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 华秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |