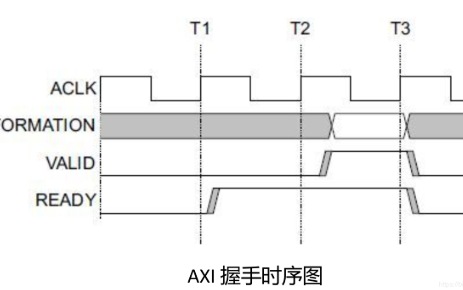

Zynq中AXI4-Lite功能 AXI4-Lite接口是AXI4的子集,专用于和元器件内的控制寄存器进行通信。AXI-Lite允许构建简单的元件接口。这个接口规模较小,对设计和验证方面的要求更少

2020-09-27 11:33:02 8051

8051

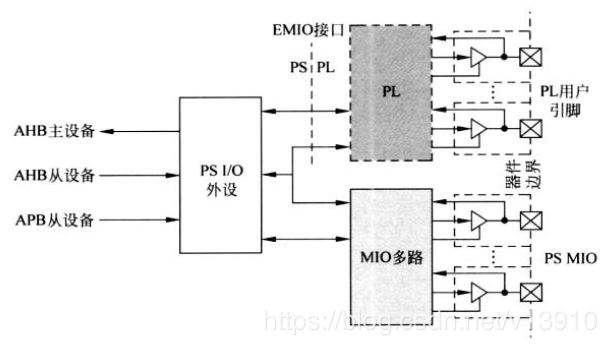

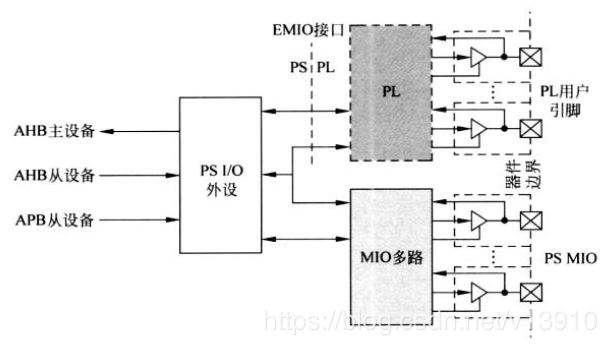

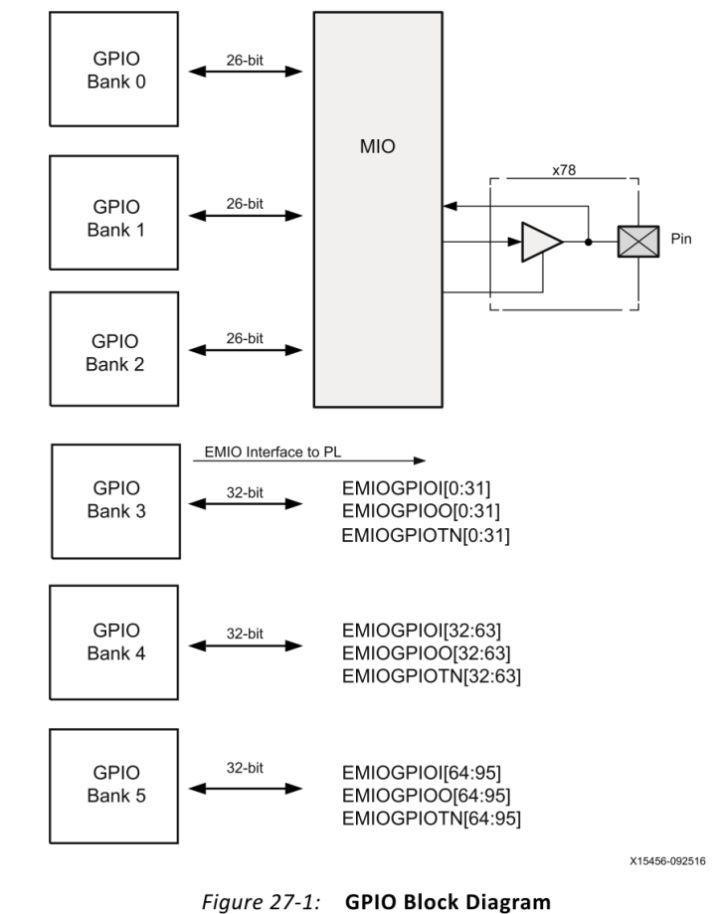

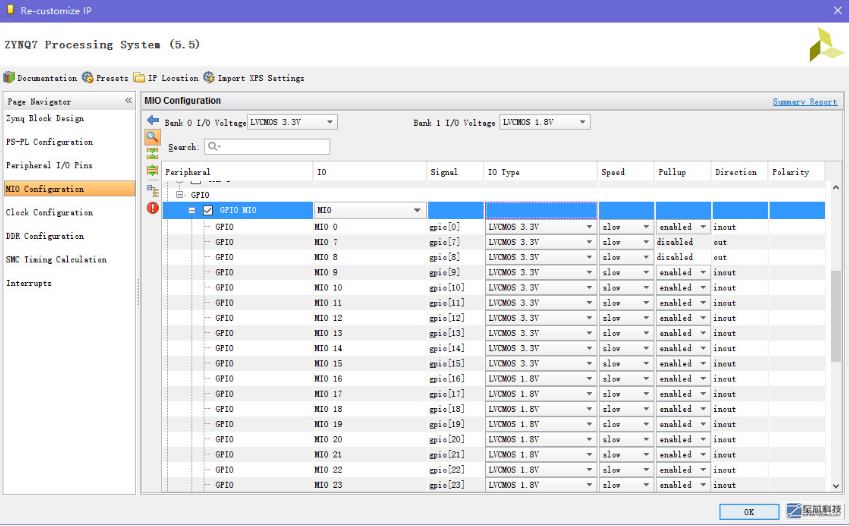

通过AXI点亮PL端LED。 1. MIO与EMIO 首先来理清楚MIO与EMIO的关系。MIO是PS的I/O引脚,一共有54个,分为Bank0与Bank1,可以接许多外设比如UART、SPI或GPIO

2020-11-24 14:32:33 20373

20373

4 版本。 AXI总线 ZYNQ有三种AXI总线: (A)AXI4:(For high-performance memory-mapped requirements.)主要面向高性能地址映射通信的需求

2020-12-04 12:22:44 6179

6179

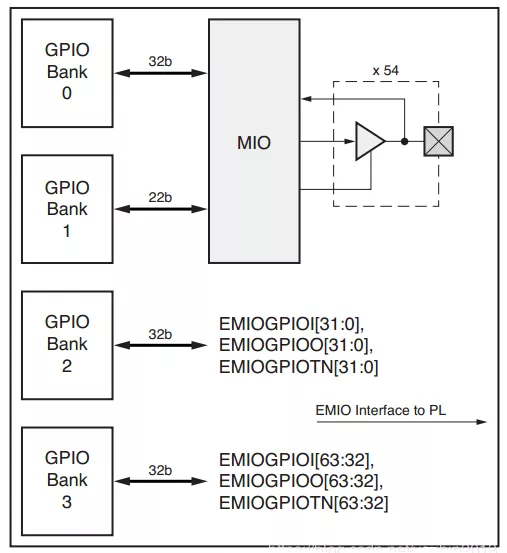

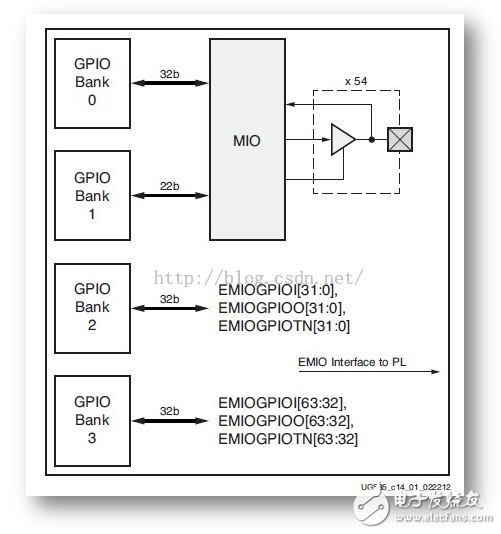

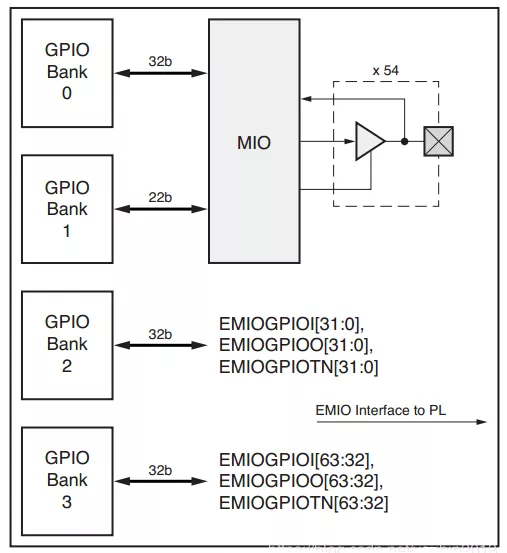

GPIO的结构体系 zynq的GPIO,分为两种,MIO(multiuse I/O)和EMIO(extendable multiuse I/O)。 ZYNQ的GPIO由4个BANK组成,其体系结构

2020-12-09 11:41:46 3059

3059

FPGA+ARM是ZYNQ的特点,那么PL部分怎么和ARM通信呢,依靠的就是AXI总线。这个实验是创建一个基于AXI总线的GPIO IP,利用PL的资源来扩充GPIO资源。通过这个实验迅速入门

2020-12-25 14:07:02 2957

2957

前言: ZYNQ 7000有三种GPIO:MIO,EMIO,AXI_GPIO MIO是固定管脚的,属于PS,使用时不消耗PL资源;EMIO通过PL扩展,使用时需要分配管脚,使用时消耗PL管脚资源

2020-12-26 10:12:57 3306

3306

一、AXI DMA介绍 本篇博文讲述AXI DMA的一些使用总结,硬件IP子系统搭建与SDK C代码封装参考米联客ZYNQ教程。若想让ZYNQ的PS与PL两部分高速数据传输,需要利用PS的HP

2020-12-31 09:52:02 7166

7166

如果想用PS点亮PL的LED灯,该如何做呢?一是可以通过EMIO控制PL端LED灯,二是通过AXI GPIO的IP实现控制。本章介绍如何使用EMIO控制PL端LED灯的亮灭。同时也介绍了,利用EMIO连接PL端按键控制PL端LED灯。

2021-01-30 10:05:00 6730

6730

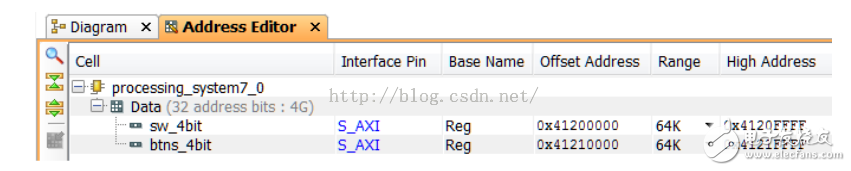

使用zynq最大的疑问就是如何把PS和PL结合起来使用,在其他的SOC芯片中一般都会有GPIO,本实验使用一个AXI GPIO的IP核,让PS端通过AXI总线控制PL端的LED灯,实验虽然简单,不过可以让我们了解PL和PS是如何结合的。

2021-02-01 10:06:00 6183

6183

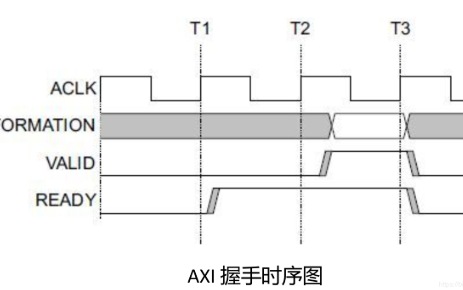

1、AXI接口协议详解 AXI 总线 上面介绍了AMBA总线中的两种,下面看下我们的主角—AXI,在ZYNQ中有支持三种AXI总线,拥有三种AXI接口,当然用的都是AXI协议。其中三种AXI总线

2022-10-14 15:31:40

AXI 总线上面介绍了AMBA总线中的两种,下面看下我们的主角—AXI,在ZYNQ中有支持三种AXI总线,拥有三种AXI接口,当然用的都是AXI协议。其中三种AXI总线分别为:AXI

2022-04-08 10:45:31

ZYNQ-7000系列MIO/EMIO/AXI_GPIO接口

2021-02-02 07:30:07

本帖最后由 何立立 于 2018-1-9 15:03 编辑

ZYNQ 、AXI协议、PS与PL内部通信 三种AXI总线分别为:AXI4:(For high-performance

2018-01-08 15:44:39

ZYNQ AXI RRESP ERR。发生RRESP时会发生什么?如何独立检测这个错误?现在,当rresp发生错误时,axi读取函数xil_in32只是失速?有任何超时或不同的方式来阅读这个错误。

2020-05-18 06:29:17

。1 axi_gpio_led_demo案例1.1 案例功能案例功能:PS端通过AXI4-Lite总线发送命令至PL端AXI GPIO IP核,IP核再根据命令控制评估底板PL端LED5的状态图

2021-05-28 14:28:28

上,也可以通过 EMIO 连接到 PL 端的引脚。Zynq-7000 系列芯片一般有 54 个 MIO,个别芯片如 7z007s 只有 32 个。GPIO 是英文“general purpose I

2022-02-08 07:27:16

大部分器件的接口要求,提供互联架构的灵活性与独立性。

(1)AXI总线

总线是一组传输通道,是各种逻辑器件构成的传输数据的通道,一般由数据线、地址线、控制线等构成。在ZYNQ中支持三种AXI总线

2023-11-03 10:51:39

ZYNQ学习笔记_GPIOGPIO介绍MIO介绍EMIO介绍控制GPIO接口的寄存器原理GPIO介绍GPIO的英文全称为General-purpose input/output,即一种通用外设,可以

2022-02-08 07:30:36

进行编程的初步PS和PL。如果上面有必要的信息,请提供。7.请提供ZYNQ 7Z020-CLG484芯片的所有I / O文档8.如何在没有AXI的情况下将处理器(PS)地址,数据,WRB,RDB连接到PL)。如何使用emio PINS来PL和PL到PS)。请提供必要的信息

2020-03-12 14:39:42

大家好,有一个AXI VDMA IP,它可以很好地使用HP端口从zynq zc706上的PS DDR获取1920x1080 @ 60Hz视频。我们可以使用相同的IP在zynq zc706上使用HP

2019-04-09 06:10:12

三种常见的PCB错误是什么

2021-03-12 06:29:32

Teledyne e2v为系统设计师提供的定制方案处理器功耗的背景知识三种调整处理器系统功耗的方法

2021-01-01 06:04:09

三种远程测控终端(RTU)产品之间的比较

2021-05-28 06:27:08

本帖最后由 一只耳朵怪 于 2018-5-25 14:55 编辑

DM6446内核有三种频率,有三种处理速度;这个速度和频率是对应的吗?由什么决定?最多可以接多少个TVP5146(单片传输速度不够)?

2018-05-25 06:47:06

FCC三种认证方式主要是针对不同类别产品。无线、射频类产品必须申请FCC ID,电脑及电脑周边产品需申请FCC DOC或ID,其它产品一般申请FCC VOC即可。三种认证方式中级别ID最高,需TCB

2015-10-22 14:11:47

HAL库中UART的三种收发方式是什么?

2022-02-18 06:33:52

HFSS三种辐射边界的区别与选择技巧是什么?

2021-05-21 06:54:59

Verilog使用。在搜索谷歌寻找答案后,我认为问题是,硬件引脚没有连接到PL。看起来他们必须从MIO的EMIO重定向到PL。但这仍然无法解决我的问题。我该怎么做,以后如何从Verilog访问它们?我

2020-03-16 10:29:49

QSPI特点QSPI三种工作模式

2020-12-31 06:36:55

如何在不同的下载方式中选择STM32的启动模式呢?STM32三种BOOT启动方式的设置与应用分别是什么?

2022-01-18 07:01:55

STM32三种启动方式是什么

2021-12-15 07:16:54

STM32三种启动模式对应的存储介质是什么?

2022-01-27 07:00:03

STM32的三种Boot模式有何差异呢?如何去验证这种差异呢?

2021-11-26 07:15:38

浅识STM32的三种boot模式文章目录浅识STM32的三种boot模式任务摘要一、认识boot1.三种BOOT模式介绍2.开发BOOT模式选择3.STM32三种启动模式4.三种模式的存储地址二

2021-12-10 07:46:37

USB设备端点有三种操作模式,包括自动验证模式、手动验证模式和Fly模式。 它们的功能是什么?

2020-12-03 06:46:02

大家好,我的设计是针对ZynQ FPGA(Vivado2013.3),它在PL和PS逻辑中具有PCIe(AXI PCIE桥)。当我尝试生成位文件时,由于3个警告,实现失败。他们是[Common

2018-10-22 11:18:06

while的三种使用形式是什么样的?

2021-11-02 08:35:34

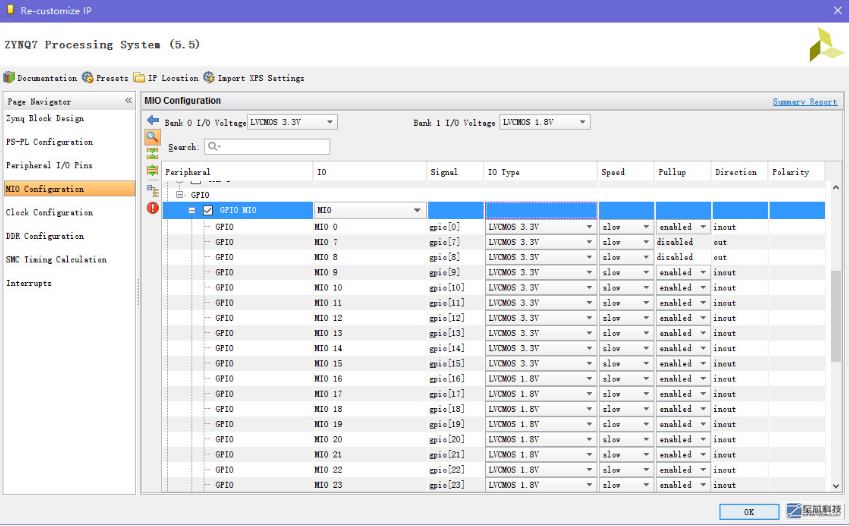

zynq芯片集成了两片arm a9的内核,和xilinx的fpga可编程部分集成在一块芯片上面。刚开始学习的时候使用vivado,现在已经在纯玩Linux了。第一步:选择MIO

2015-06-14 14:27:17

持PS+PL的架构,灵活使用PL。Zynq上的存储器接口也很丰富,包括DDR控制器,Quad-SPI控制器、Nand/NOR/SRAM控制器等。通用IO(GPIO)在Zynq上,我们可以通过MIO引出最多54个

2015-07-07 20:22:49

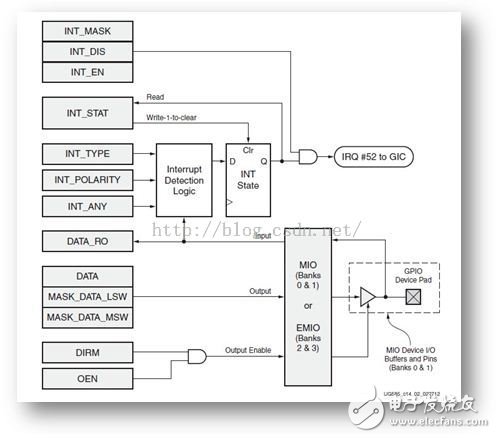

)简称为GPIO,中文意思为通用IO口,很多简单控制开关的设备只需要开关两种状态就可以来了,用传统的串口显得复杂,所以嵌入式微处理器通常用IO口即可。本文主要介绍Zynq的GPIO基本原理和相关寄存器配置

2015-07-17 12:44:38

catalog中选择zynq 7000 system6、击上图 32b GP AXI master ports的绿色方框,选择general项。确认Enable GPIO on EMIO

2015-06-25 21:31:50

原子公众号,获取最新资料第三章GPIO之EMIO按键控制LED实验PS和外部设备之间的通信主要是通过复用的输入/输出(Multiplexed Input/Output,MIO)实现的。除此之外,PS还可

2020-08-29 16:20:36

通过EMIO连接到PL端的引脚。Zynq-7000系列芯片一般有54个MIO,个别芯片如7z007s只有32个。 GPIO是英文“general purpose I/O”的缩写,即通用的输入/输出

2020-08-29 16:17:15

原子公众号,获取最新资料第四章GPIO之MIO按键中断实验中断是一种当满足要求的突发事件发生时通知处理器进行处理的信号。中断可以由硬件处理单元和外部设备产生,也可以由软件本身产生。对硬件来说,中断信号

2020-08-29 16:21:47

一灯双控的三种接线方法有哪些利弊

2021-03-11 07:10:04

什么是AXI GPIO触发类型?当我按下按钮时,它会触发中断,当我松开按钮时,它也会触发中断,我该如何设置触发类型?请帮忙!

2020-04-10 10:49:05

什么是Boot模式?STM32三种Boot模式有什么差异?怎么实现STM汇编程序设计?

2021-11-29 06:04:54

本文逐一介绍三种视频数字接口的标准。

2021-06-03 06:24:31

一般伺服都有三种控制方式:速度控制方式,转矩控制方式,位置控制方式。大多数人想知道的就是这三种控制方式具体根据什么来选择的?

2021-01-29 07:28:36

伺服电机的三种控制方式

2021-01-21 06:45:01

伺服有哪几种控制方式?伺服的三种控制方式具体根据什么来选择的?

2021-10-11 08:17:43

RJ45插头实现GE_T模式的电口应用。Zynq-7000 PS部分包含两个千兆以太网MAC层硬核,因此还需要以太网物理层传输芯片实现千兆以太网接口。MAC层硬核所对应的接口引脚,既可从PS端的MIO引脚

2021-10-22 09:43:10

从不同的侧重点给出了几种拓扑,将对其进行分析比较三种拓扑有其各自的有缺点,如何来选择它们?

2021-04-07 06:05:16

刷机时用到的三种工具分别是什么?SD卡有何作用?fastboot是什么?fastboot有何作用?

2021-12-27 06:18:48

你好我有Zynq 7z020板,我想访问它的GPIO,但我找不到Zynq处理器文档,所以我知道如何访问Zynq GPIO?问候

2019-09-11 10:48:04

嵌入式三种定时器的区别在哪?嵌入式三种定时器的特点分别有哪些呢?

2021-12-27 06:49:27

常用的FBAR模型有哪三种?

2021-03-11 06:16:18

蓝牙无线组网的优点是什么?常见的三种无线接入方式是什么?蓝牙无线组网原理与上网方案分享

2021-05-26 06:33:11

LABVIEW 小白 想做一个轴承故障检测系统 需要选择轴承内圈外圈滚子三种故障计算公式算出的结果 要用枚举控件有人能给编一下吗就类似于用枚举控件选择三种不同类型的数值 可用数值常量代替

2018-04-27 16:51:41

`玩转Zynq连载2——Zynq PS的GPIO外设更多资料共享 链接:https://share.weiyun.com/5s6bA0s1 概述 Zynq的GPIO外设控制最多54个MIO引脚,也

2019-04-18 16:33:51

GPIO的PS系统配置打开ZYNQ7 ProcessingSystem的配置页面Peripheral I/O Pins,可以看到右侧若勾选GPIO MIO选项,在对应的MIO号若点击变绿,则表示该MIO号

2019-10-10 11:21:06

的就是PL的引脚)。关于MIO和EMIO的关系,更形象直接的可以示意如图所示。MIO和EMIO都是PS的一部分,但是MIO可以直接连接到Zynq芯片的引脚上,和PL无关;而EMIO需要通过PL的IO

2019-10-12 17:35:16

` 1概述Zynq将ARM和FPGA整合到了一个芯片上,它的过人之处不仅是功耗、面积、成本的优化,更多的是将二者之间原本极为受限的数据交互方式转移到芯片内部完成,4条AXI GP通道(2个从机、2个

2019-11-12 10:23:42

1概述AXI HP总线是Zynq芯片非常重要的一个功能,它可以实现Cortex A9与PL之间大吞吐量的数据通信。可以说,Zynq芯片最大的卖点恐怕就是这条总线。对不起,不是1条,是4条这样的AXI

2019-11-26 09:47:20

不同通道使用情况下的数据吞吐量。大家可以在此基础上,更改不同的AXI HP总线时钟频率,以评估时钟频率对AXI HP总线的影响。2 AXI总线协议介绍参考文档《玩转Zynq-基础篇:AXI总线协议介绍

2019-11-28 10:11:38

●在从机与互联总线之间 ●在主机与从机之间大多数系统使用以下三种互联方式中的一种: ●地址和数据总线共享 ●地址共享,有多个数据总线 ● 多层互联,即有多个地址和数据总线在大多数系统中,对地址通道

2019-05-06 16:55:32

第三种WiFi模块是什么?有什么特点?

2021-05-14 06:49:07

编译的三种类型是什么?ARM_Linux制作嵌入式远程调试工具

2021-12-24 06:42:58

原理图的Grid Preset的默认情况下有三种设置,请问这三种设置有什么区别,是怎么使用的

2019-04-10 07:35:06

请群主详细解释下这三种启动方式,看了参考资料不是很明白其意!谢谢!

2019-07-17 04:35:12

进程类型进程的三种状态

2021-04-02 07:06:39

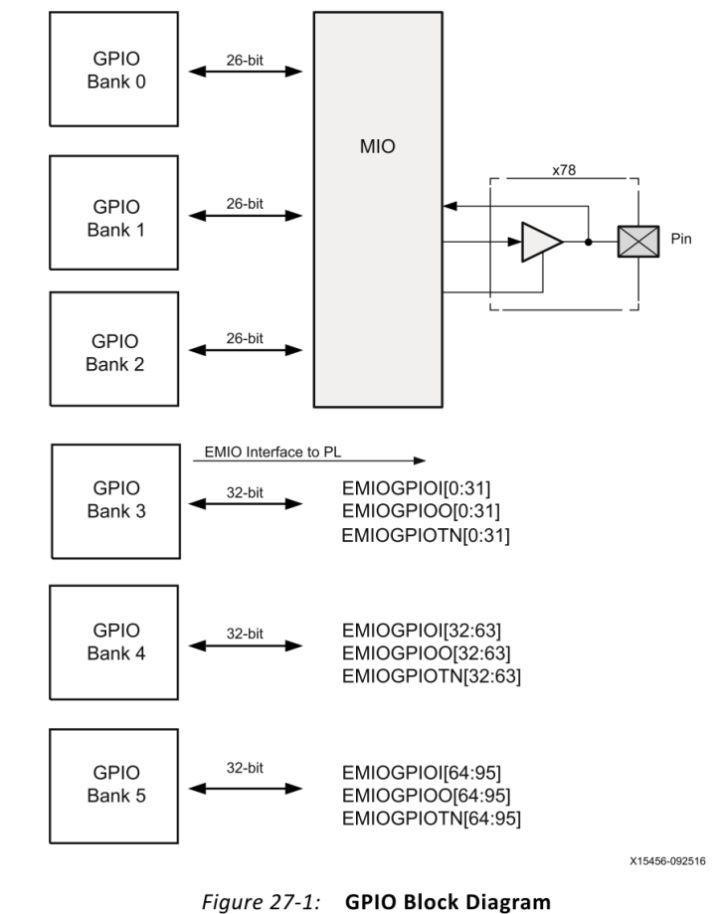

通过EMIO布线到PL; c)新增了四通道的高速GTR收发器; d)DDR控制更新到可支持DDR4L-2400速率。 (1)MIO资源 Zynq UltraScale+具有78个可配置复用的MIO,这些MIO可用作将PS内的相关外设控制器引出,同时

2017-02-08 08:29:11 491

491

本文主要介绍zynq linux AXI DMA传输步骤教程,具体的跟随小编一起来了解一下。

2018-07-08 05:46:00 29549

29549

我们先看有哪三种GPIO:MIO、EMIO、AXI_GPIO。其中MIO和EMIO是直接挂在PS上的GPIO。而AXI_GPIO是通过AXI总线挂在PS上的GPIO上。

2018-07-07 08:23:00 4944

4944 GPIO功能,PS部分通过M_AXI_GP接口来控制该GPIO IP模块;另外EMIO模块虽然使用PS部分GPIO但也使用了PL部分的管脚资源。MIO方式实现GPIOvivado中zynq设置如下图由图中

2018-08-07 10:16:49 2708

2708

Zynq-7000 PL端HDMI的显示控制 Zynq-7000 PS到PL端emio的使用 Vivado 专家文章:Tcl 是什么? Zynq-7000 ARM端MIO的使用 Zynq

2019-09-15 14:57:00 3305

3305 了解MIO和EMIO如何相关以及如何使用首选的PlanAhead / XPS流将信号传递到“真实世界”。

2018-11-26 06:27:00 3272

3272 如何设计高效的 PL 和 PS 数据交互通路是 ZYNQ 芯片设计的重中之重。AXI 全称 Advanced eXtensible Interface,是 Xilinx 从 6 系列的 FPGA 开始引入的一个接口协议,主要描述了主设备和从设备之间的数据传输方式。

2020-03-15 17:04:00 10317

10317

PS部分框图如上图所示,PS 和外部接口之间的通信主要是通过复用的输入 / 输出( Multiplexed Input/Output,MIO)实现的,它提供了可以做灵活配置的 54 个引脚,这表明外部设备和引脚之间的映射是可以按需定义的。

2020-08-27 14:30:35 4024

4024

为了简化使用GPIO,编写了以下脚本。使用下列脚本,一条命令就能设置一个GPIO的输出值。脚本接受两个输入参数。第一个参数表示GPIO编号,MIO GPIO从0开始,EMIO GPIO从78开始。第二个参数是输出值。如果输出值是1,可以省略第二个参数。

2020-09-03 09:50:19 2520

2520

在ZYNQ中,支持AXI-Lite,AXI4和AXI-Stream三种总线,但PS与PL之间的接口却只支持前两种,AXI-Stream只能在PL中实现,不能直接和PS相连,必须通过AXI

2020-09-24 09:50:30 4289

4289

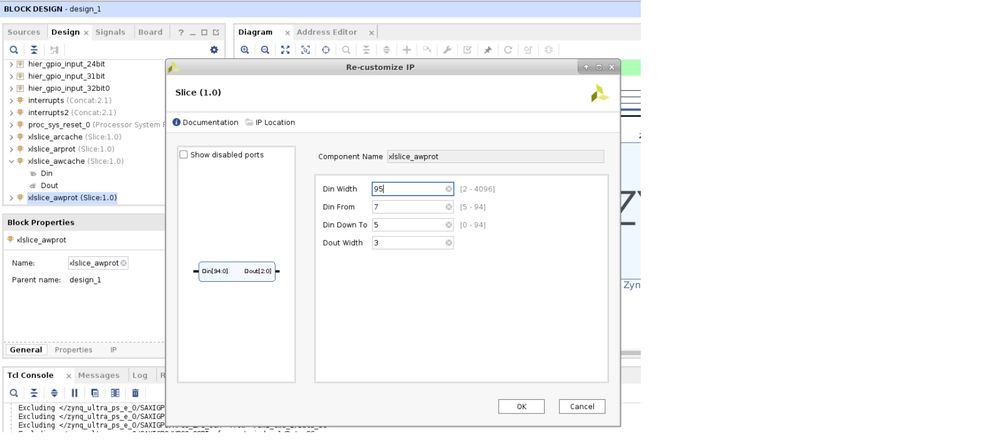

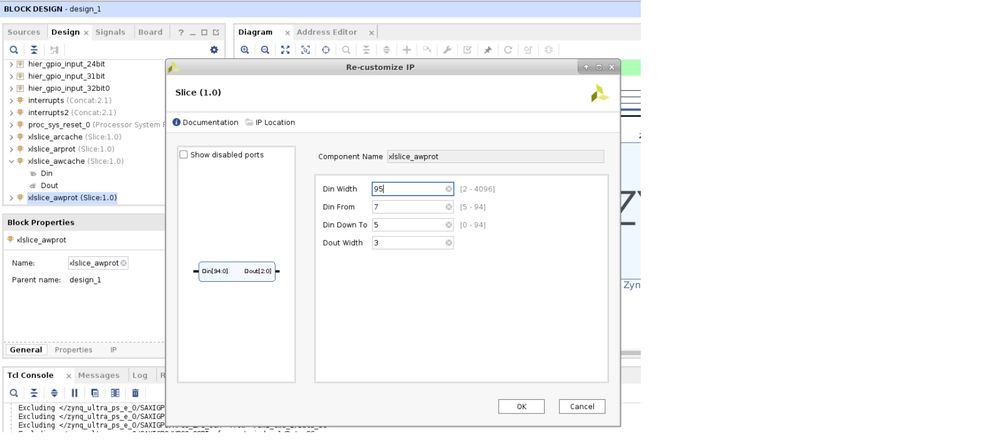

MPSoC 为PL提供了96个GPIO,通过EMIO管脚链接到PL。 普通PL设计,一般只会用到几个GPIO管脚。可以使用Vivado IPI中的Slice IP, 从其中分出指定数量的管脚

2020-11-04 14:57:17 1499

1499

引言 近来,几乎每个赛灵思 IP 都使用 AXI 接口。Zynq、Zynq MP、MicroBlaze 和全新的 Versal 处理器都无一例外使用 AXI 接口。因此,AXI 接口已成为几乎所有

2020-09-27 11:06:45 5857

5857

带宽会受限于SPI接口有效速率,本文采用芯片为W5500,支持10M/100M自适应,其理论值高达80Mbps,基本达到算法验证的要求。 ZYNQ可以通过灵活的EMIO模拟SPI接口,从而在最少改动官方demo的前提下移植C语言驱动程序。本文着重讲述EMIO的C语言软件驱动方式及可重用封装

2020-12-25 17:22:19 1888

1888 不同类型的DMA GPIO PL general purpose AXI GP AXI utlilizing PS DMAC High performance w/DMA ACP w/DMA 几种

2020-10-09 18:05:57 6391

6391

和接口的构架 在ZYNQ中,支持AXI-Lite,AXI4和AXI-Stream三种总线,但PS与PL之间的接口却只支持前两种,AXI-Stream只能在PL中实现,不能直接和PS相连,必须通过

2020-11-02 11:27:51 3880

3880

学习重点包括 MIO、 EMIO 的使用,中断资源的使用,熟悉了解 ZYNQ 中断的库函数,学会推导 XILINX SDK 中断函数的构架,掌握 AXI-LITE 总线协议,掌握自定义 IP 的创建,封装。掌握 VIVADO 软件的调试技巧等。

2020-11-09 08:00:00 3

3 ZYNQ-7000系列MIO/EMIO/AXI_GPIO接口

2022-07-25 17:41:58 2046

2046

ZYNQ-7000系列MIO/EMIO/AXI_GPIO接口

2021-01-31 06:50:04 12

12 。如图2.1所示,在相对较高层次对比了三种器件。Zynq MPSoC的PS部分比Zynq的PS部分面积更大,也更复杂。本章,将介绍这三种器件的特点。 2.1 技术时间线 进一步介绍之前,需要指出这三种

2021-04-02 17:20:14 13783

13783

上,也可以通过 EMIO 连接到 PL 端的引脚。Zynq-7000 系列芯片一般有 54 个 MIO,个别芯片如 7z007s 只有 32 个。GPIO 是英文“general purpose I/O”的缩写,即通用的输入/输出。是 ZYNQ PS 中的一个外设,用于观测和控制器件引脚的状态。图 1

2021-12-04 18:51:06 16

16 ZYNQ学习笔记_GPIOGPIO介绍MIO介绍EMIO介绍控制GPIO接口的寄存器原理GPIO介绍GPIO的英文全称为General-purpose input/output,即一种通用外设,可以

2021-12-04 19:36:10 10

10 [导读] 前面写过篇介绍ZYNQ基本情况的文章,今天来肝一篇实战文章介绍AXI quad SPI 使用方法,如果你正使用ZYNQ的这个IP,希望对你有所...

2022-01-26 17:01:47 6

6 这篇博文特别关注 Zynq SoC 的多用途 IO (MIO, Multipurpose IO) 模块。

2022-03-30 11:43:29 1452

1452 前面简单学习了关于GPIO的操作,本次将使用PL 端调用 AXI GPIO IP 核, 并通过 AXI4-Lite 接口实现 PS 与 PL 中 AXI GPIO 模块的通信。

2022-07-19 17:36:52 3230

3230 zynq 中带有两个硬核千兆以太网MAC,ENET0,ENET1。与普通SOC 芯片不同,zynq PS 断地外设可以通过MIO连接到芯片的引脚上,也可以通过EMIO 接口连接到PL 端。连接到PL端后,带来了灵活性,可以转换成各种接口。比如设计一个交换机。定义端其它的引脚。

2022-09-23 15:19:58 2023

2023 Zynq UltraScale+ PS MIO 可能在 VCCO_PSMIO 电源上电缓升期间输出高位毛刺

2023-07-10 16:47:39 490

490

Xilinx 从 Spartan-6 和 Virtex-6 器件开始采用高级可扩展接口 (AXI) 协议作为知识产权 (IP) 内核。Xilinx 继续将 AXI 协议用于针对 7 系列和 Zynq-7000 All Programmable SoC 器件的 IP。

2023-09-27 09:50:27 594

594

电子发烧友App

电子发烧友App

评论