Zynq7000系列芯片有54个MIO,可以在XPS环境下将这些MIO直接配置为外设的引脚,不需要添加约束文件,MIO信号对PL部分是透明的,不可见。同时Zynq可以配置多达63个EMIO引脚,这些引脚可以配置到PL部分,也可以配置为外设的引脚,不过需要添加约束文件指定封装引脚。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

封装

+关注

关注

128文章

9146浏览量

147907 -

赛灵思

+关注

关注

33文章

1797浏览量

133154 -

Zynq

+关注

关注

10文章

625浏览量

49243

发布评论请先 登录

相关推荐

热点推荐

如何在AMD Vitis Unified IDE中使用系统设备树

您将在这篇博客中了解系统设备树 (SDT) 以及如何在 AMD Vitis Unified IDE 中使用 SDT 维护来自 XSA 的硬件元数据。本文还讲述了如何对 SDT 进行操作,以便在 Vitis Unified IDE 中实现更灵活的使用场景。

Zynq7100 BSP移植,MSH终端不能正确显示是为什么?

由于新版本的RT Thread的BSP不再提供Zynq7000的支持。所以同事从RT Thread(4.0.3)中的Zynq7000移植了一份Zynq 7100的BSP。但是MSH终端和串口输出

发表于 09-19 06:26

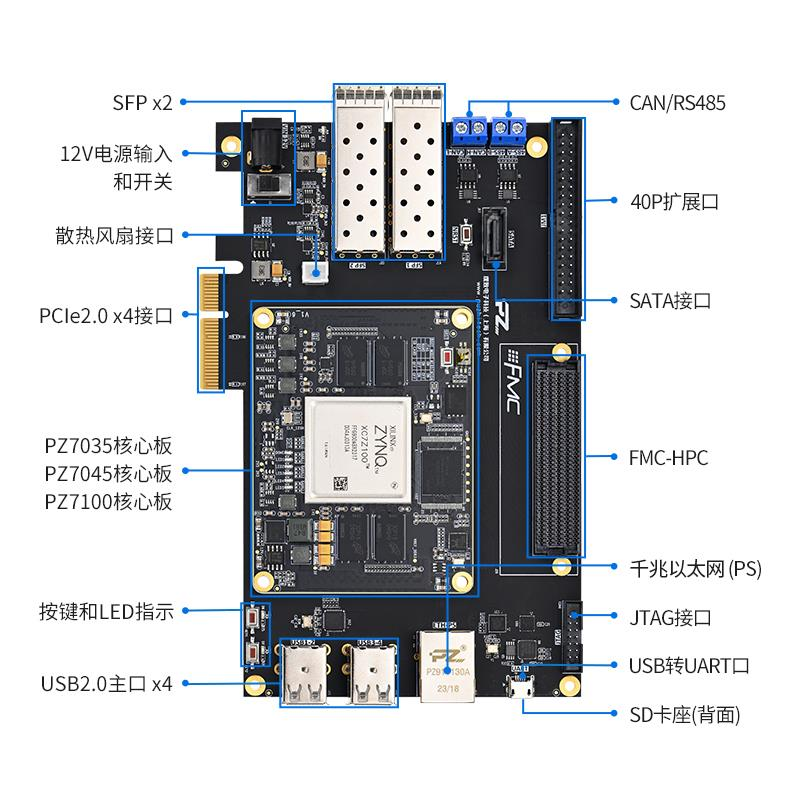

fpga开发板 璞致ZYNQ 7000 系列之 PZ7035/PZ7045/PZ7100-FH 核心板与开发板用户手册

本文介绍了Xilinx Zynq-7000系列可扩展处理平台及其开发板应用。Zynq-7000采用双核ARM Cortex-A9处理器与28nm FPGA架构,支持高性能嵌入式开发。开发板采用核心板

Zynq-7000 SoC与7系列设备内存接口解决方案数据手册

技术手册,适用于使用LogiCORE IP核(如DDR3/DDR2 SDRAM、RLDRAM II、QDRII+)进行存储器接口设计26。核心功能:IP核配置与时序:详细说明Xilinx MIG(Memory Interface Generator)IP核的使用方法,包括信号定义、时序约束、物理层(PHY

发表于 07-28 16:17

•3次下载

LPC1227FBD48如何在没有SDK的情况下配置FreeRTOS?

我想在基于 LPC1227FBD48 系列的现有项目中使用 FreeRTOS,但我们没有可用于控制器的 SDK。我们如何在没有 SDK 的情况下配置 FreeRTOS。

发表于 04-02 06:33

Zynq7000处理器的配置详解

添加好ZYNQ7 Processing System IP核后,需要对其进行配置,双击弹出如下窗口。绿色部分表示ZYNQ PS部分中可配置的项目,可以双击转向相应的设置界面,也可以直接

从零开始驯服Linux(一):ZYNQ-Linux启动文件构建全解析

码:zdyz资料盘B盘:https://pan.baidu.com/s/1NNYDCpEkM2jd6jR69Y1mfg 提取码:zdyz

1.2安装ZYNQ-7000交叉编译工具链编译uboot和内核

发表于 03-20 16:48

如何在MATLAB中使用DeepSeek模型

在 DeepSeek-R1(https://github.com/deepseek-ai/DeepSeek-R1) AI 模型横空出世后,人们几乎就立马开始询问如何在 MATLAB 中使用这些模型

如何在Windows中使用MTP协议

、图片等)的通信协议,它被广泛用于Android设备。以下是如何在Windows中使用MTP协议的详细步骤: 1. 确保设备支持MTP 首先,你需要确认你的设备支持MTP协议。大多数现代Android

DCS控制系统的配置与实施流程

DCS(分布式控制系统)控制系统的配置与实施流程是一个复杂但有序的过程,涉及多个步骤和环节。以下是一个典型的DCS控制系统配置与实施流程: 一、筹备工作 确定需求 :明确控制系统的控制

基于Xilinx ZYNQ7000 FPGA嵌入式开发实战指南

电子发烧友网站提供《基于Xilinx ZYNQ7000 FPGA嵌入式开发实战指南.pdf》资料免费下载

发表于 12-10 15:31

•39次下载

如何在Zynq-7000的PlanAhead/XPS流程中使用MIO与EMIO配置

如何在Zynq-7000的PlanAhead/XPS流程中使用MIO与EMIO配置

评论