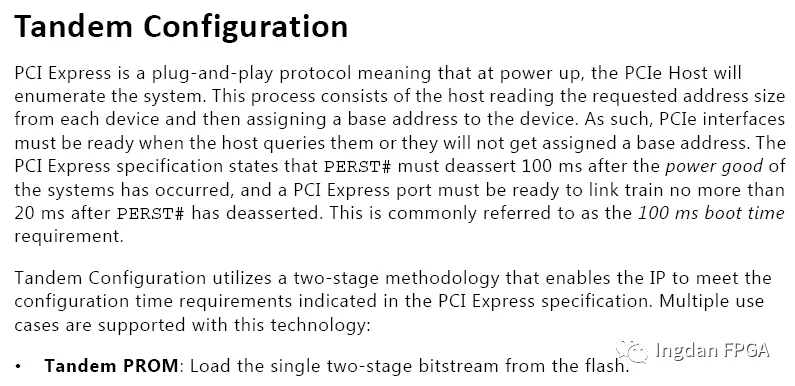

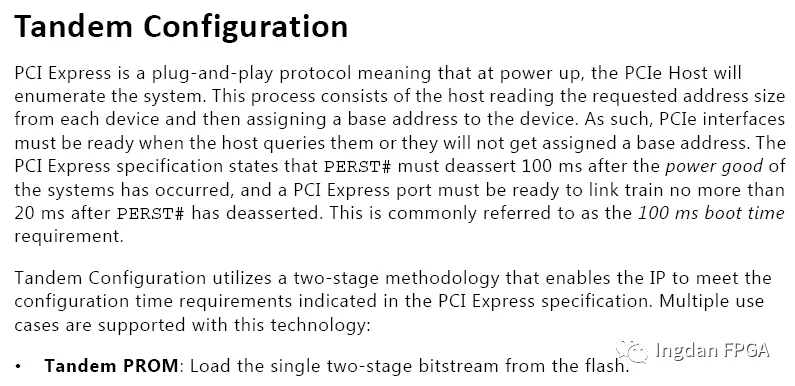

现在大规模FPGA的bitstream比较大导致板卡从上电到FPGA配置完成的时间远远超过100MS的要求,从而电脑端无法正常识别到PCIE设备。为此Xilinx的PCIE Tandem功能是专为满足PCIe设备在100ms之内枚举起来要求而设计的。

2022-08-02 08:03:43 2455

2455

本文我们将向大家介绍PCIe引脚定义以及PCIe协议层。

2023-09-26 11:39:14 5665

5665

最近弄PCIE,遇到一个问题,以前我们总认为:Xilinx的PCIE core的管脚是固定的,即指定了PCIE core的位置,对应的管脚也就指定了,真实情况是怎么样的呢?

2023-11-17 17:02:52 1362

1362

Xilinx7系列普及讲座内容请下载附件pdf,更多内容请登录www.rocetech.com

2013-03-31 14:09:45

Xilinx7系列普及讲座内容请下载附件pdf,更多内容请登录www.rocetech.com

2013-03-31 14:20:25

Xilinx7系列普及讲座内容请下载附件pdf,更多内容请登录www.rocetech.com

2013-03-31 14:27:04

PCIE-52P90H

2023-03-29 22:43:17

我想用C6657的PCIE接口扩展一个WIFI.

C6657的PCIE需要一个LVDS的参考时钟(PCIECLKP, PCIECLKN), WIFI芯片的PCIE需要一个HCSL的参考时钟

2018-06-21 18:45:06

) 使用最新 XILINX 官方 XDMA 驱动,稳定可靠;4) 支持 16 路用户中断;5) 支持 XILINX 7 系列以上的全系 FPGA;6) 5.支持 Windows/Linux 系统;二、 低

2021-05-19 08:58:02

可达7.68TB。出于对数据中心这种密集型用例的考量,CD7 E3.S系列占用较少的PCIe通道数,因此可在机架内搭载更多的PCIe SSD或加速器,这也就意味着更大的存储空间和更高的算力。CD7采用

2021-12-11 08:00:00

和AMBA ACE协议和ARM架构。

该文档涵盖以下主题:

·本文档中使用的术语说明。

·针对PCIe事务的ARM内存类型使用指南。

·如何遵守ARM处理元件(PE)的PCIe事务的ARM内存模型要求

2023-08-17 07:25:03

在DSP上运行的代码量很大,过程繁琐。

请问有没有方法将DSP程序直接在DSP上自启动,不需要通过Host PC发送。我想是否能实现板卡能通过PCIe模式启动时,自动加载flash中的DSP程序??

当然只要有方法能满足 将DSP中的数据通过PCIE传输至Host PC即可!

多谢大家!

2018-06-19 05:08:19

”,简写PCIe。2、AC耦合电容:高速差分信号电气规范要求PCIe发送端串联一个电容,进行耦合。3、链路类型与差分信号数量:X1:1对时钟差分信号,1对收发差分信号,单面pin数18pi...

2021-11-11 08:05:11

的主动状态电源管理(ASPM)。一般来说,无论是系统驱动端硬件(RC)还是设备硬件(EP)都可以通过检测pcie链路上的空闲时间,然后启动电源状态转移。有两种低功率链路状态:L0s,也叫L0

2021-12-28 06:18:35

的主动状态电源管理(ASPM)。一般来说,无论是系统驱动端硬件(RC)还是设备硬件(EP)都可以通过检测pcie链路上的空闲时间,然后启动电源状态转移。有两种低功率链路状态:L0s,也叫L0 st...

2022-01-03 08:00:09

亲爱的,我需要使用2-3个PCIe(x2)和一个Kintex 7 FPGA。实际上我正在查看系列7发现的数据表(在集成的IP资源下),可以只使用一个PCIe Gen 2。我是否正确理解了数据表?在此先感谢您的帮助。安东尼奥

2020-08-27 16:42:54

1特点 Xilinx 7 系列的提供的bank分为HP(High-performance)和HR(High-range)。HP主要为了满足高速内存的性能要求以及其他chip-to-chip接口

2020-12-23 17:17:47

Windows、Linux等操作系统,如Windriver6. 即插即用,支持热插拔本人已经在Xilinx评估板SP605,ML555,ML505,ML605和KC705,以及自制的PCIe金手指板卡上调试验证了

2014-03-01 18:11:32

前言TLK7-EVM是一款由广州创龙基于Xilinx Kintex-7系列FPGA自主研发的核心板+底板方式的开发板,可快速评估FPGA性能。核心板尺寸仅80mm*58mm,底板采用沉金无铅工艺的6

2020-09-24 14:39:36

pcie虚拟化技术中,一端pcie的虚拟通道又睡指定,是通过软件配置吗

2019-11-11 10:34:47

Artix 7的PCIe链路建立Ac701与主机Pc之间的通信。请使用UG964中描述的套件提供的测试示例:我们使用Questasim跟踪模拟流程,因此我们成功编译了xilinx库并启动

2019-09-10 07:56:36

。EC20 Mini PCIe系列模块包含EC20-E Mini PCIe、EC20-A Mini PCIe和EC20-C Mini PCIe三个版本,使其能够向后兼容现存的EDGE和GSM/GPRS网络,以确保在缺乏3G和4G网络的偏远地区也能正常工作。`

2018-06-05 17:38:23

6 6 Pin PCIe to (2) SATA 15 Pin

2024-03-14 22:02:05

PCIE BOARD 6 PORT DB-9

2023-03-22 20:41:28

MODULE CONV PCIE-SMA

2023-03-22 20:00:22

嗨论坛,我们在我们自己的载板上使用 Variscite 的 i.MX7D SoM。模块上的 SoC 无法启动,因为我们的板子没有 100 MHz外部 PCIe 参考时钟,并且内核挂起并显示以下

2023-04-23 08:03:17

嗨,在ML605设计中,信号“PCIE_250M_MGT1_P / N”从器件“ICS874001”驱动到PCIe MGT参考时钟。根据以下链接中给出的相位噪声值,http

2020-06-08 15:30:33

DEV SYSTEM P4080 PCIE

2023-03-22 19:55:54

你好成员,我开始接触Xilinx(仍然来自Altera)。我有一个带PCIe的Spartan 6连接套件。我得到它与USB,UART罚款和运行程序读/写内存。但是当我将PCIe安装到我的计算机中

2019-08-28 10:04:34

DEVELOPMENTSYSTEMT4240PCIE

2023-03-22 19:56:26

硬件加速。板卡设计满足工业级要求。如下图所示: 图 1:硬件加速卡实物图 二、技术指标图 2:硬件加速卡结构框图 标准PCIe半高、半长卡,符合PCI Express 3.0 规范。 支持PCIe x1

2019-10-25 16:00:50

1.08a”(“reset_pcie”和“mmcm_lock”) - 项目开始工作。我尝试启动标准项目,我从“xilinx.com”下载。 (“kc705-pcie

2020-07-14 16:19:52

口上)我用XILINX官方的XDMA PCIE驱动(2017版本和2018版本都试过)然后启动XDMA对PS DDR进行读或者写,单独读或者写(比如400KB数据),可以正常工作。但是,当我同时启动

2019-11-21 10:35:01

/axi_pcie3_0_pcie3_ip_pcie_7vx.v../axi_bridge/14.4/axi_pcie3_0/ip_2/source

2020-07-25 11:26:47

参考。1.“使用出厂镜像启动时发现无法正常启动”问题描述——客户自制底板去掉PCIe烧录出厂镜像,启动时出现的卡死信息:编辑切换为居中添加图片注释,不超过 140 字(可选)产生原因——PCIe

2022-09-15 17:04:06

实际上有时会出现日志下的问题

但是现在,当我尝试启动时,问题总是出现。

是什么原因 ??

bsp: binaries_auto_linux_bsp28.0_s32g274

U-Boot

2023-05-06 08:10:59

各位大神,请教一个问题。目前正在使用Xilinx新出的Vivado 软件生成DMA和PCIE集成的IP核,在此基础上又生成了一个example design,但是在仿真的时候报错。是Xilinx的这款产品不够成熟还是我操作有错误??各位大神有没有遇到此类问题的??

2017-01-13 21:56:41

背景:imx6qlinux-3.0.35内核参考飞凌自己做的板子,pcie接tw6869,内核配置中只选了PCIe,没有选RC两个子项,每次启动总是pcie link up failed,怀疑可能是

2022-01-10 07:46:24

:能使用xiinx 的PCIE ip核完成读写功能对以上课程有兴趣的同学点下面链接学习 : 明德扬FPGA课程_PCIE高速接口XILINX.ISE教程_哔哩哔哩_bilibili这只是我们明德扬课程

2022-02-14 09:50:22

紫光的logos系列的PGL50H/PGL100H、logos-2全系列都集成gen2×4的PCIE硬核,且官方也提供了例程。

紫光的PCIE用起来还是挺方便的,生成IP的同时生成了对应的PCIE

2023-11-17 14:35:30

嗨,PCIe-Spec定义在稳定供电后100ms,PCIe设备必须为链路训练做好准备。使用7系列Zynq设备无法达到此时间。我使用了两种方法来减少启动时间: - 优化FSBL以达到SPI控制器的最大

2020-06-09 16:42:15

FPGA pcie dma测试

流程:金手指和电脑连接之后,先加载程序,pc重启;

现象:pc无法开机。

FPGA pcie x8,pc x16,直接连接上去的

请问这是什么情况呀,为什么电脑开不了机呢?

2023-09-13 18:21:28

本帖最后由 一只耳朵怪 于 2018-5-25 15:02 编辑

系统:dm8168作为ep,启动方式为spi现在想仿真器访问8168的pcie寄存器区域,需要PRCM配置打开pcie,我

2018-05-25 08:39:50

,PCIe x167.支持Xilinx器件:Spartan-6,Virtex-5,Virtex-6,Artix-7,Kintex-7,Virtex-7,Kintex Ultrascale,Virtex

2020-11-25 22:27:25

硬件加速。板卡设计满足工业级要求。如下图所示: 图 1:硬件加速卡实物图二、技术指标图 2:硬件加速卡结构框图标准PCIe半高、半长卡,符合PCI Express 3.0 规范。支持PCIe x1、x4

2018-07-27 16:49:30

,主要用于FPGA硬件加速。板卡设计满足工业级要求。如下图所示: 图 1:硬件加速卡实物图 二、技术指标图 2:硬件加速卡结构框图 标准PCIe半高、半长卡,符合PCI Express 3.0 规范

2018-08-22 17:31:55

PC&HMI、工业机器人、机器视觉、 医疗影像、电力自动化等领域。 TL-A7HSAD采集卡是一款由广州创龙基于Xilinx Artix-7系列FPGA自主研发的高速数据采集卡,可配套广州创龙

2018-07-06 10:00:41

PC&HMI、工业机器人、机器视觉、 医疗影像、电力自动化等领域。TL-K7FMC采集卡是一款由广州创龙基于Xilinx Kintex-7系列FPGA自主研发的FMC数据采集卡,采用沉金无铅工艺

2018-07-06 10:32:44

PCIe是什么?有什么核心优势?Xilinx的PCIe端点模块的显著优势包括哪些?基于Virtex-5 LXT FPGA的PCIe端点该怎样去设计?

2021-05-26 06:39:11

基于kintex UltraScale XCKU060的双路QSFP+光纤PCIe 卡一、板卡概述 本板卡系北京太速科技自主研发,基于Xilinx UltraScale Kintex系列

2022-07-11 11:35:54

我是一名PCIe新手,想了解以下问题:

1、如何测试PCIe?

2、如何读写PCIe(两块开发板通过PCIe线互连,分别配置为RC和EP)?

3.如何支持NTB?

2023-06-12 06:05:51

并不理想。本文将讨论如何使用一个多点信号来分配PCIe时钟,而且仍满足PCIe第二代规范严格的抖动要求。

2019-09-26 07:56:41

并不理想。本文将讨论如何使用一个多点信号来分配PCIe时钟,而且仍满足PCIe第二代规范严格的抖动要求。

2019-08-30 06:54:47

Xilinx生成的PCIE核(如xapp1052),如果要使用的话,是必须要自己用C语言编写控制程序么?对于EDK的PCIE工程(xapp1030),应该在SDK中编写C驱动就行了吧,还是说也需要另外编写应用程序? 以上是一些关于PCIE我拿不准的地方,希望大家能够抽时间看看,给我一些提点,谢谢!!!

2015-06-25 19:21:35

我想在K7系列中使用“PCIE DMA”,但我找不到这个例子。

2020-07-29 10:56:04

参考。1.“使用出厂镜像启动时发现无法正常启动”问题描述——客户自制底板去掉PCIe烧录出厂镜像,启动时出现的卡死信息:产生原因——PCIe影响了启动,需要在设备树里把跟PCIe有关的功能关闭

2022-08-20 13:48:33

求一个Xilinx PCIe DMA Master代码工程

2021-06-23 17:26:35

如题:想买个xilinx7系列开发板,有没有人推荐个,最好不超过2000块,有没有

2018-01-13 21:56:36

最近在调pcie 2.0,用的是Xilinx k7 325t的片子,之前用4x、2.5g的时候工作正常,现在将速度提升至5.0g,但是一直识别不到设备。用chipscope抓信号,现象如下:1

2015-01-29 14:24:22

请教大家谁用过 Xilinx PCIe IP 核啊?

2014-01-15 14:38:28

亲关于如何使用GTX生成PIPE接口PCIE PHY的以下主题,有没有人有答案?https://forums.xilinx.com/t5/7

2020-05-04 09:05:44

for generating this kind of traffic. I'm on Windows 7 so the MET driver pointed out in the Xilinx PCIe tutorial

2019-04-17 09:10:31

嗨,我想在Kintex 7(KC705)评估板中获得尽可能多的端口12GHZ。PCIe端口是Kintex 7(KC705)评估板中唯一提供8个GTK端口的端口。PCIe Gen3仅支持8GHZ,但我

2019-09-29 08:21:01

本帖最后由 一只耳朵怪 于 2018-6-25 11:01 编辑

你好!我目前正在实现6657DSP 评估板与xilinx kintex7 FPGA之间的PCIE连接,其中DSP作为Root

2018-06-25 05:14:40

M31 PCIe 2.1 PHY IP M31 PCIe 2.1收发器IP提供了一系列完整的PCIe 2.1基本应用程序。它符合PIPE 3.0规范。该IP集成了高速混合信号电路,以支持

2023-04-03 19:47:28

M31 PCIe 3.1 PHY IP M31 PCIe 3.1 PHY IP为高带宽应用提供高性能、多通道功能和低功耗架构。PCIe 3.1 IP支持一系列完整的PCIe 3.1基本应

2023-04-03 19:50:56

所有的PCIe SSD在很大程度上看起来都是一样的,那么用户如何才能选择出满足他们需求的合适的PCIe SSD呢?

2011-12-22 14:17:12 5966

5966 Xilinx FPGA工程例子源码:PCIE DMA例子

2016-06-07 14:13:43 48

48 本文档内容介绍了基于Xilinx PCIe例程附带Linux驱动的修改,供参考。

2017-09-15 16:38:32 22

22 在EDK环境中针对在xilinx sp605 PCIe开发板,举一个简单的例子,介绍如何使用PCIE核与PC进行数据通讯。

2018-06-07 02:46:00 5273

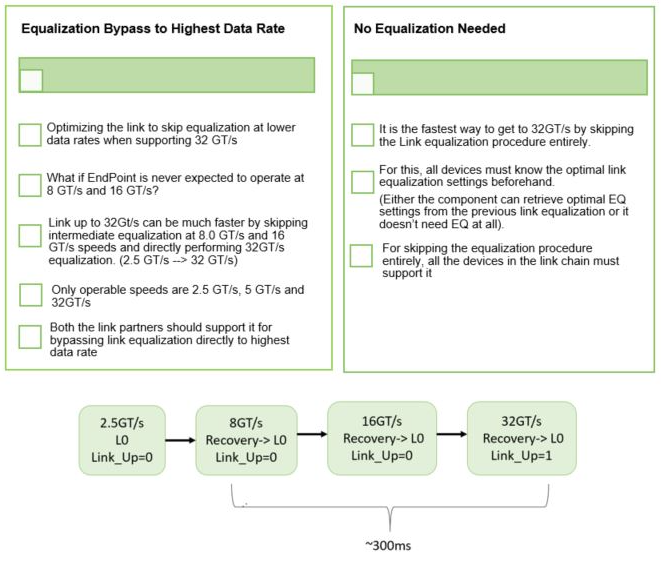

5273 根据PCIe的协议,当设备启动后,PCIe设备必须满足启动时间的要求,即上电后100ms内,完成PCIe设备的初始化。如果不能满足PCIe设备启动时间的要求,则lspci可能无法检测到基于FPGA

2018-06-19 10:24:00 7625

7625

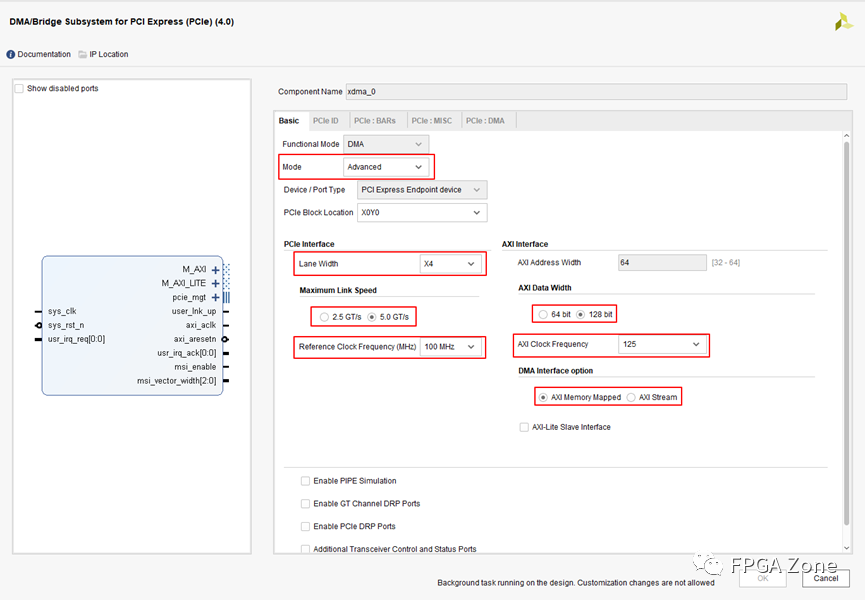

本视频介绍了设置和测试Xilinx PCIe DMA子系统性能的过程。

2018-11-27 06:16:00 6069

6069 ,M-PCIe ECN主要的改动在物理层,通过引入M-PHY,旨在获得更低的功耗以适应嵌入式设备的低功耗要求。 M-PCIe的主要特性如下: M-PCIe的上层协议层、事务层(TL)、数据链

2020-11-24 14:51:48 6997

6997 FPGA的bitstream比较大导致板卡从上电到FPGA配置完成的时间远远超过100MS的要求,从而电脑端无法正常识别到PCIE设备。 为此Xilinx的PCIE Tandem(详见PG156)功能

2021-06-18 14:57:17 3064

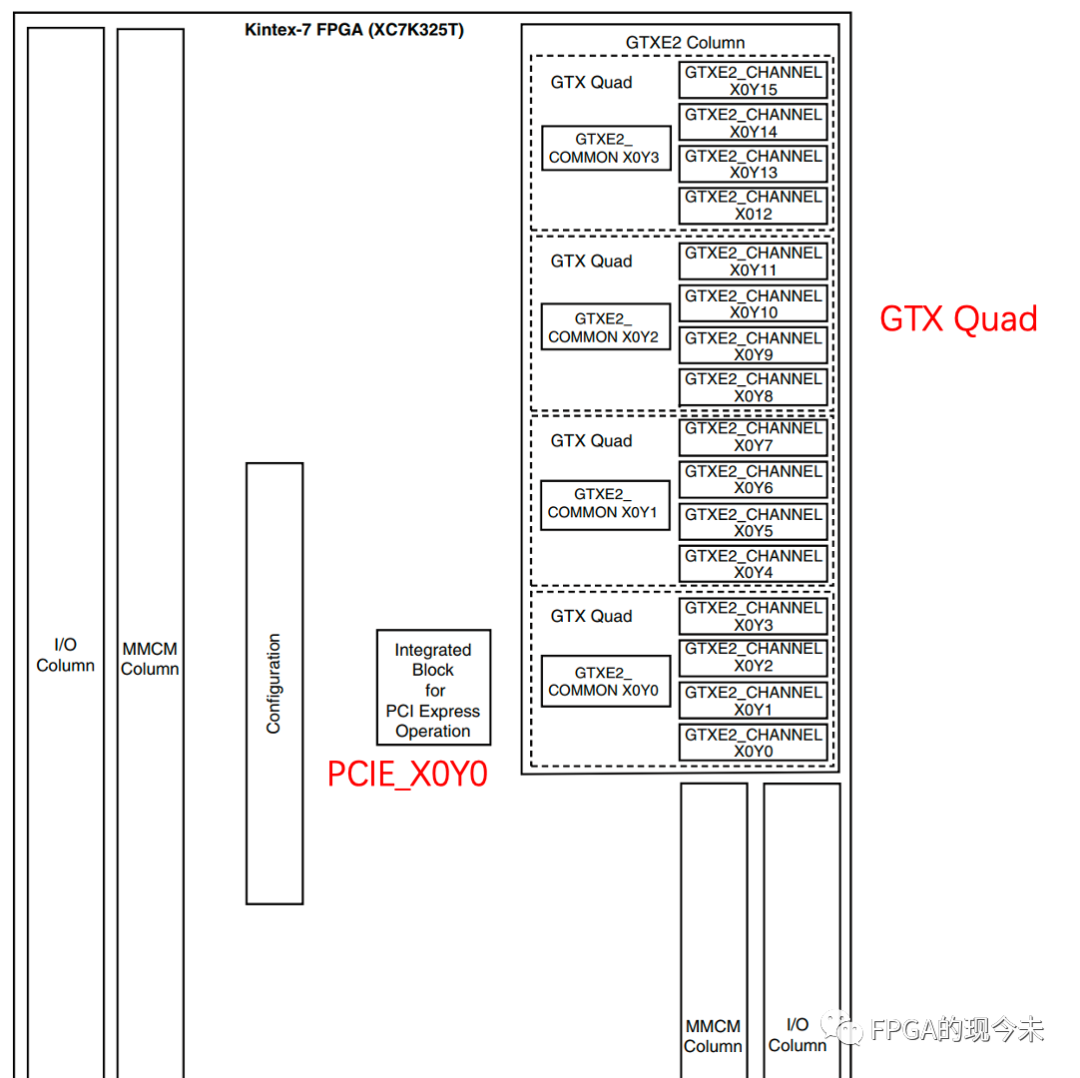

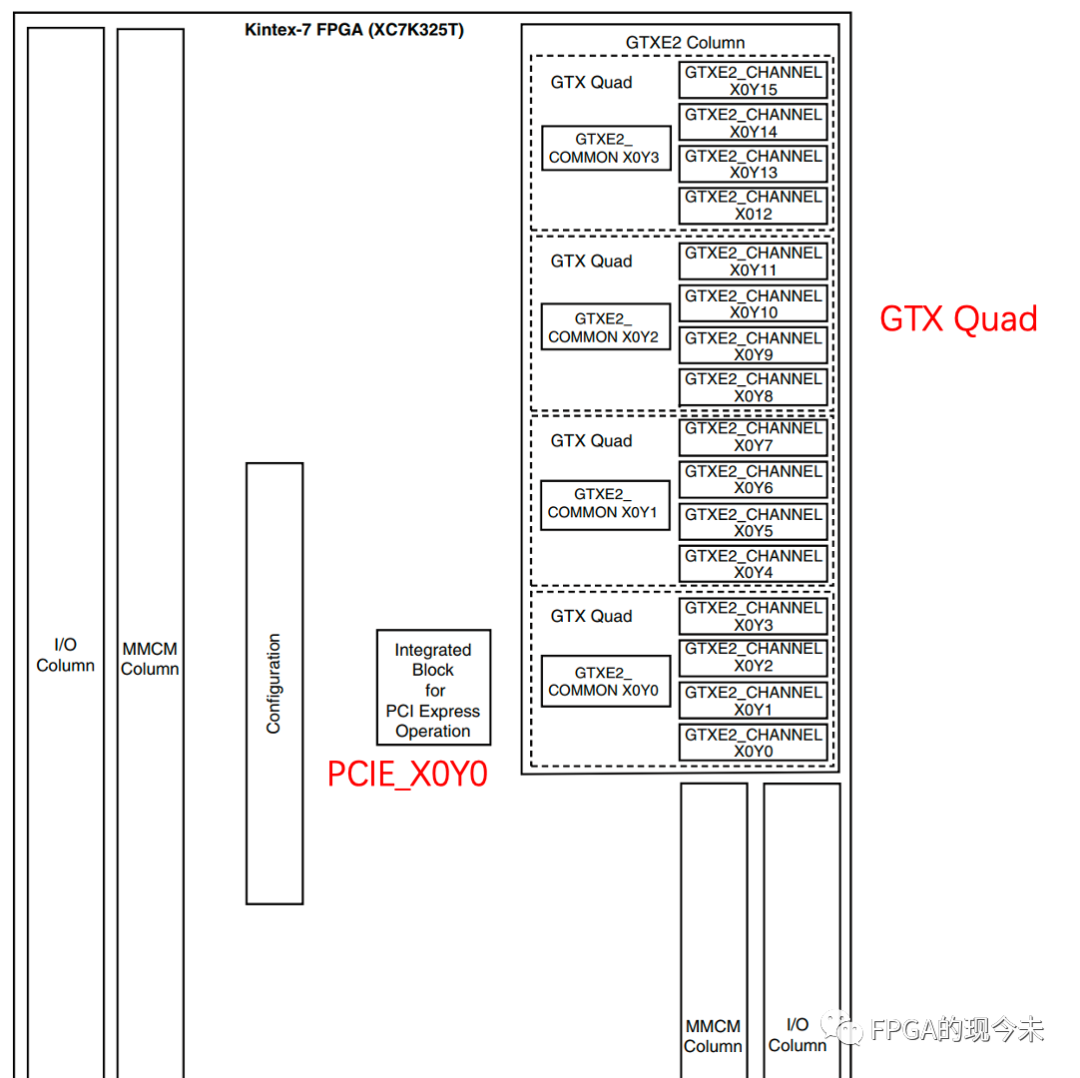

3064 : 总结上文:在硬件设计引脚分配的时候我们需要知道: 1、一个GT Quad由四个GT车道组成。为PCIe IP选择GT Quads时,Xilinx建议您在最靠近PCIe硬

2021-06-27 11:20:53 5951

5951

”,简写PCIe。2、AC耦合电容:高速差分信号电气规范要求PCIe发送端串联一个电容,进行耦合。3、链路类型与差分信号数量:X1:1对时钟差分信号,1对收发差分信号,单面pin数18pi...

2021-11-06 17:51:01 57

57 一个GT Quad由四个GT车道组成。为PCIe IP选择GT Quads时,Xilinx建议您在最靠近PCIe硬块的地方使用GT Quad。虽然这不是必要时,它将改善设计的位置,路线和时间。

2023-03-30 09:41:32 3469

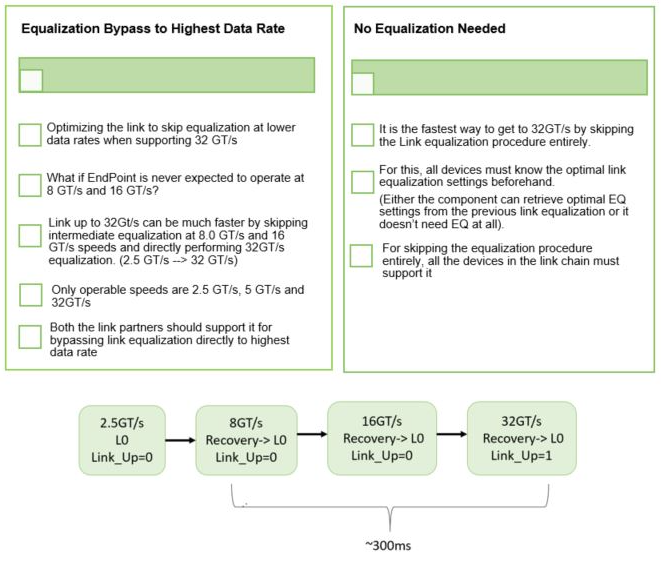

3469 PCIe 是用于点对点通信的高速差分串行标准。每一代 PCIe 标准都提供比上一代产品更多的功能和更快的数据传输速率。最新一代 PCIe 5.0 将使 PCIe 4.0 的吞吐率翻倍。PCIe

2023-05-26 10:23:14 1133

1133

PCIe接口相对来讲还是打交道比较多的接口。无论是Intel还是Xilinx的IP也都接触到过。

2023-06-05 10:47:27 3514

3514

支持 PCIe Gen5 x 4 与 CXL(EP)的连接,以及 PCIe Gen5 x 8 与 CCIX(RC/EP)的连接。这使得它能够以高速率 PCIe 进行数据传输,满足 PCIe 相关的验证或是对带宽要求高的应用。

2023-07-04 10:56:47 295

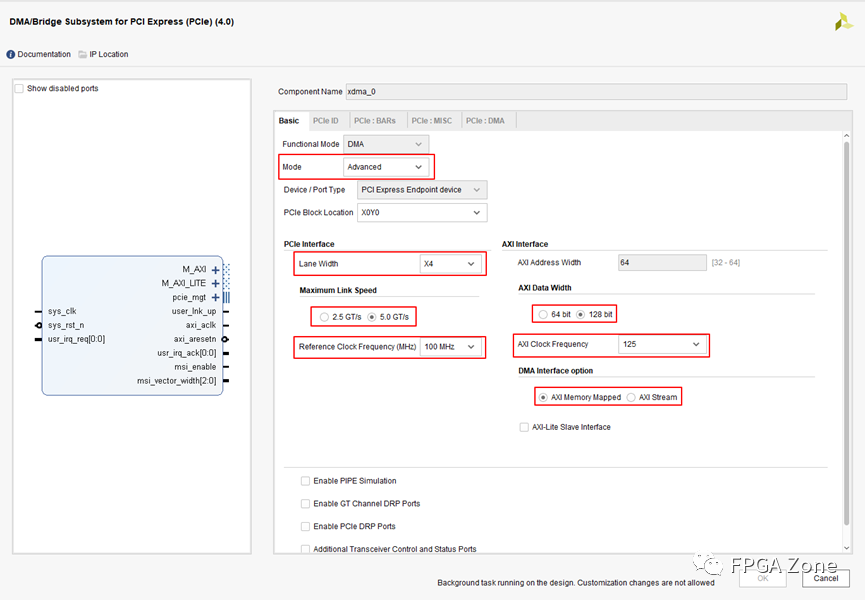

295 本文介绍一个FPGA开源项目:PCIE通信。该工程围绕Vivado软件中提供的PCIE通信IP核XDMA IP建立。Xilinx提供了XDMA的开源驱动程序,可在Windows系统或者Linux系统下使用,因此采用XDMA IP进行PCIE通信是比较简单直接的。

2023-09-04 16:45:54 1142

1142

随着英特尔Alder Lake CPU的发布,以及AMD 7000 Ryzen CPU的即将发布,PCIe 5.0 硬件终于成为现实。但什么是 PCIe 5.0?

2023-11-18 16:48:14 1302

1302

电子发烧友网站提供《i.MX 9系列-启动时间测量方法应用指南.pdf》资料免费下载

2024-02-20 10:37:04 0

0

电子发烧友App

电子发烧友App

评论