随着FPGA的不断发展,FPGA本身自带的PCIE硬核的数量越来越多,本文以ZU11EG为例介绍,如何进行对应的硬件引脚分配。

设计目标:ZU11EG FFVC1760封装,挂载4组NVME,接口为PCIE X4 ,

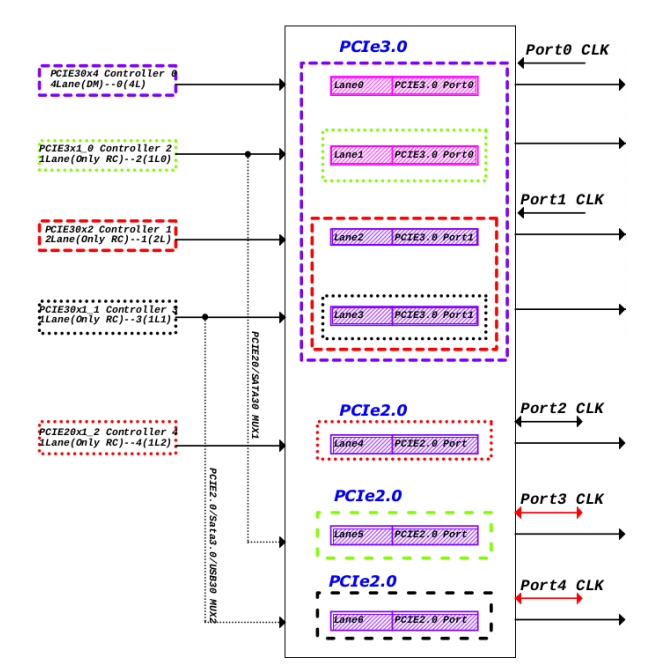

先我们先对ZU11EG的资源进行分析,在UG1075中我们可以清楚的看到其包含4个PCIE块,分别位于X0Y2,X0Y3,XIY1,XIY0.

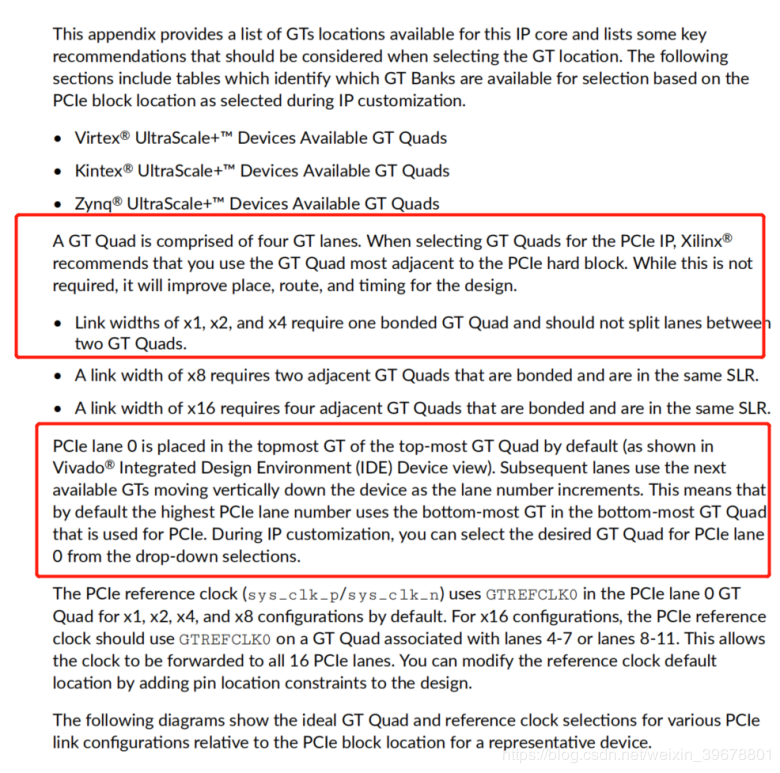

在文档PG213上我们可以看到如下:

总结上文:在硬件设计引脚分配的时候我们需要知道:

1、一个GT Quad由四个GT车道组成。为PCIe IP选择GT Quads时,Xilinx建议您在最靠近PCIe硬块的地方使用GT Quad。虽然这不是必要时,它将改善设计的位置,路线和时间。

2、需要注意PCIE lane 0的位置

3.根据些表格,这些表格根据以下内容确定哪些GT库可供选择:IP自定义期间选择的PCIe块位置。

那如何验证自己的分配结果呢?最终在实际使用的时候我们会应用到相关的IP核,最简单也是最靠谱的方法,是采用vivado新建工程,生成PCIE的IP核进行验证,如下图所示,可以清楚的知道对应的那些可用。

在FPGA硬件设计中,引脚分配是最重要的一步,也是最关键的一步。

编辑:jq

-

FPGA

+关注

关注

1655文章

22287浏览量

630308 -

PCIe

+关注

关注

16文章

1421浏览量

87551 -

GT

+关注

关注

0文章

15浏览量

24962

原文标题:基于XILINX FPGA的硬件设计总结之PCIE硬件设计避坑

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

一文搞懂 RK3588 PCIe:从硬件资源到拆分配置 + 避坑指南(含脑图)

MES系统避坑指南

【开源FPGA硬件】硬件黑客集结:开源FPGA开发板测评活动全网火热招募中......

PCBA打样全流程避坑指南:为电子产品研发保驾护航

选择身份核验终端硬件设备,你需要避开那些坑?

XILINX FPGA的硬件设计总结之PCIE硬件设计避坑指南

XILINX FPGA的硬件设计总结之PCIE硬件设计避坑指南

评论