最近弄PCIE,遇到一个问题,以前我们总认为:Xilinx的PCIE core的管脚是固定的,即指定了PCIE core的位置,对应的管脚也就指定了,真实情况是怎么样的呢?

背景说明

硬件在分配PCIE的管脚的时候,没有分配到xilinx推荐的对应的管脚上,如何处理呢?是否只能改板?

背景介绍

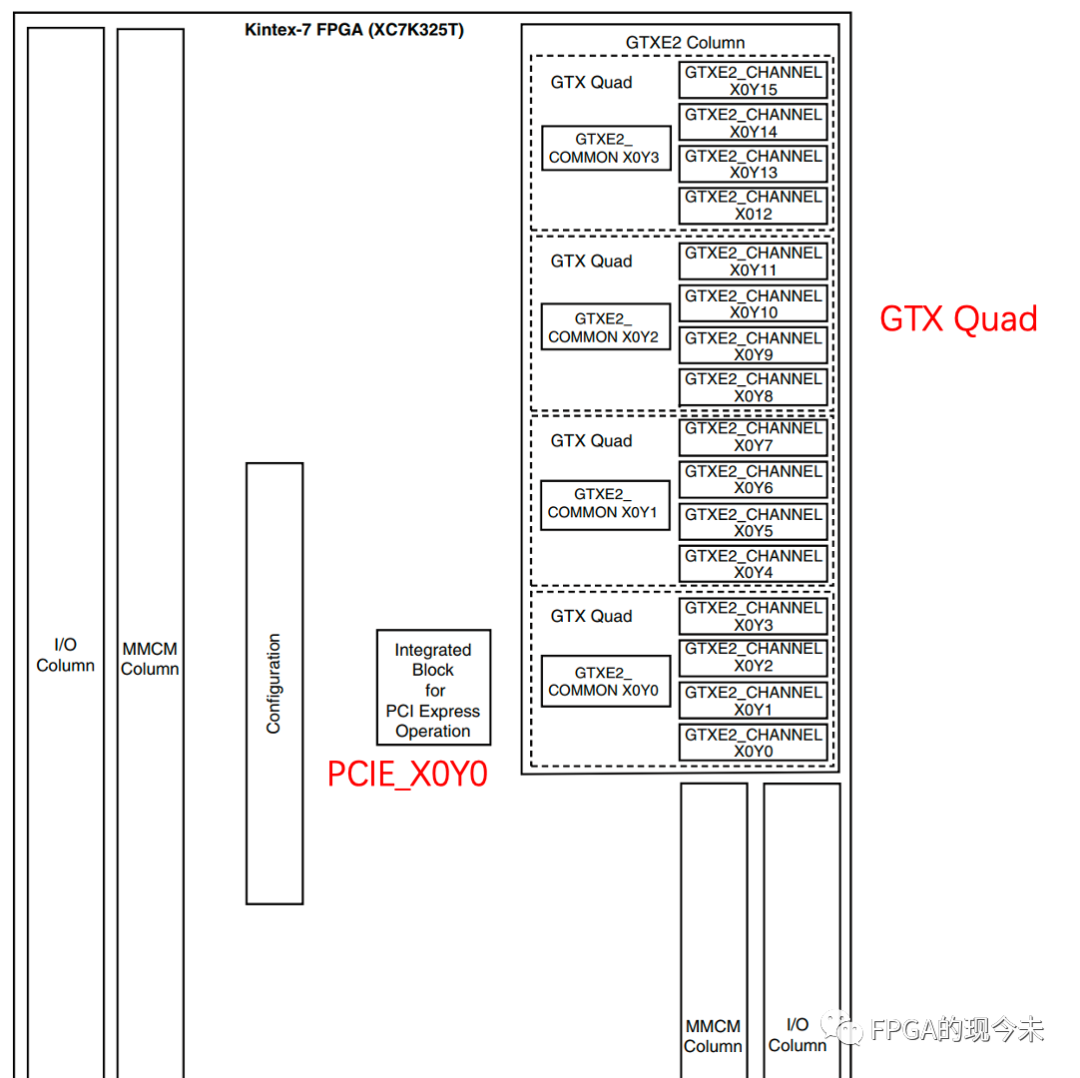

使用7系列的xilinx FPGA,需要用到PCIE core,计划是使用xilinx提供的硬core,该系列的FPGA中只有一个硬core,所以没得选择,我们使用的是PCIE_X0Y0这个硬core,如下图所示:

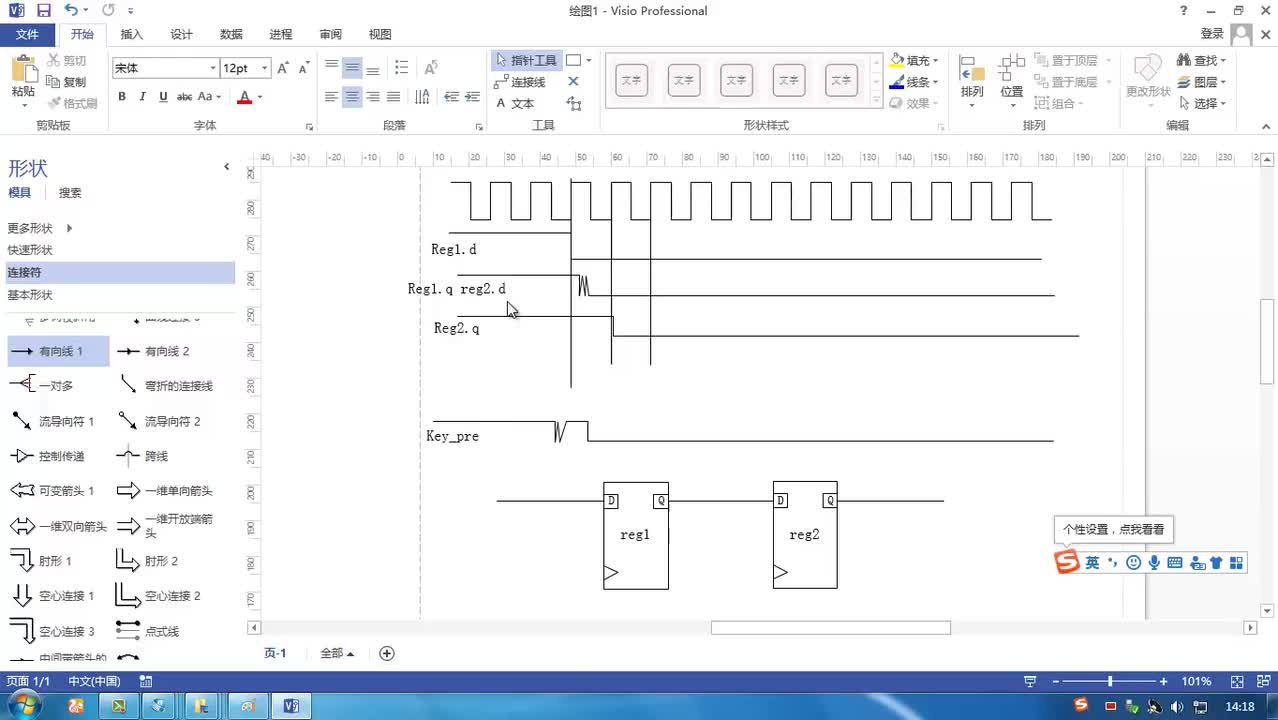

当PCIE的位置确定以后,PCIE对应的serdes位置也就“固定”了,有三种方式可以来查看这个“固定”位置。

第一、在PG054:7 Series FPGAs Integrated Block for PCI Express v3.2 LogiCORE IP Product Guide中,如下图所示:我们可以看到,对于的K7系列的325T的器件,X4的recommended GT locationg是X0Y4/X0Y5/X0Y6/X0Y7

另外我们在文档ug476:7 Series FPGAs GTX/GTH Transceivers中可以看到X0Y4/X0Y5/X0Y6/X0Y7对应的管脚如下图所示:

第二种方式,直接综合PCIE core,综合后,查看综合结果,如下图所示,我们可以看到,在不对PCIE core做任何约束的情况下,该PCIE默认的管脚也是在channel X0Y4-——X0Y7所在Quad上。其pin的约束和上图一致。

还有第三种方式,通过xilinx提供的example design来确定对应的管脚约束,通过查看example design的约束,我们发现关于位置的约束就只有如下一行,它约束的差分时钟双端转单端的refclk_ibuf,位置为IBUFDS_GTE2_X0Y3,这个刚好也位于MGT_BANG_116。

set_property LOC IBUFDS_GTE2_X0Y3 [get_cells refclk_ibuf]

结论:K7系列FPGA对于X4的PCIE,其默认的约束就是在MGT_BANG_116,

问题

硬件在管脚分配的时候,没有按照Xilinx默认的管脚分配原则分配在MGT_BANG_116,而是分配到了MGT_BANG_118上(第一张图中,右边的4个gtx quad从上到下分别是118/117/116和115)。

解决方案

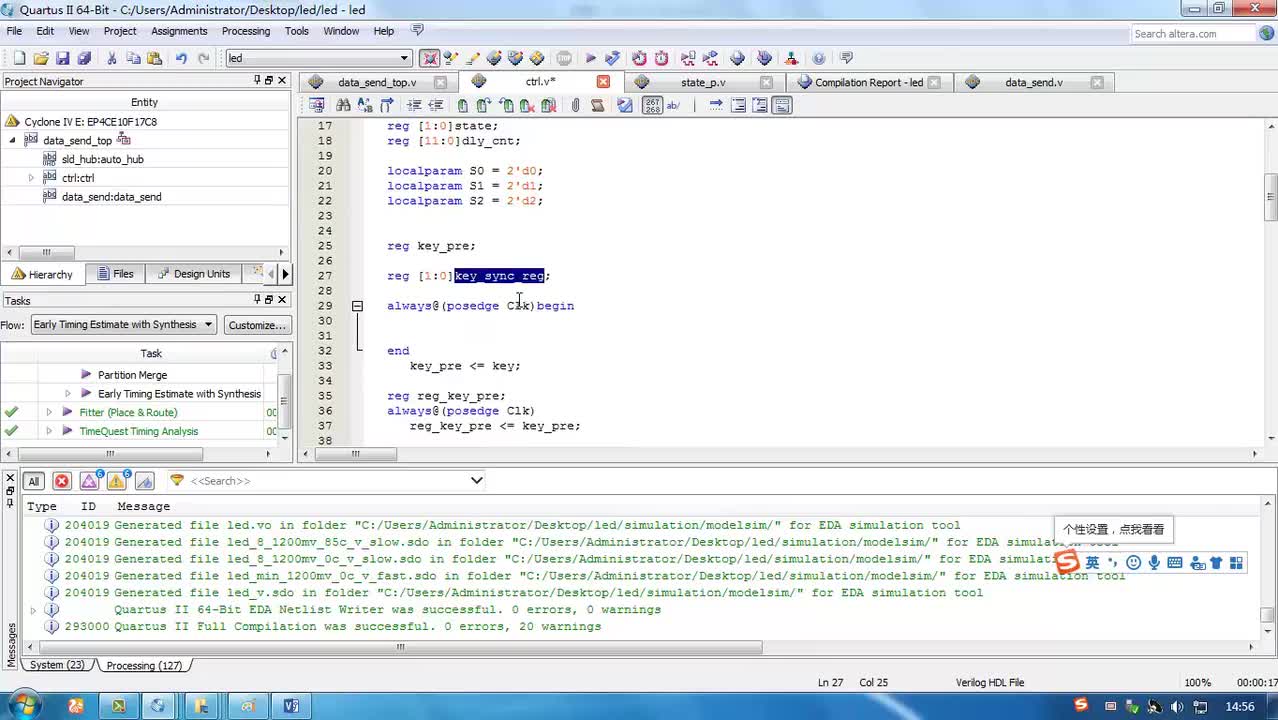

pcie core和所用的gt是分开的,我们可以通过约束channel的位置来改变所使用的channel,从而改变pcie的管脚。约束如下所示,只需要绑定channel和pcie对应的lane即可,通过约束发现imp阶段工程是可以通过的。

set_property LOC GTXE2_CHANNEL_X0Y12 [get_cells {***/pcie_core/pcie_7x_1_i/inst/gt_top_i/pipe_wrapper_i/pipe_lane[0].gt_wrapper_i/gtx_channel.gtxe2_channel_i}]

测试结果

通过实际上板测试,pcie core能正常link up,进行业务测试收发数据也正常,不过这里也有一个风险,通过device视图我们可以看到,MGT_BANG_118所在的quad是离pcie core最远的quad,尤其是两者之间资源比较多的时候,布线会比较多,这必然导致时序风险。

结论

1、pcie的管脚有xilinx推荐的最佳约束位置,分配管脚的时候应该严格按照推荐的规则来分配;

2、如果硬件把管脚弄错了,可以通过约束来修改pcie core的默认管脚,但是资源紧张的时候可能有时序风险。

-

FPGA

+关注

关注

1664文章

22502浏览量

639101 -

Xilinx

+关注

关注

73文章

2206浏览量

131865 -

PCIe

+关注

关注

16文章

1477浏览量

88911 -

管脚

+关注

关注

1文章

230浏览量

33884

发布评论请先 登录

xilinx ddr2硬核管脚问题

用于 Xilinx FPGA Zynq 7 的电源解决方案

xilinx,ddrmig文件中管脚分配

化PCIe应用中的时钟分配方法

怎么使用一个多点信号分配PCIe时钟?

Xilinx FPGA是否有任何选项或可能的解决方案?

PCIE高速传输解决方案FPGA技术XILINX官方XDMA驱动

基于Core的动态内存分配方案

Xilinx PCIE core管脚分配错误的解决方案

Xilinx PCIE core管脚分配错误的解决方案

评论