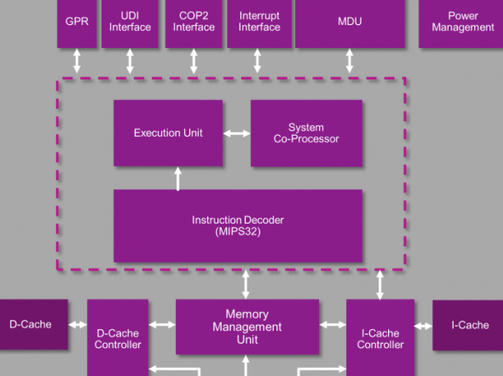

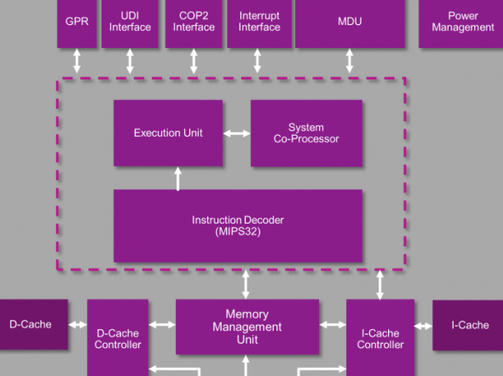

课程的地方在于首次采用了一款纯粹的商用软核CPU用于研究目的,用户可以在此课程的系统集成环境下详细、深入的探索计算机架构。 MIPSfpga使用一款MIPS系列软核IP具体来讲是microAptiv核,PIC32MK处理器采用的既是此款软核。该核面向的是可编程逻

2018-05-21 10:17:01 8273

8273

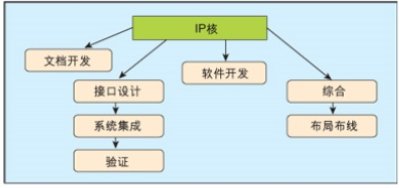

现今的FPGA设计规模越来越庞大,功能越来越复杂,因此FPGA设计的每个部分都从头开始着手是不切实际的。

2023-06-12 17:25:14 5762

5762

软核与fpga如何共用一块flash?

目前fpga开发板上只有一个flash,用nuclei 向软核中下载程序掉电就不跑了,请问怎么解决?

2023-08-12 06:05:26

系统级设计,设计人员现在使用SOPC Builder工具时,可以选择Freescale?、ARM?或者Altera软核处理器以及50多种其他的知识产权(IP)模块。 &

2008-06-17 11:40:12

TXVring区发送数据,从RXVring区读取接收数据,A核反之。处理器支持消息传递单元(MessagingUnit,简称MU)功能模块,通过MU传递消息进行通信和协调,芯片内的M7控制核和A53

2022-11-23 15:09:45

)放置flash 偏移地址0x50000处,关闭看门狗,重新配置后,发现fpga只更新了硬核,软核没有运行。通过测试,发现更新完硬核后,软核还是找到的第一个程序软核入口。没有找到要更新程序软核入口地址。不知道如何设置,使重新配置后,能够找到更新程序软核地址?希望大神帮助。。感激

2017-07-30 10:21:09

:

但是我们实际上板后发现,通过终端显示的实际运行频率是16MHZ.如下图

经过询问请教芯来科技的官方人员,我们得知,由于FPGA布局布线,以及FPGA通过LUT实现逻辑电路,导致在FPGA用软核

2025-10-29 06:19:19

FPGA硬核与软核处理器有什么区别和联系?

2023-05-30 20:36:48

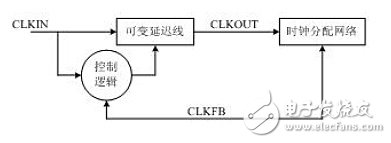

Loop)、PLL(Phase Locked Loop)、DSP和CPU等软处理核(Soft Core)。现在越来越丰富的内嵌功能单元,使得单片FPGA成为了系统级的设计工具,使其具备了软硬件联合设计的能力

2017-05-09 15:10:02

(Phase Locked Loop)、DSP和CPU等软处理核(Soft Core)。现在越来越丰富的内嵌功能单元,使得单片FPGA成为了系统级的设计工具,使其具备了软硬件联合设计的能力,逐步向

2023-05-30 20:53:24

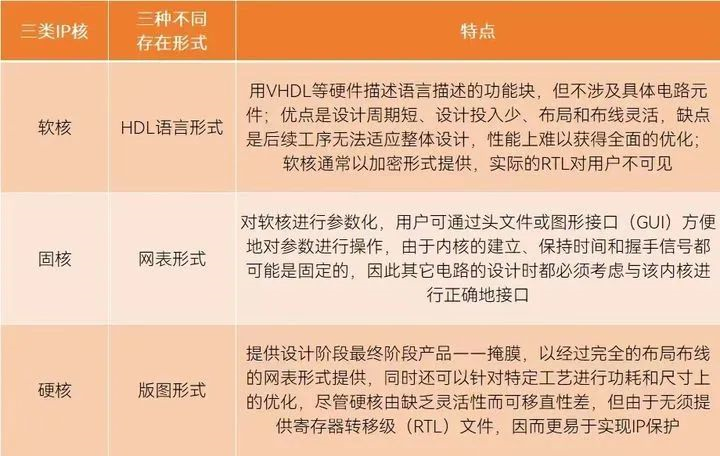

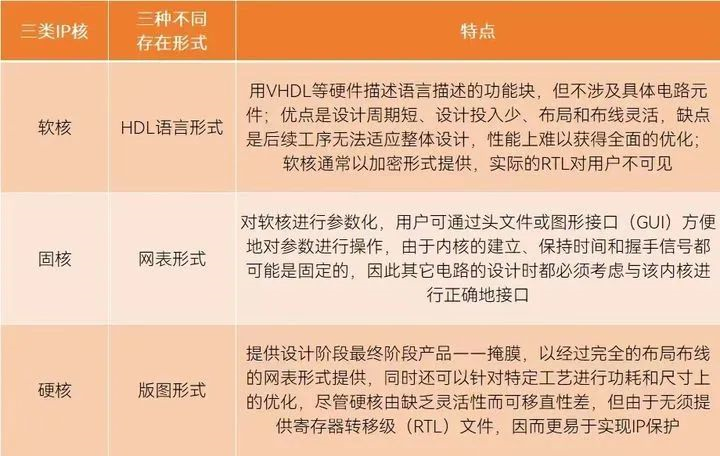

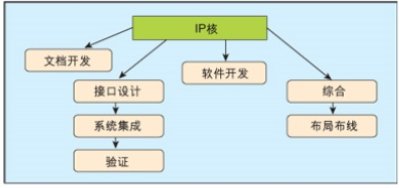

。 从IP核的提供方式上,通常将其分为软核、固核和硬核这3类。从完成IP核所花费的成本来讲,硬核代价最大; 从使用灵活性来讲,软核的可复用使用性最高。与软核实现方式相比,硬核可以把功耗降低5~10 倍

2018-09-03 11:03:27

FPGA的IP软核使用技巧主要包括以下几个方面:

理解IP软核的概念和特性 :

IP软核是指用硬件描述语言(如VHDL或Verilog)描述的功能块,但并不涉及具体的电路实现细节。它通常只经过功能

2024-05-27 16:13:24

FPGA由6部分组成,分别为可编程输入/输出单元、基本可编程逻辑单元、嵌入式块RAM、丰富的布线资源、底层嵌入功能单元和内嵌专用硬核等。

2019-09-26 06:11:33

如何根据成本、功耗和性能来选择微处理器?FPGA结构中硬核和软核的特点是什么?处理器IP有什么重要性?

2021-04-08 06:16:37

IP核是指在电子设计中预先设计的用于搭建系统芯片的可重用构件,可以分为软核、固核和硬核三种形式。软核通常以可综合的RTL代码的形式给出,不依赖于特定的工艺,具有最好的灵活性。硬IP核是针对某种特定

2021-07-22 08:24:29

[url=]ISE中应用MicroBlaze软核[/url]

2015-12-14 13:22:42

关于QuartusⅡ10.1中NIOS2软核的构建、软件编译及程序固化 一、硬件开发1、构建CPU模块2、构建EPCS控制器,SYSTEM ID模块,JTAG UART模块3、构建RAM模块(1

2022-01-25 07:58:08

求教e203 软核如何和FPGA通信

2025-11-07 06:15:50

模拟电路描述,代码与工艺无关,重用性高,有大量IP核可供使用。1.2软核、固核与硬核:软核:经验证的实现特定功能的电路结构的Verilog HDL模型;固核:在现场可编程门阵列FPGA上实现的、经验

2022-03-22 10:26:00

知识产权核,其分为软核、硬核和固核。软核通常是与工艺无关、具有寄存器传输级硬件描述语言描述的设计代码,可以进行后续设计;硬核是前者通过逻辑综合、布局、布线之后的一系列工艺文件,具有特定的工艺形式、物理实现

2016-12-22 23:37:00

知识产权核,其分为软核、硬核和固核。软核通常是与工艺无关、具有寄存器传输级硬件描述语言描述的设计代码,可以进行后续设计;硬核是前者通过逻辑综合、布局、布线之后的一系列工艺文件,具有特定的工艺形式、物理实现

2019-03-04 06:35:13

保护您的 IP 核——第一部分软 IP——前言 随着全球化硬件设计和制造过程的激增以及IP供应商之间的竞争,IP盗版/假冒、虚假所有权等威胁正在加剧。因此,保护 IP 核设计的要求及其代表的专有

2022-02-23 11:59:45

想问问virl_sdn_fsdprb_1在arm核里有什么作用呢?看名字可以猜一下功能吗

2016-09-06 14:36:33

FPGA的硬核和软核有什么区别呢,有没有使用硬核的开发板,想学习关于FPGA硬核的知识,各位大神有什么建议呢?真心求教

2013-03-05 11:51:54

单元(LUT4/LUT5混合架构),130KB SRAM,32bit 位宽64MBit SDRAM,用来跑 RISC-V 的软核相当合适了。 为了给这块 FPGA 烧录 bitstream 把它变成软

2022-09-16 16:15:39

在quartus上想修改软核PLL中设置,为什么打不开啊?想改一改PLL的分频,打不开pll核。如图

2017-02-02 16:10:34

在tc275上怎么用一个核触发另一个核产生软中断?

2024-02-19 08:14:22

UART内部可划分为哪几个模块?这些模块有什么功能?基于APB总线的UART接口软核该如何去设计?

2021-06-18 08:20:15

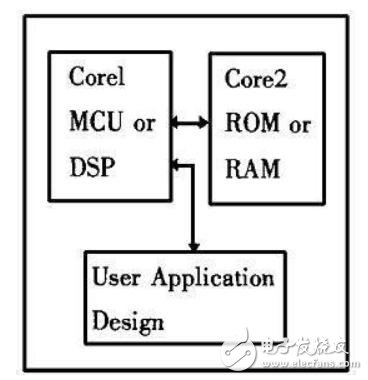

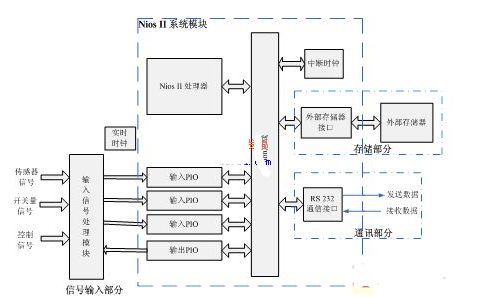

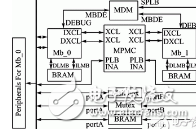

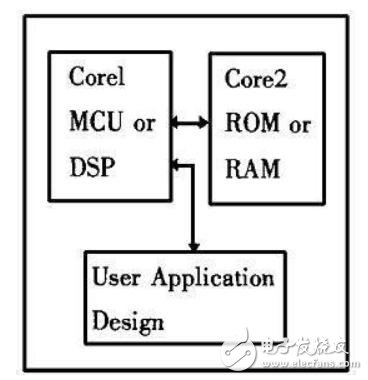

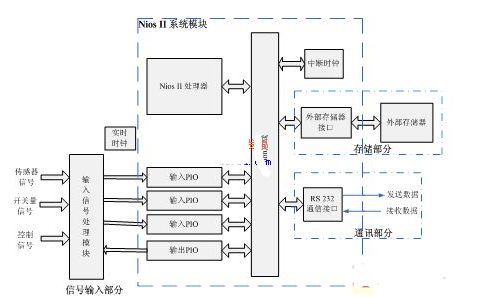

基于NIOS II 软核处理器的SOPC 技术摘要:介绍了基于NIOS II 软核处理器的SOPC 技术,分析了传统方法和基于SOPC 技术的方法实现扩频收发机的优劣,详细说明了嵌有双NIOS II

2009-10-06 15:05:24

如何为tinyriscv软核串口下载编写一个图形界面软件?

2022-02-16 07:54:07

IP核可以两种形式提供给客户:软核和硬核。两种方式都可使客户获得在功能上经过验证的设计。软核也被称为可综合内核,需要由客户进行综合并在其SoC上实现。而硬核已完全实现(完成了版图设计),可直接用于

2021-07-03 08:30:00

导航系统SoC芯片设计的要求有什么?如何构建基于LEON开源软核的SoC平台?

2021-05-27 06:18:16

本文利用先进的EDA软件,用VHDL硬件描述语言采用自顶向下的模块化设计方法,完成了具有相序自适应功能的双脉冲数字移相触发器的IP软核设计。

2021-04-28 06:39:00

NiosⅡ处理器是Intel公司为Altera公司推出的一个32位精简指令处理器软核。在Altera公司推出的软件SoPC中加载NiosⅡ软核和相应的外围接口以及与定义相应的自定义指令,然后

2019-08-06 06:37:27

有没有带DSP软核的FPGA,要求DSP运行速度在50kHz以上。

2014-09-29 18:13:51

介绍如何在Altera开发平台上,使用Nios软核CPU来构建嵌入式Internet系统;并结合以太网远程数据采集系统的实例,介绍此类系统硬件,软件的设计方法。

2021-06-04 07:05:47

什么是三相全控桥整流电路?怎样去设计IP软核?怎样对IP软核进行仿真及验证?

2021-04-23 07:12:38

本帖最后由 eehome 于 2013-1-5 09:55 编辑

哪位大侠有FPGA入门级的资料,跪求之!!!关于FPGA可以实现哪些功能,进行哪些方面的功能扩展,比如内嵌硬核、软核

2012-07-22 08:45:34

本文介绍的是基于RISC体系结构的8位高速MCUIP软核的设计与实现,采用Verilog HDL自上而下地描述了MCUIP软核的硬件结构,并验证了设计的可行性和正确性。在实际硬件电路中,该IP核的运行频率达到75MHz,可应用于高速控制领域。

2021-04-19 07:28:21

请问谁手里还有原来ip-extreme免费版本的coldfire for altera软核,能否分享给我一份?

2021-06-21 06:25:01

所搭的IP软核的通讯协议与总线支持的通讯协议(ICB)不同怎么转换?

2023-08-17 07:05:35

,便于广大工程师的学习和交流。1. FOC控制硬核和通用软核的区别和优缺点2. FOC控制算法基本介绍3. 低压吊扇最新方案介绍大家也可以参考下面链接观看培训视频:http://t.elecfans.com/live/1277.html

2020-08-28 10:41:36

我已经搭建好了软核microblaze,但是用sdk编程却看不懂,请教大侠如何学习在sdk内编程?

2014-03-04 17:15:00

核的分类和特点有哪些?在FPGA设计中的核分为哪几种?核基FPGA是如何设计的?软核的设计及使用是什么?

2021-04-14 06:25:39

片上Nios Ⅱ嵌入式软核多处理器系统具有哪些优势?如何实现片上嵌入式Nios Ⅱ软核六处理器系统的设计?

2021-04-19 08:17:09

基于FPGA 的嵌入式ASIP 软核设计与实现作者:李庆诚 任健 刘嘉欣 黄宝贞 来源:微计算机信息摘要:采用ASIP+FPGA 模式设计了一款嵌入式微处理器软核,以该软核为例从体系结构和

2010-02-06 10:44:40 30

30 介绍了系统芯片SOC的概念和M8051 IP软核的原理,给出了视频字符叠加器VAD_SOC中M8051 IP软核的作用,详细介绍了I2C主控制器模块的设计,给出了功能仿真波形,最后对M8051IP软核在视频

2010-07-05 14:31:33 47

47 采用ASIP+FPGA模式设计了一款嵌入式微处理器软核,以该软核为例从体系结构和指令集设计两方面对ASIP+FPGA模式微处理器软核的设计进行了分析和验证,最后通过与传统微处理器对比

2010-07-28 17:41:46 17

17 内嵌ARM核的FPGA芯片EPXA10及其在图像驱动和处理方面的应用

2006-04-16 23:33:07 1544

1544 本文阐述了一种基于NiosII 软核处理器技术的数字式超声探伤系统设计方案,与传统数字式超声探伤系统进行了比较,讨论了数字式超声探伤系统的工作原理及NiosII 软核处理器设计过程

2011-09-21 16:40:50 32

32 本书介绍Xilinx公司的嵌入式集成开发平台EDK工具组的使用方法,FPGA内嵌CPU核软核Microblaze和硬核PowerFC405,以及使用这些CPU核与Xilinx提供的多种外设IP核进行嵌入式设计的流程与方法。引

2011-11-23 10:47:01 102

102 NiosII软核处理器是Altera公司开发,基于FPGA操作平台使用的一款高速处理器,为了适应高速运动图像采集,提出了一种基于NiosII软核处理的步进电机接口设计,使用verilog HDL语言完成该接

2012-06-12 09:09:07 43

43 基于软核Nios_Ⅱ的SOPC数据采集系统的设计

2016-02-17 10:07:11 41

41 FPGA和Nios_软核的语音识别系统的研究。

2016-05-10 10:46:40 20

20 软核演练篇,VHDL资料,又需要的下来看看

2016-08-08 15:17:40 20

20 中的printf()函数),可以直接调用,非常方便,大大加快了开发速度。 IP内核的三种类型 IP核有三种不同的存在形式:HDL语言形式,网表形式、版图形式。分别对应我们常说的三类IP内核:软核、固核和硬核。

2017-11-15 11:19:14 10744

10744 设计了一款基于双MicroBlaze软核处理器、面向嵌入式领域的SOPC系统,在信息处理繁忙的情况下,实现两软核处理器之间的同步、通信和中断功能,提高信息吞吐率和系统灵活性,降低设备尺寸。两处理器

2017-11-18 03:50:27 4439

4439

中的printf()函数),可以直接调用,非常方便,大大加快了开发速度。 IP内核的三种类型 IP核有三种不同的存在形式:HDL语言形式,网表形式、版图形式。分别对应我们常说的三类IP内核:软核、固核和硬核。

2017-11-28 15:49:58 2339

2339 提出了基于嵌入式PLC软核的通用配网保护平台设计方案。针对传统保护软件编程灵活性差,现场可配置能力弱的问题,在分析嵌入式PLC软核的特性并讨论了基于PLC软核技术实现110 kV及以下配网综合保护

2018-01-17 16:03:49 0

0 集成电路设计过程中引入的非受控第三方IP软核较容易被植入硬件木马,以往的功能测试方法较难实现全覆盖检测。为此,分析硬件木马结构及其在IP软核中的实现特征,提出一种基于硬件木马特征匹配的检测方法。给出

2018-02-23 11:39:38 0

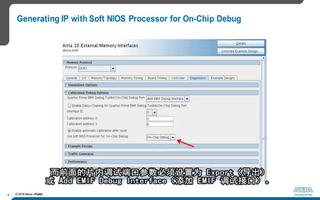

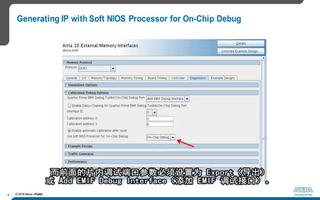

0 使用片内调试 Nios 软核处理器

2018-06-20 05:53:00 3888

3888

基于Nios软核的SoPC系统设计是整个系统硬件设计的核心,包括Nios软核处理器的设计、数据采集控制的设计、图像信号FFT分析的实现、参数显示以及RS232通信模块的设计等。另外,使用Nios进行嵌入式设计在硬件上必需使用Altera公司的FPGA。

2019-08-21 14:22:37 1698

1698

本文给出了汽车电子控制单元 ECU 的 IP 核设计。该 IP 核基于 RISC 技术的单指令、单周期的体系结构,并采用了自顶向下(top-down)的设计方法和硬件描述语言 Verilog HDL,给出了 ECU 的体系结构以及各个功能模块的具体设计和仿真结果。

2018-10-31 08:00:00 20

20 核芯显卡是建立在和处理器同一内核芯片上的图形处理单元。本视频主要详细阐述了核芯显卡的优势,分别有低功耗、高性能以及WiDi。

2018-11-24 10:12:57 5410

5410 软核在EDA设计领域指的是综合之前的寄存器传输级(RTL)模型;具体在FPGA设计中指的是对电路的硬件语言描述,包括逻辑描述、网表和帮助文档等。软核只经过功能仿真,需要经过综合以及布局布线才能使用。

2019-03-01 15:41:13 12406

12406 以Step by step的方式Guide You来定制你自己的NIOS-II软核SoC,并创建C语言的流水灯测试程序,运行在自己做的CPU系统上。

2019-04-22 16:35:45 2903

2903 软核、固核和硬核,设计的完成度是由低到高,对芯片设计公司的要求也是从高到低,而发挥的空间也是从高到低:软核发挥的空间最大,硬核发挥的空间最小

2019-04-03 10:04:06 47948

47948 用户逻辑和软核的综合应加合理的时序约束, 以满足设计的要求, 约束条件可由综合文件(Synthesis Script ) 给出。完成设计输入后进入设计实现阶段,在此阶段固核的网表和设计约束文件

2019-06-02 10:45:31 4182

4182

软核演练篇包含了哪些内容:该篇以什么是软核、什么是Qsys、如何构建一个Qsys系统为切入点,在该基础上进一步介绍了Nios II处理器的体系结构、Qsys丰富多彩的内置IP,以及Avalon总线

2019-11-11 17:46:21 3419

3419

IP核有三种不同的存在形式:HDL语言形式,网表形式、版图形式。分别对应我们常说的三类IP内核:软核、固核和硬核。这种分类主要依据产品交付的方式,而这三种IP内核实现方法也各具特色。

2019-12-19 07:07:00 2268

2268

IP核有三种不同的存在形式:HDL语言形式,网表形式、版图形式。分别对应我们常说的三类IP内核:软核、固核和硬核。这种分类主要依据产品交付的方式,而这三种IP内核实现方法也各具特色。

2019-10-08 07:09:00 1940

1940 软核演练篇包含了哪些内容:该篇以什么是软核、什么是Qsys、如何构建一个Qsys系统为切入点,在该基础上进一步介绍了Nios II处理器的体系结构、Qsys丰富多彩的内置IP,以及Avalon总线

2019-12-10 07:06:00 4271

4271

软核演练篇包含了哪些内容:该篇以什么是软核、什么是Qsys、如何构建一个Qsys系统为切入点,在该基础上进一步介绍了Nios II处理器的体系结构、Qsys丰富多彩的内置IP,以及Avalon总线

2019-12-10 07:03:00 2816

2816 软核演练篇包含了哪些内容:该篇以什么是软核、什么是Qsys、如何构建一个Qsys系统为切入点,在该基础上进一步介绍了Nios II处理器的体系结构、Qsys丰富多彩的内置IP,以及Avalon总线

2019-12-09 07:10:00 3628

3628

本文参照CAN2.0 总线协议设计了一个CAN 控制器软核。具体设计采用TOP-DOWN 方式,上层采用模块化设计,最底层模块以Verilog 语言编写而成。测试了软核在Xilinx 公司

2019-07-19 17:48:41 27

27 嵌入式处理器是嵌入式系统的核心,有硬核和软核之分。

2019-10-18 10:36:28 7066

7066

、固IP和硬IP。软IP是用Verilog/VHDL等硬件描述语言描述的功能块,但是并不涉及用什么具体电路元件实现这些功能。固IP是完成了综合的功能块。硬IP提供设计的最终阶段产品掩膜。定义源自百度百科 三.IP授权的出现源自半导体设计行业的分工,即设计公司无

2020-08-19 11:08:51 708

708 IP核可以两种形式提供给客户:软核和硬核。两种方式都可使客户获得在功能上经过验证的设计。软核也被称为可综合内核,需要由客户进行综合并在其SoC上实现。而硬核已完全实现(完成了版图设计),可直接用于

2021-01-07 07:32:00 3668

3668

概述ME32x系列是内嵌ARM Cortex M0/M3核的32位微控制器。

2021-03-31 15:14:33 3474

3474 断路器两侧电源是否同相而研发的无线高压核相器。无线语音高压核相器适合6KV~220KV输电线路带电核相作业,本高压核相器具有验电功能和语音功能。无线高压核相器标准支持:DL/T408-1991GB/T1029-2005 GB311.1-2012。 TAG8000无线高压核相器是根据国家

2021-03-31 16:12:00 3579

3579 SOPC技术,即软核处理器,最早是由Altera公司提出来的,它是基于FPGA的SOC片上系统设计技术。

2021-04-15 09:48:46 10800

10800 在FPGA上生成8086指令兼容的软核以及外设并在此基础上跑通pc机上吃豆子PACMAN游戏项目(深圳市优能电源技术有限公司)-在FPGA上生成8086指令兼容的软核以及外设,并在此基础上跑通pc机上吃豆子PACMAN游戏项目

2021-09-16 12:17:37 13

13 SOPC技术最早是由Altera公司提出来的,它是基于FPGA的SOC片上系统设计技术。是使用FPGA的逻辑和资源搭建的一个软核CPU系统,由于是使用F...

2022-01-26 19:03:52 2

2 在前文中,我们了解到两种 FPGA 嵌入式处理器核方案:软核与硬核。本文将展开讨论软核在一个基于 FPGA 通信系统中的应用。软核,由 FPGA...

2022-02-07 10:07:43 4

4 SOPC技术,即软核处理器,最早是由Altera公司提出来的,它是基于FPGA的SOC片上系统设计技术。是使用FPGA的逻辑和资源搭建的一个软核CPU系统,由于是使用FPGA的通用逻辑搭建的CPU

2022-12-06 10:00:39 2319

2319 电子发烧友网站提供《基于Nios软核的音频效果器.pdf》资料免费下载

2023-10-09 15:28:11 0

0 目前 AMD 的以太网 IP 核,如软核 10G/25G,40G/50G 或者硬核 CMAC,MRMAC,DCMAC 等等,都采用的是同一种 Pause 帧处理方式。

2023-10-18 09:15:37 2039

2039

电子发烧友App

电子发烧友App

评论