ETD第14期:SDR源同步接口时序约束方法

- FPGA(591969)

- 接口设计(29663)

- ETD(16852)

相关推荐

工程师谈FPGA时序约束七步法

时序例外约束包括FalsePath、MulticyclePath、MaxDelay、MinDelay。但这还不是最完整的时序约束。

2016-05-29 23:25:10 1064

1064

1064

1064FPGA案例解析:针对源同步的时序约束

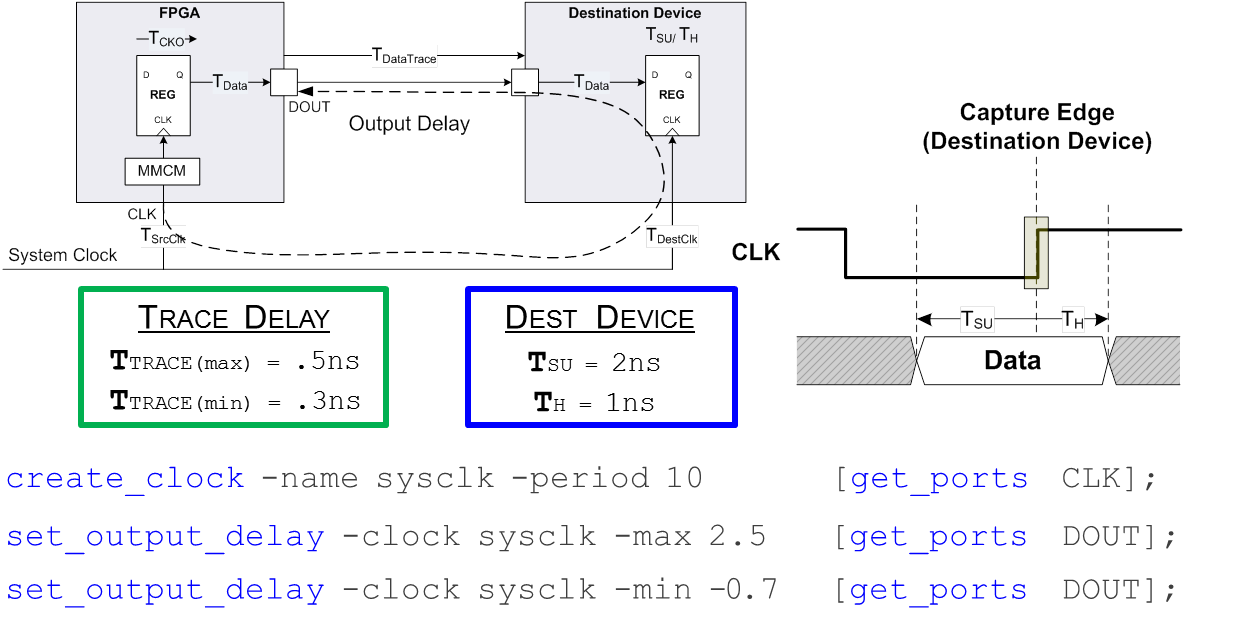

是指FPGA与外部器件共用外部时钟;源同步(SDR,DDR)即时钟与数据一起从上游器件发送过来的情况。在设计当中,我们遇到的绝大部分都是针对源同步的时序约束问题。所以下文讲述的主要是针对源同步的时序约束。 根据网络上收集的资料以及结合自

2020-11-20 14:44:52 6859

6859

6859

6859

VIVADO时序约束及STA基础

时序约束的目的就是告诉工具当前的时序状态,以让工具尽量优化时序并给出详细的分析报告。一般在行为仿真后、综合前即创建基本的时序约束。Vivado使用SDC基础上的XDC脚本以文本形式约束。以下讨论如何进行最基本时序约束相关脚本。

2022-03-11 14:39:10 8731

8731

8731

8731FPGA的IO口时序约束分析

在高速系统中FPGA时序约束不止包括内部时钟约束,还应包括完整的IO时序约束和时序例外约束才能实现PCB板级的时序收敛。因此,FPGA时序约束中IO口时序约束也是一个重点。只有约束正确才能在高速情况下保证FPGA和外部器件通信正确。

2022-09-27 09:56:09 1382

1382

1382

1382FPGA主时钟约束详解 Vivado添加时序约束方法

在FPGA设计中,时序约束的设置对于电路性能和可靠性都至关重要。在上一篇的文章中,已经详细介绍了FPGA时序约束的基础知识。

2023-06-06 18:27:13 6213

6213

6213

6213

FPGA时序约束之衍生时钟约束和时钟分组约束

在FPGA设计中,时序约束对于电路性能和可靠性非常重要。在上一篇的文章中,已经详细介绍了FPGA时序约束的主时钟约束。

2023-06-12 17:29:21 1230

1230

1230

1230FPGA时序约束之伪路径和多周期路径

前面几篇FPGA时序约束进阶篇,介绍了常用主时钟约束、衍生时钟约束、时钟分组约束的设置,接下来介绍一下常用的另外两个时序约束语法“伪路径”和“多周期路径”。

2023-06-12 17:33:53 868

868

868

868同步电路设计中静态时序分析的时序约束和时序路径

同步电路设计中,时序是一个主要的考虑因素,它影响了电路的性能和功能。为了验证电路是否能在最坏情况下满足时序要求,我们需要进行静态时序分析,即不依赖于测试向量和动态仿真,而只根据每个逻辑门的最大延迟来检查所有可能的时序违规路径。

2023-06-28 09:35:37 490

490

490

490

FPGA设计大家谈:让时序约束更简单—ETD第14期

1月10日,由电子发烧友网主办的FPGA技术沙龙顺利开展。本次沙龙邀请的是Altera代理商骏龙科技FAE张亚峰,嘉宾在沙龙现场为听众详解了“SDR源同步接口时序约束”。听众均来自车载系统、测试仪

2015-01-14 16:34:26 4704

4704

4704

4704ETD第12期:科技与体育的碰撞——智能羽毛球拍[深圳市]

。 但是目前业内企业关注的焦点似乎都在智能家居以及可穿戴设备上,做智能体育硬件的厂商是寥寥无几。从这也可看出智能体育硬件存在极大的发展空间,而科技体育是未来发展的必然趋势,此次ETD第12期技术沙龙有幸

2014-11-05 11:11:20

ETD第13期安防与智能家居技术沙龙PPT下载!

智能家居已然是大势所趋,业内企业如何在风口浪尖上赢得市场是大家最关心的。不难发现创新的产品设计是获取用户青睐的前提。对此,电子发烧友网ETD第13期技术沙龙邀请到安锐通科技秦总和科地通信龚总为大家

2014-12-09 10:51:21

ETD第14期SDR源同步接口时序约束方法视频出炉了!

电子发烧友网ETD第14期SDR源同步接口时序约束方法-会前交流电子发烧友网ETD第14期SDR源同步接口时序约束方法-演讲电子发烧友网ETD第14期SDR源同步接口时序约束方法-提问

2015-01-17 16:27:32

ETD第14期:SDR源同步接口时序约束方法

ETD第14期:SDR源同步接口时序约束方法活动详情 在设计接口时,要满足同步时钟和总线信号有确定的时序要求困扰了不少工程师,那么如何有效的解决此问题呢?同步接口约束是FPGA工程师常用的方法之一

2014-12-31 14:21:17

时序约束 专版

此版只讨论时序约束约束理论约束方法约束结果时钟约束(Clock Specification): 约束所有时钟(包括你的设计中特有的时钟)对准确的时序分析结果而言是必不可少的。Quartus II

2013-05-16 18:51:50

时序约束之时序例外约束

当逻辑行为以默认的方式不能正确的定时逻辑行为,想以不同的方式处理时序时,必须使用时序例外命令。1. 多周期路径约束指明将数据从路径开始传播到路径结束时,所需要的时钟周期

2018-09-21 12:55:34

时序约束是如何影响数字系统的,具体如何做时序分析?

的(频率和相位都同步),那么数据引脚和时钟引脚的时序关系以及从引脚到寄存器输入端的延时共同决定了第一个寄存器的建立时间和保持时间能否得到满足,设计者可以对数据引脚到寄存器输入端的延时进行约束。为了保证

2020-08-16 07:25:02

时序约束资料包

好的时序是设计出来的,不是约束出来的时序就是一种关系,这种关系的基本概念有哪些?这种关系需要约束吗?各自的详细情况有哪些?约束的方法有哪些?这些约束可分为几大类?这种关系仅仅通过约束来维持吗?1

2018-08-01 16:45:40

时序分析总结(以SDRAM时序约束为例)

都是以clock为基准的,记住这个,算的时候就很容易了;4.基本的时序约束有:时钟约束,IO约束,例外说明,这些都是可以通过timequest来设置的。所谓同步时序,寄存器在同一个时钟沿动作,所谓异步

2014-12-29 14:53:00

源同步时序系统之基本结构

,这个选通信号也可以称为源同步时钟信号。源同步时钟系统中,数据和源同步时钟信号是同步传输的,我们保证这两个信号的飞行时间完全一致,这样只要在发送端的时序是正确的,那么在接收端也能得到完全正确的时序。整个

2014-12-30 13:54:22

源同步的约束该怎么加?

最近遇到个问题,想请教一下大家 FPGA和一个芯片使用源同步的方式通讯,输出一个时钟CLK和一个数据总线DataData在内部由全局失踪clk0驱动,想知道Data的offset约束该怎么加啊? 我

2014-12-29 14:43:02

约束源怎么同步DDR接口

我有一个RGMII接口,时钟与边缘的数据DDR对齐。根据我的理解,我应该使用具有90°相位的再生时钟来采样具有最佳时序余量。这意味着我必须使用一个PLL我看到用于DDR接口的SelectIO内核,它

2019-03-12 09:56:10

FPGA时序约束--基础理论篇

FPGA开发过程中,离不开时序约束,那么时序约束是什么?简单点说,FPGA芯片中的逻辑电路,从输入到输出所需要的时间,这个时间必须在设定的时钟周期内完成,更详细一点,即需要满足建立和保持时间

2023-11-15 17:41:10

FPGA时序约束OFFSET

FPGA时序约束,总体来分可以分为3类,输入时序约束,输出时序约束,和寄存器到寄存器路径的约束。其中输入时序约束主要指的是从FPGA引脚输入的时钟和输入的数据直接的约束。共分为两大类:1、源同步系统

2015-09-05 21:13:07

FPGA时序约束的几种方法

Incremental Compilation。这是造成上述两种方法容易混淆的原因。5. 核心频率约束+时序例外约束+I/O约束+寄存器布局约束 寄存器布局约束是精确到寄存器或LE一级的细粒度布局约束。设计者

2017-12-27 09:15:17

FPGA时序约束的几种方法

控。从最近一段时间工作和学习的成果中,我总结了如下几种进行时序约束的方法。按照从易到难的顺序排列如下:0. 核心频率约束 这是最基本的,所以标号为0。1. 核心频率约束+时序例外约束 时序例外约束包括

2016-06-02 15:54:04

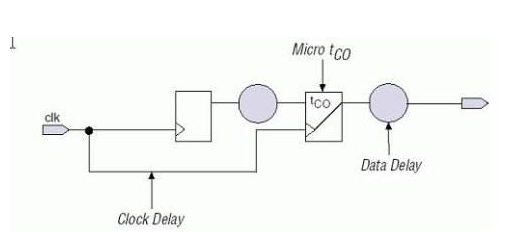

FPGA实战演练逻辑篇55:VGA驱动接口时序设计之2源同步接口

可以分析一下这个接口的时序要求,然后对其进行约束。这个输出的信号,其实是很典型的源同步接口,它的时钟和数据都是由FPGA来驱动产生的。一般的源同步接口的寄存器模型如图8.25所示。在我们的这个系统中

2015-07-29 11:19:04

FPGA实战演练逻辑篇56:VGA驱动接口时序设计之3时钟约束

,FPGA产生的数据data_out和时钟clk_out的理想波形是时钟上升沿锁存到稳定可靠的数据。(特权同学,版权所有)图8.26 源同步接口寄存器和时序波形关系下面我们来探讨如何对这个设计进行约束。首先

2015-07-30 22:07:42

FPGA实战演练逻辑篇61:CMOS摄像头接口时序设计1理想时序

/1pJ5bCtt 本实例的CMOS接口是时序分析中典型的pin2reg接口。由于详细的设计说明将在第12章中,因此大家可以先大体浏览过第12章,对整个系统设计有一定了解后,再来进行本节的pin2reg

2015-08-12 12:42:14

FPGA实战演练逻辑篇64:CMOS摄像头接口时序设计4时序约束

CMOS摄像头接口时序设计4时序约束(特权同学版权所有)本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》(特权同学版权所有)配套例程下载链接:http://pan.baidu.com/s

2015-08-18 21:24:30

FPGA沙龙:SDR源同步接口时序约束方法沙龙精彩内容回顾!

草丛中两只花,今天的沙龙现场我们还迎来了两位美女工程师,有木有感觉本次沙龙的氛围更加轻松了呢~~~!张工正在为大家介绍SDR源同步接口时序约束,学会这个保证你贯穿全部时序问题!会中认真听讲并记录

2014-12-31 14:25:41

xilinx 时序分析及约束

大部分的时序分析和约束都写在这里了。 一、基本时序路径1、clock-to-setup周期约束跨时钟域约束: (1)当源触发器和目标触发器的驱动时钟不同,且时钟的占空比不是50

2017-03-09 14:43:24

《EDA工具手册》约束管理器分册

第一章 约束管理器介绍41.1约束管理器简介41.2约束管理器界面简介81.2.1worksheet selector81.2.2用户接口91.2.3View选项91.3启动约束管理器11第2章

2017-11-10 12:30:42

【潘文明至简设计法】系列连载教程 FPGA时序约束视频教程

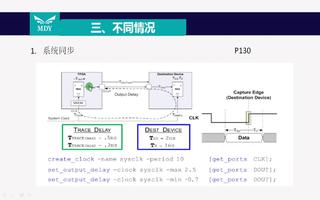

延时约束是约束的重点。明德扬把输入约束分成三大类:系统同步、源同步和无时钟数据,其中源同步分成SDR和DDR两场景,而DDR又可再细分成边沿对齐和中心对齐。以上每种情况,其约束语句、获取参数的方法都是

2017-06-14 15:42:26

【转帖】经验总结:FPGA时序约束的6种方法

控。 下文总结了几种进行时序约束的方法。按照从易到难的顺序排列如下: 0. 核心频率约束 这是最基本的,所以标号为0。1. 核心频率约束+时序例外约束 时序例外约束包括FalsePath

2017-10-20 13:26:35

与时钟频率不同的源同步数据如何约束?

考虑第4个约束。我还试图使用MMCM生成的时钟来设置OFFSET = IN约束TIMEGRP“sdr_c_0”OFFSET = IN 3.125 ns有效6.25 ns在“CMX_input_inst

2018-10-16 17:14:28

关于时序约束

本帖最后由 seduce 于 2015-2-3 14:20 编辑

关于约束今天在研究时序约束这一块,于是想着上来和大家分享一下心得,同时和大家交流交流,互相成长,欢迎批评指正。首先说一下

2015-02-03 14:13:04

关于FPGA时序约束的一点总结

)。方法2调试起来简单,PLL设置简单,出错可能性小。通过不断调整相位,最终肯定可以正确通信。缺点也明显,接口一多,每个都要做随路时钟就浪费了。最近一直在做时序约束,总结一下时序约束过程。(1)根据时序

2016-09-13 21:58:50

分享一个关于源同步接口时序分析与相移计算的例子

= ((td2- tc1-7ns)+( td1+7ns-tc2))/2 = (td2+td1-tc1-tc2)/2 回头看看,其实这类时序也是非常典型的源同步接口,和SDRAM接口相比,SDRAM不仅

2014-12-26 16:36:46

对边沿对齐源同步输入端口的约束

[get_ports data_in*] -add #对false path的约束。#对于源同步接口,virt_clk为Launch Clock#data_clock为Latch

2014-12-25 14:28:06

本人小白,请教什么是源同步接口?

最近经常看到有人在聊源同步接口,但是百度、谷歌也没找到太多相关的信息,不找到哪位大神可以解释一下什么是源同步接口啊?它的用途是什么呢?可以做些什么呀?十分感谢,本人小白,希望大家不要见笑哈!

2014-12-26 15:51:35

荣小菜补钙记第55期: AF消息传递太麻烦?试试接口吧!

荣小菜补钙记第55期: AF消息传递太麻烦?试试接口吧!同步更新于 WeChat:荣小菜在补钙欢迎关注 内容更丰富大家好,我是荣小菜,本期讲解下在操作者框架中使用接口类来传递消息的方法,该方法主要

2022-01-23 11:47:41

详解FPGA的时序以及时序收敛

参考ug612。4.输出时序约束输出就是输入的逆,因此分析的过程是类似的,分类也是类似的。针对时钟的不同,有系统同步和源同步两种。此处不再详细说明。系统同步SDR源同步DDR(一般来说不给约束就可以)5.

2019-07-09 09:14:48

请教时序约束的方法

我是一个FPGA初学者,关于时序约束一直不是很明白,时序约束有什么用呢?我只会全局时钟的时序约束,如何进行其他时序约束呢?时序约束分为哪几类呢?不同时序约束的目的?

2012-07-04 09:45:37

高云半导体时序约束的相关内容

实现时序约束以及如何阅读STA 报告。有关本手册中的高云半导体云源®软件(以下简称云源)界面截图参考的是 1.9.8.01 版本。因软件版本更新,部分信息可能会略有差异,具体以用户软件版本信息为准。

2022-09-29 08:09:58

同步时序逻辑电路

同步时序逻辑电路:本章系统的讲授同步时序逻辑电路的工作原理、分析方法和设计方法。从同步时序逻辑电路模型与描述方法开始,介绍同步时序逻辑电路的分析步骤和方法。然后

2009-09-01 09:06:27 0

0

0

0时序约束与时序分析 ppt教程

时序约束与时序分析 ppt教程

本章概要:时序约束与时序分析基础常用时序概念QuartusII中的时序分析报告

设置时序约束全局时序约束个别时

2010-05-17 16:08:02 0

0

0

0时序约束用户指南

时序约束用户指南包含以下章节: ?第一章“时序约束用户指南引言” ?第2章“时序约束的方法” ?第3章“时间约束原则” ?第4章“XST中指定的时序约束” ?第5章“Synplify中指定的时

2010-11-02 10:20:56 0

0

0

0Xilinx时序约束培训教材

时序约束的概念 时序约束主要包括周期约束(FFS到FFS,即触发器到触发器)和偏移约束(IPAD到FFS、FFS到OPAD)以及静态路径约束(STA, IPAD到OPAD)等3种。通过附加约束条件可以使综合布线工具调整映射和布局布线过程,使设计达到时序要求。例如用OFFSET_IN_BEFORE

2011-03-16 18:10:38 0

0

0

0FPGA开发之时序约束(周期约束)

偏移约束。 这里先说一下周期约束:周期约束是为了达到同步组件的时序要求。如果相邻同步原件相位相反,那么延迟就会是时钟约束值的一半,一般不要同时使用上升沿和下降沿。注意:在实际工程中,附加的约束时间为期望值的

2017-02-09 02:56:06 605

605

605

605基于FPGA 和 SoC创建时序和布局约束以及其使用

作时序和布局约束是实现设计要求的关键因素。本文是介绍其使用方法的入门读物。 完成 RTL 设计只是 FPGA 设计量产准备工作中的一部分。接下来的挑战是确保设计满足芯片内的时序和性能要求。为此

2017-11-17 05:23:01 2417

2417

2417

2417

FPGA中的时序约束设计

一个好的FPGA设计一定是包含两个层面:良好的代码风格和合理的约束。时序约束作为FPGA设计中不可或缺的一部分,已发挥着越来越重要的作用。毋庸置疑,时序约束的最终目的是实现时序收敛。时序收敛作为

2017-11-17 07:54:36 2326

2326

2326

2326

深入了解时序约束以及如何利用时序约束实现FPGA 设计的最优结果

作为赛灵思用户论坛的定期访客(见 ),我注意到新用户往往对时序收敛以及如何使用时序约束来达到时序收敛感到困惑。为帮助 FPGA设计新手实现时序收敛,让我们来深入了解时序约束以及如何利用时序约束实现

2017-11-24 19:37:55 4903

4903

4903

4903

添加时序约束的技巧分析

。 在添加全局时序约束时,需要根据时钟频率划分不同的时钟域,添加各自的周期约束;然后对输入输出端口信号添加偏移约束,对片内逻辑添加附加约束。

2017-11-25 09:14:46 2347

2347

2347

2347FPGA时序约束简介

在简单电路中,当频率较低时,数字信号的边沿时间可以忽略时,无需考虑时序约束。但在复杂电路中,为了减少系统中各部分延时,使系统协同工作,提高运行频率,需要进行时序约束。通常当频率高于50MHz时,需要考虑时序约束。

2018-03-30 13:42:59 14208

14208

14208

14208

【时序约束资料包】培训课程Timing VIVADO

好的时序是设计出来的,不是约束出来的 时序就是一种关系,这种关系的基本概念有哪些? 这种关系需要约束吗? 各自的详细情况有哪些? 约束的方法有哪些? 这些约束可分为几大类? 这种关系仅仅通过约束

2018-08-06 15:08:02 400

400

400

400进行时序约束的方法都在这里,赶紧收藏

1. 核心频率约束 这是最基本的,所以标号为0。 2. 核心频率约束+时序例外约束 时序例外约束包括FalsePath、MulticyclePath、MaxDelay、MinDelay。但这还

2018-09-21 22:04:01 1440

1440

1440

1440

如何使用时序约束向导

了解时序约束向导如何用于“完全”约束您的设计。

该向导遵循UltraFast设计方法,定义您的时钟,时钟交互,最后是您的输入和输出约束。

2018-11-29 06:47:00 2702

2702

2702

2702

时序约束步骤:系统同步与源同步

针对普通时钟系统存在着限制时钟频率的弊端,人们设计了一种新的时序系统,称之为源同步时序系统。它最大的优点就是大大提升了总线的速度,在理论上信号的传送可以不受传输延迟的影响。

2019-12-20 07:09:00 4151

4151

4151

4151

赛灵思关于I/O约束法的简要概括(下)

DDR接口的约束稍许复杂,需要将上升沿和下降沿分别考虑和约束,以下以源同步接口为例,分别就Setup/Hold Based 方法和Skew Based方法举例。

2019-07-25 11:01:38 2457

2457

2457

2457

FPGA时序约束的建立和保持时间方法

首先来看什么是时序约束,泛泛来说,就是我们告诉软件(Vivado、ISE等)从哪个pin输入信号,输入信号要延迟多长时间,时钟周期是多少,让软件PAR(Place and Route)后的电路能够

2020-01-28 17:34:00 3077

3077

3077

3077

Vivado进行时序约束的两种方式

上面我们讲的都是xdc文件的方式进行时序约束,Vivado中还提供了两种图形界面的方式,帮我们进行时序约束:时序约束编辑器(Edit Timing Constraints )和时序约束向导(Constraints Wizard)。两者都可以在综合或实现后的Design中打开。

2020-03-08 17:17:00 19067

19067

19067

19067

多时钟域的同步时序设计和几种处理异步时钟域接口的方法

在数字电路设计中,大部分设计都是同步时序设计,所有的触发器都是在同一个时钟节拍下进行翻转。这样就简化了整个设计,后端综合、布局布线的时序约束也不用非常严格。但是在设计与外部设备的接口部分时,大部分

2020-07-24 09:52:24 3920

3920

3920

3920

正点原子FPGA静态时序分析与时序约束教程

静态时序分析是检查芯片时序特性的一种方法,可以用来检查信号在芯片中的传播是否符合时序约束的要求。相比于动态时序分析,静态时序分析不需要测试矢量,而是直接对芯片的时序进行约束,然后通过时序分析工具给出

2020-11-11 08:00:00 58

58

58

58FPGA时序约束的6种方法详细讲解

对自己的设计的实现方式越了解,对自己的设计的时序要求越了解,对目标器件的资源分布和结构越了解,对EDA工具执行约束的效果越了解,那么对设计的时序约束目标就会越清晰,相应地,设计的时序收敛过程就会更可控。

2021-01-11 17:44:44 8

8

8

8FPGA时序约束的常用指令与流程详细说明

器件共用外部时钟;源同步(SDR,DDR)即时钟与数据一起从上游器件发送过来的情况。在设计当中,我们遇到的绝大部分都是针对源同步的时序约束问题。所以下文讲述的主要是针对源同步的时序约束。

2021-01-11 17:46:32 13

13

13

13FPGA时序约束的概念和基本策略

A 时序约束的概念和基本策略 时序约束主要包括周期约束(FFS到FFS,即触发器到触发器)和偏移约束(IPAD到FFS、FFS到OPAD)以及静态路径约束(IPAD到OPAD)等3种。通过附加

2021-09-30 15:17:46 4401

4401

4401

4401创建输入输出接口时序约束的窍门

时序约束中的 set_input_delay/set_output_delay 约束一直是一个难点,无论是概念、约束值的计算,还是最终的路径分析,每一次都要费一番脑子。Vivado为方便用户创建

2022-08-02 09:54:20 1797

1797

1797

1797

约束、时序分析的概念

很多人询问关于约束、时序分析的问题,比如:如何设置setup,hold时间?如何使用全局时钟和第二全局时钟(长线资源)?如何进行分组约束?如何约束某部分组合逻辑?如何通过约束保证异步时钟域之间

2023-05-29 10:06:56 372

372

372

372

如何在Vivado中添加时序约束呢?

今天介绍一下,如何在Vivado中添加时序约束,Vivado添加约束的方法有3种:xdc文件、时序约束向导(Constraints Wizard)、时序约束编辑器(Edit Timing Constraints )

2023-06-26 15:21:11 1847

1847

1847

1847

静态时序分析的基本概念和方法

向量和动态仿真 。本文将介绍静态时序分析的基本概念和方法,包括时序约束,时序路径,时序裕量,setup检查和hold检查等。 时序路径 同步电路设计中,时序是一个主要的考虑因素,它影响了电路的性能和功能。为了验证电路是否能在最

2023-06-28 09:38:57 714

714

714

714

电子发烧友App

电子发烧友App

评论