1.时序分析与约束

1.1 约束是FPGA设计不可或缺的,约束文件分为:

用户设计文件(.UCF),由用户输入

网表约束文件(.NCF),综合生成

物理约束文件(.PCF),实现生成

约束类型分为:

周期约束、偏移约束、静态路径约束;

1.2 高的工作频率意味着更加强大的处理能力,但带来了:时序冲突的概率变大以及电路的稳定性降低,为此必须进行时序、面积和负载等多方面的约束。

对于一般的低速设计(处理时钟不超过50MHz),基本上不需时序方面的处理。

1.3 时序分析贯穿整个FPGA设计,任何阶段时序分析不满足,都需重新修改代码或者调整时序约束。

2. 动态时序分析与静态时序分析

动态时序分析需要仿真条件, 需要输入向量,着重于逻辑功能;

静态时序分析不需要外部激励,着重于时序性能分析;

静态时序分析在分析过程中计算时序路径上数据信号的到达时间和要求时间的差值,以

判断是否违反设计规则的错误,即Slack (时裕量)= T_required_time(约束时长) – T_arrival_time (实际时延),Slack为正则满足时序。

3.时钟的时序特性:偏移(skew)、抖动(jitter)、占空比失真(duty cycle distortion)

时钟偏移:指同一信号到达两个不同寄存器之间的时间差值(原因:两条时钟路径长度不同) ,在设计中主要时钟应走全局时钟网络;

时钟抖动、占空比失真

4.时序裕量

约束文件要求的时钟周期与实际布局布线后时钟周期的差值

5.添加约束原则

先附加全局约束,再补充局部约束。目的是在可能的地方尽量放松约束,提高布线成功概率,减少布局布线时间。典型的全局约束包括周期约束和偏移约束。

在添加全局时序约束时,先根据时钟频率不同划分不同的时钟域,添加各自的周期约束;然后对输入输出信号添加偏移约束,对片内逻辑添加附加约束

6.硬件设计电路的最高工作频率

取决于芯片内部元件固有的建立时间和保持时间,以及同步元件之间的逻辑和布线延迟。即由芯片和代码共同决定。

7.周期约束

常用的策略是:附加的时钟周期约束的时长为期望值90%.

语法一:Net “信号名” period = 周期长度 high/low 脉冲持续时间

其中high/low指周期内第一个脉冲是高电平还是低电平,脉冲持续时间即该 脉冲的持续时间。

举例 Net “clk_100MHz” period = 10 ns High 5ns

指定了信号clk_100MHz的周期为10ns,搞电平持续为5ns,该约束将被添加到clk_100MHz所驱动的元件上。

8.偏移约束

规定了外部时钟和数据输入输出管脚之间的相对时序关系,只能用于端口信号,不能用于内部信号,语法结构:

OFFSET = [IN|OUT] “offset_time” [units] {BEFORE|AFTER} “clk_name” [TIMEGRP “group_name”]

[IN|OUT]:说明约束的是输入还是输出

offset_time:数据与有效时钟沿之间的时间差

[units]:时间差单位,缺省为ns

{BEFORE|AFTER}:表明该时间差实在时钟沿之前还是之后

“clk_name”:有效时钟名字

[TIMEGRP “group_name”]:用户添加的分组信号,缺省时为时钟“clk_name”所能驱动的所有触发器

偏移约束通知布局布线器输入数据的到达时刻,从而可准确调整布局布线的过程,使约束信号建立时间满足要求

举例:NET “DATA_IN” OFFSET = IN 10 BEFORE “CLK_50MHz”。

责任编辑:lq6

-

时序

+关注

关注

5文章

402浏览量

38627

原文标题:FPGA学习笔记-时序分析与约束

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

vivado时序分析相关经验

移植E203到Genesys2开发板时遇到时序问题的常见原因

时序约束问题的解决办法

关于综合保持时间约束不满足的问题

技术资讯 I Allegro 设计中的走线约束设计

一文读懂 PWM控制背光亮度原理

西门子再收购EDA公司 西门子宣布收购Excellicon公司 时序约束工具开发商

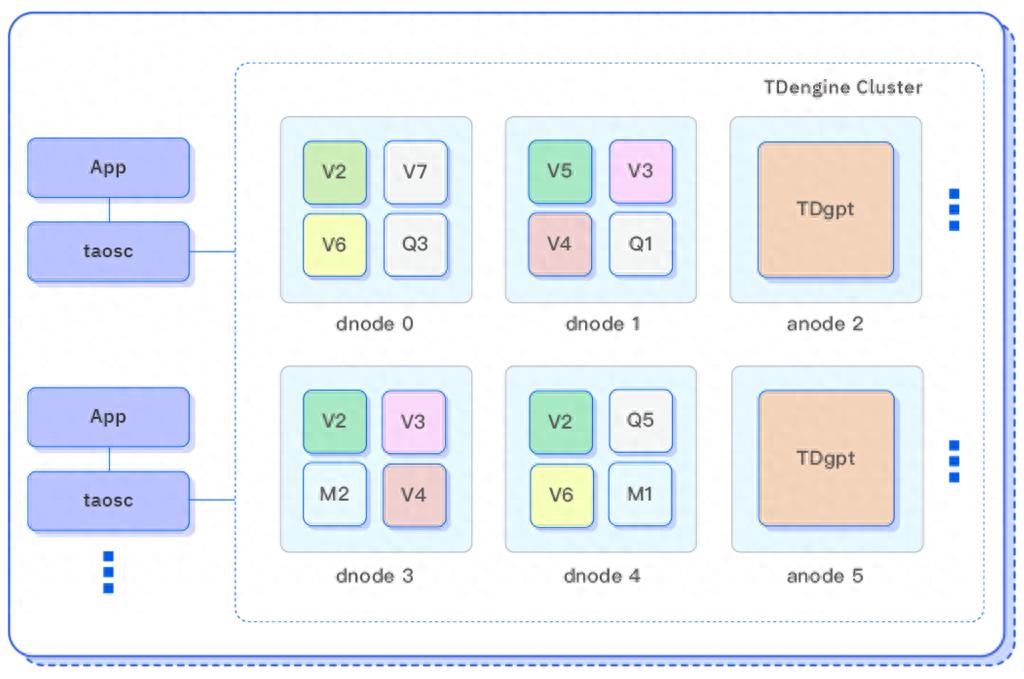

TDengine 发布时序数据分析 AI 智能体 TDgpt,核心代码开源

集成电路设计中静态时序分析介绍

一文读懂什么是「雷电4」

一文带你读懂EBSD

一文读懂时序分析与约束

一文读懂时序分析与约束

评论