时序例外约束包括FalsePath、MulticyclePath、MaxDelay、MinDelay。但这还不是最完整的时序约束。

2016-05-29 23:25:10 1064

1064 约束流程 说到FPGA时序约束的流程,不同的公司可能有些不一样。反正条条大路通罗马,找到一种适合自己的就行了。从系统上来看,同步时序约束可以分为系统同步与源同步两大类。简单点来说,系统同步

2020-11-20 14:44:52 6859

6859

时序约束的目的就是告诉工具当前的时序状态,以让工具尽量优化时序并给出详细的分析报告。一般在行为仿真后、综合前即创建基本的时序约束。Vivado使用SDC基础上的XDC脚本以文本形式约束。以下讨论如何进行最基本时序约束相关脚本。

2022-03-11 14:39:10 8731

8731 在高速系统中FPGA时序约束不止包括内部时钟约束,还应包括完整的IO时序约束和时序例外约束才能实现PCB板级的时序收敛。因此,FPGA时序约束中IO口时序约束也是一个重点。只有约束正确才能在高速情况下保证FPGA和外部器件通信正确。

2022-09-27 09:56:09 1382

1382 FPGA开发过程中,离不开时序约束,那么时序约束是什么?简单点说,FPGA芯片中的逻辑电路,从输入到输出所需要的时间,这个时间必须在设定的时钟周期内完成,更详细一点,即需要满足建立和保持时间。

2023-06-06 17:53:07 860

860

在FPGA设计中,时序约束的设置对于电路性能和可靠性都至关重要。在上一篇的文章中,已经详细介绍了FPGA时序约束的基础知识。

2023-06-06 18:27:13 6213

6213

在FPGA设计中,时序约束对于电路性能和可靠性非常重要。在上一篇的文章中,已经详细介绍了FPGA时序约束的主时钟约束。

2023-06-12 17:29:21 1230

1230 前面几篇FPGA时序约束进阶篇,介绍了常用主时钟约束、衍生时钟约束、时钟分组约束的设置,接下来介绍一下常用的另外两个时序约束语法“伪路径”和“多周期路径”。

2023-06-12 17:33:53 868

868 FPGA中时序约束是设计的关键点之一,准确的时钟约束有利于代码功能的完整呈现。进行时序约束,让软件布局布线后的电路能够满足使用的要求。

2023-08-14 17:49:55 711

711

时序路径作为时序约束和时序分析的物理连接关系,可分为片间路径和片内路径。

2023-08-14 17:50:02 452

452

前面讲解了时序约束的理论知识FPGA时序约束理论篇,本章讲解时序约束实际使用。

2023-08-14 18:22:14 842

842

”语句。5、FPGA 一般触发器资源比较丰富,而CPLD组合逻辑资源更丰富。6、FPGA和CPLD的组成:FPGA基本有可编程I/O单元、基本可编程逻辑单元、嵌入式 块RAM、丰富的布线资源、底层嵌入

2018-01-07 12:40:39

。 但是目前业内企业关注的焦点似乎都在智能家居以及可穿戴设备上,做智能体育硬件的厂商是寥寥无几。从这也可看出智能体育硬件存在极大的发展空间,而科技体育是未来发展的必然趋势,此次ETD第12期技术沙龙有幸

2014-11-05 11:11:20

智能家居已然是大势所趋,业内企业如何在风口浪尖上赢得市场是大家最关心的。不难发现创新的产品设计是获取用户青睐的前提。对此,电子发烧友网ETD第13期技术沙龙邀请到安锐通科技秦总和科地通信龚总为大家

2014-12-09 10:51:21

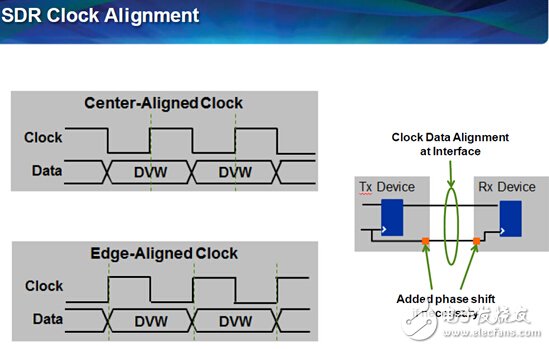

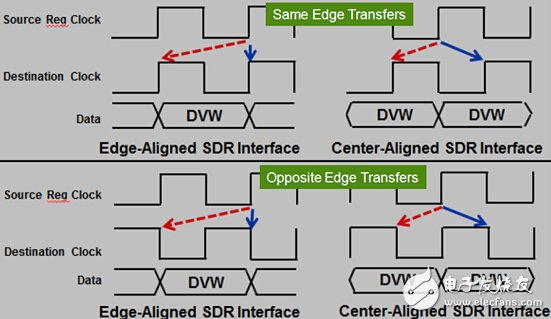

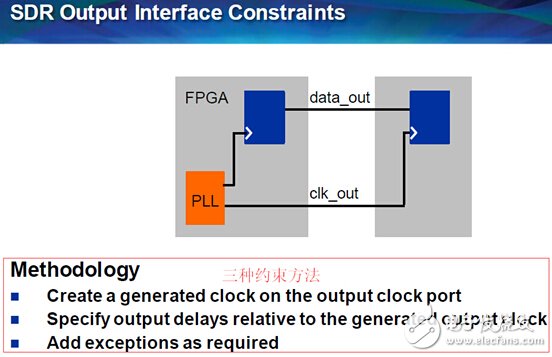

电子发烧友网ETD第14期SDR源同步接口时序约束方法-会前交流电子发烧友网ETD第14期SDR源同步接口时序约束方法-演讲电子发烧友网ETD第14期SDR源同步接口时序约束方法-提问

2015-01-17 16:27:32

ETD第14期:SDR源同步接口时序约束方法活动详情 在设计接口时,要满足同步时钟和总线信号有确定的时序要求困扰了不少工程师,那么如何有效的解决此问题呢?同步接口约束是FPGA工程师常用的方法之一

2014-12-31 14:21:17

FPGA开发过程中,离不开时序约束,那么时序约束是什么?简单点说,FPGA芯片中的逻辑电路,从输入到输出所需要的时间,这个时间必须在设定的时钟周期内完成,更详细一点,即需要满足建立和保持时间

2023-11-15 17:41:10

FPGA时序约束,总体来分可以分为3类,输入时序约束,输出时序约束,和寄存器到寄存器路径的约束。其中输入时序约束主要指的是从FPGA引脚输入的时钟和输入的数据直接的约束。共分为两大类:1、源同步系统

2015-09-05 21:13:07

刚刚看的一个非常不错的讲解时序约束的资料。在此分享下。

2015-01-21 15:14:35

FalsePath、MulticyclePath、MaxDelay、MinDelay。但这还不是最完整的时序约束。如果仅有这些约束的话,说明设计者的思路还局限在FPGA芯片内部。 2. 核心频率约束

2016-06-02 15:54:04

不是最完整的时序约束。如果仅有这些约束的话,说明设计者的思路还局限在FPGA芯片内部。 2. 核心频率约束+时序例外约束+I/O约束 I/O约束包括引脚分配位置、空闲引脚驱动方式、外部走线延时

2017-12-27 09:15:17

FPGA时序分析与约束(1)本文中时序分析使用的平台:quartusⅡ13.0芯片厂家:Inter1、什么是时序分析?在FPGA中,数据和时钟传输路径是由相应的EDA软件通过针对特定器件的布局布线

2021-07-26 06:56:44

你好: 现在我使用xilinx FPGA进行设计。遇到问题。我不知道FPGA设计是否符合时序要求。我在设计中添加了“时钟”时序约束。我不知道如何添加其他约束。一句话,我不知道哪条路径应该被禁止。我

2019-03-18 13:37:27

经过两天的恶补,特别是学习了《第五章_FPGA时 序收敛》及其相关的视频后,我基本上明白了时序分析的概念和用法。之后的几天,我会根据一些官方的文件对时序分析进行更系统、深入的学习。先总结一下之前

2011-09-23 10:26:01

FPGA毕竟不是ASIC,对时序收敛的要求更加严格,本文主要介绍本人在工程中学习到的各种时序约束技巧。 首先强烈推荐阅读官方文档UG903和UG949,这是最重要的参考资料,没有之一。它提倡

2020-12-23 17:42:10

发送方法适用于低速设备;后接DDR处理器,需要调整的,选择PLL方法;一般推荐使用锁相环(PLL)方法,在不够用的时候,可以选择DDIO方法会前大家正在进行简单的自我介绍并交流一些FPGA的现状分析万

2014-12-31 14:25:41

FPGA/CPLD的综合、实现过程中指导逻辑的映射和布局布线。下面主要总结一下Xilinx FPGA时序约束设计和分析。

2023-09-21 07:45:57

`为保证设计的成功,设计人员必须确保设计能在特定时限内完成指定任务。要实现这个目的,我们可将时序约束应用于连线中——从某 FPGA 元件到 FPGA 内部或 FPGA 所在 PCB 上后续元件输入

2012-03-01 15:08:40

,因此,为了避免这种情况,必须对fpga资源布局布线进行时序约束以满足设计要求。因为时钟周期是预先知道的,而触发器之间的延时是未知的(两个触发器之间的延时等于一个时钟周期),所以得通过约束来控制触发器之间的延时。当延时小于一个时钟周期的时候,设计的逻辑才能稳定工作,反之,代码会跑飞。

2018-08-29 09:34:47

FPGA高级时序综合教程The UCF FileUCF =用户约束文件( User Constraints File )可以用文本编辑器和XilinxConstraints Editor (GUI

2012-08-11 11:28:50

: 100.000MHz) --------------------------------------------------------------------------------整个程序非常的简单,时序约束报最高

2017-08-14 15:07:05

请教一下,FPGA由晶振输入的时钟,只是作为DCM输入,在其他各模块中没有用到,自己最简单的程序,时序约束报最高工作时钟也是100MHz,查资料这款FPGA最快可跑四五百M,请教一下,为什么我最简单的一个程序只能跑100MHz,是否是晶振输入时钟的延时所限制了?十分感谢

2017-08-11 10:55:07

好的时序是设计出来的,不是约束出来的时序就是一种关系,这种关系的基本概念有哪些?这种关系需要约束吗?各自的详细情况有哪些?约束的方法有哪些?这些约束可分为几大类?这种关系仅仅通过约束来维持吗?1

2018-08-01 16:45:40

小弟刚学习FPGA不久,仅仅学习了一个普通工作流,但对于时序约束什么的几乎一无所知最近在编一个模块时,VIVADO综合实现出来Timing那里是红色,WNS TNS为负值,只知道似乎是当前布线延迟

2015-09-06 20:08:42

满足vlx760 fpga的时序要求。将偏移输入/输出约束添加到vlx760 fpga-IN ANY WAY- 帮助满足125MHz周期约束?帮帮我 !!! :)ž。以上来自于谷歌翻译以下为原文hi

2019-04-08 10:27:05

Xilinx_fpga_设计:全局时序约束及试验总结

2012-08-05 21:17:05

在给 FPGA 做逻辑综合和布局布线时,需要在工具中设定时序的约束。通常,在 FPGA 中都包含有4 种路径:从输入端口到寄存器,从寄存器到寄存器,从寄存器到输出,从输入 到输出的纯组合逻辑

2012-03-05 15:02:22

本视频是MiniStar FPGA开发板的配套视频课程,主要通过工程实例介绍Gowin的物理约束和时序约束,课程内容包括gowin的管脚约束及其他物理约束和时序优化,以及常用的几种时序约束。 本

2021-05-06 15:40:44

结果。我们的优势:一个傻瓜式、但实用的时序约束“操作手册”。本系列视频,简单介绍了我们的“操作手册”,保证让你有意外的收获!另外,FPGA是实践课程,听一千遍,不如自己动手实践,练习才是最重要的内容

2017-06-14 15:42:26

、MulticyclePath、MaxDelay、MinDelay。但这还不是最完整的时序约束。如果仅有这些约束的话,说明设计者的思路还局限在FPGA芯片内部。2. 核心频率约束+时序例外约束+I/O约束 I/O

2017-10-20 13:26:35

cyclone系列FPGA时遇到的事儿【高手问答】第14期——如何升华51单片机基础,成为一个出色的开发工程师。【高手问答】第13期——向资深PCB设计师取经:如何设计高速PCB【高手问答】第12期——韦东山

2014-11-21 14:47:53

` Elecfans论坛高手问答第2期阿东带你走进fpga的逻辑编程设计本期高手问答(7月7日-7月14日)我们请来了 @100dongdong 为大家解答关于fpga的逻辑编程设计方面的问题。大牛

2014-07-07 14:30:15

` Elecfans论坛高手问答第3期走进硬件电路设计本期高手问答(7月14日-7月21日)我们请来了 @164908060 为大家解答关于硬件电路设计方面的问题。高手问答意义:为了更好的促进大家

2014-07-14 11:35:13

张工带你玩转STM32问答高手问答第9期小编导读: 一周一期的高手问答,又在周一与大家相见了。本期(8.25~8.31)的主题是与STM32相关的问答。我们请到了拥有丰富经验的张工。简介: 张工

2014-08-25 10:20:32

SDRAM数据手册有如张时序要求图。如何使SDRAM满足时序要求?方法1:添加时序约束。由于Tpcb和时钟频率是固定的,我们可以添加时序约束,让FPGA增加寄存器延时、寄存器到管脚的延时,从而使上述

2016-09-13 21:58:50

约束,实际上就是对软件布局布线提出一些要求,让布局布线的过程按照要求来,当然,这一点是非常有必要的,所以,研究时序约束最好是在有一块fpga的板子的情况下进行,这样,你能理解的更透彻。下面是正文,我用

2015-02-03 14:13:04

各位大神,我现在做一个FPGA的项目,现在verilog代码写得差不多了,通过modelsim仿真出来的数据看上去也没什么问题,然后我老板叫我做下时序分析,就是写时序约束,但是我才刚接触这个(之前

2016-08-12 11:19:28

小技巧和帮助来设置时钟;使用像Synopsys Synplify Premier一样的工具正确地设置时序约束;然后调整参数使之满足赛灵思FPGA设计性能的目标。会有来自不同角度的挑战,包括:?更好

2021-05-18 15:55:00

。掌握分析和确定关键路径时序的方法,并通过分析找出关键路径的时序问题,再对关键路径进行优化,通过RTL层面的不断优化,不断修炼自己的设计能力,让设计出来的电路更为靠谱有效!本资料属大西瓜FPGA开发团队,在此开源,与大家一起学习FPGA!

2017-02-26 09:42:48

在给FPGA做逻辑综合和布局布线时,需要在工具中设定时序的约束。通常,在FPGA设计工具中都FPGA中包含有4种路径:从输入端口到寄存器,从寄存器到寄存器,从寄存器到输出,从输入到输出的纯组合逻辑。

2019-11-08 07:27:54

本帖最后由 松山归人 于 2021-7-9 10:20 编辑

大家上午好!这是我们硬件实战教程的第14期内容,由鲁肃老师继续为大家带来一个实例项目的讲解。大家关于常用运放电路布局问题都可以

2021-07-09 10:19:51

总结时序收敛的目的是让FPGA design 按预设的逻辑正常的工作。为了使其正常工作,需要考虑至少三处:FPGA内部的寄存器-寄存器时序要求,FPGA输入数据的时序要求,FPGA输出信号的要求。

2019-07-09 09:14:48

我是一个FPGA初学者,关于时序约束一直不是很明白,时序约束有什么用呢?我只会全局时钟的时序约束,如何进行其他时序约束呢?时序约束分为哪几类呢?不同时序约束的目的?

2012-07-04 09:45:37

时序约束与时序分析 ppt教程

本章概要:时序约束与时序分析基础常用时序概念QuartusII中的时序分析报告

设置时序约束全局时序约束个别时

2010-05-17 16:08:02 0

0 时序约束用户指南包含以下章节: ?第一章“时序约束用户指南引言” ?第2章“时序约束的方法” ?第3章“时间约束原则” ?第4章“XST中指定的时序约束” ?第5章“Synplify中指定的时

2010-11-02 10:20:56 0

0 在设计接口时,要满足同步时钟和总线信号有确定的时序要求困扰了不少工程师,那么如何有效的解决此问题呢?同步接口约束是FPGA工程师常用的方法之一,但是,或许你在网上苦苦搜索教学视频后,还未能掌握

2014-12-26 10:02:26 23

23 FPGA时序约束方法很好地资料,两大主流的时序约束都讲了!

2015-12-14 14:21:25 19

19 赛灵思FPGA设计时序约束指南,下来看看

2016-05-11 11:30:19 48

48 FPGA学习资料教程之Xilinx时序约束培训教材

2016-09-01 15:27:27 0

0 小技巧和帮助来设置时钟;使用像Synopsys Synplify Premier一样的工具正确地设置时序约束;然后调整参数使之满足赛灵思FPGA设计性能的目标。 会有来自不同角度的挑战,包括: •更好的设计计划,例如完整的和精确的时序约束和时钟规范 •节约时间的

2017-02-09 01:59:11 264

264 时序约束可以使得布线的成功率的提高,减少ISE布局布线时间。这时候用到的全局约束就有周期约束和偏移约束。周期约束就是根据时钟频率的不同划分为不同的时钟域,添加各自周期约束。对于模块的输入输出端口添加

2017-02-09 02:56:06 605

605 Xilinx FPGA编程技巧常用时序约束介绍,具体的跟随小编一起来了解一下。

2018-07-14 07:18:00 4129

4129

作时序和布局约束是实现设计要求的关键因素。本文是介绍其使用方法的入门读物。 完成 RTL 设计只是 FPGA 设计量产准备工作中的一部分。接下来的挑战是确保设计满足芯片内的时序和性能要求。为此

2017-11-17 05:23:01 2416

2416

一个好的FPGA设计一定是包含两个层面:良好的代码风格和合理的约束。时序约束作为FPGA设计中不可或缺的一部分,已发挥着越来越重要的作用。毋庸置疑,时序约束的最终目的是实现时序收敛。时序收敛作为

2017-11-17 07:54:36 2326

2326

针对八通道采样器AD9252的高速串行数据接口的特点,提出了一种基于FPGA时序约束 的高速解串方法。使用Xilinx公司的FPGA接收高速串行数据,利用FPGA内部的时钟管理模块DCM、位置约束

2017-11-17 12:27:01 6488

6488

作为赛灵思用户论坛的定期访客(见 ),我注意到新用户往往对时序收敛以及如何使用时序约束来达到时序收敛感到困惑。为帮助 FPGA设计新手实现时序收敛,让我们来深入了解时序约束以及如何利用时序约束实现

2017-11-24 19:37:55 4903

4903

在简单电路中,当频率较低时,数字信号的边沿时间可以忽略时,无需考虑时序约束。但在复杂电路中,为了减少系统中各部分延时,使系统协同工作,提高运行频率,需要进行时序约束。通常当频率高于50MHz时,需要考虑时序约束。

2018-03-30 13:42:59 14208

14208

介绍FPGA约束原理,理解约束的目的为设计服务,是为了保证设计满足时序要求,指导FPGA工具进行综合和实现,约束是Vivado等工具努力实现的目标。所以首先要设计合理,才可能满足约束,约束反过来检查

2018-06-25 09:14:00 6374

6374 好的时序是设计出来的,不是约束出来的 时序就是一种关系,这种关系的基本概念有哪些? 这种关系需要约束吗? 各自的详细情况有哪些? 约束的方法有哪些? 这些约束可分为几大类? 这种关系仅仅通过约束

2018-08-06 15:08:02 400

400 不是最完整的时序约束。如果仅有这些约束的话,说明设计者的思路还局限在FPGA芯片内部。 3. 核心频率约束+时序例外约束+I/O约束 I/O约束包括引脚分配位置、空闲引脚驱动方式、外部走线延时

2018-09-21 22:04:01 1440

1440

FPGA中的时序问题是一个比较重要的问题,时序违例,尤其喜欢在资源利用率较高、时钟频率较高或者是位宽较宽的情况下出现。建立时间和保持时间是FPGA时序约束中两个最基本的概念,同样在芯片电路时序分析中也存在。

2019-12-23 07:01:00 1894

1894

首先来看什么是时序约束,泛泛来说,就是我们告诉软件(Vivado、ISE等)从哪个pin输入信号,输入信号要延迟多长时间,时钟周期是多少,让软件PAR(Place and Route)后的电路能够

2020-01-28 17:34:00 3077

3077

时序分析结果,并根据设计者的修复使设计完全满足时序约束的要求。本章包括以下几个部分: 1.1 静态时序分析简介 1.2 FPGA 设计流程 1.3 TimeQuest 的使用 1.4 常用时序约束 1.5 时序分析的基本概念

2020-11-11 08:00:00 58

58 下面举一个最简单的例子来说明时序分析的基本概念。假设信号需要从输入到输出在FPGA内部经过一些逻辑延时和路径延时。我们的系统要求这个信号在FPGA内部的延时不能超过15ns,而开发工具在执行过程中

2021-01-11 17:44:43 8

8 对自己的设计的实现方式越了解,对自己的设计的时序要求越了解,对目标器件的资源分布和结构越了解,对EDA工具执行约束的效果越了解,那么对设计的时序约束目标就会越清晰,相应地,设计的时序收敛过程就会更可控。

2021-01-11 17:44:44 8

8 说到FPGA时序约束的流程,不同的公司可能有些不一样。反正条条大路通罗马,找到一种适合自己的就行了。从系统上来看,同步时序约束可以分为系统同步与源同步两大类。简单点来说,系统同步是指FPGA与外部

2021-01-11 17:46:32 13

13 在FPGA 设计中,很少进行细致全面的时序约束和分析,Fmax是最常见也往往是一个设计唯一的约束。这一方面是由FPGA的特殊结构决定的,另一方面也是由于缺乏好用的工具造成的。好的时序约束可以指导布局布线工具进行权衡,获得最优的器件性能,使设计代码最大可能的反映设计者的设计意图。

2021-01-12 17:31:00 8

8 在高速系统中FPGA时序约束不止包括内部时钟约束,还应包括完整的IO时序约束利序例外约束才能实现PCB板级的时序收敛。因此,FPGA时序约束中IO口时序约束也是重点。只有约東正确才能在高速情况下保证FPGA和外部器件通信正确

2021-01-13 17:13:00 11

11 一、前言 无论是FPGA应用开发还是数字IC设计,时序约束和静态时序分析(STA)都是十分重要的设计环节。在FPGA设计中,可以在综合后和实现后进行STA来查看设计是否能满足时序上的要求。

2021-08-10 09:33:10 4768

4768

A 时序约束的概念和基本策略 时序约束主要包括周期约束(FFS到FFS,即触发器到触发器)和偏移约束(IPAD到FFS、FFS到OPAD)以及静态路径约束(IPAD到OPAD)等3种。通过附加

2021-09-30 15:17:46 4401

4401 A 时序约束的概念和基本策略 时序约束主要包括周期约束(FFS到FFS,即触发器到触发器)和偏移约束(IPAD到FFS、FFS到OPAD)以及静态路径约束(IPAD到OPAD)等3种。通过附加

2021-10-11 10:23:09 4861

4861

本文章探讨一下FPGA的时序约束步骤,本文章内容,来源于配置的明德扬时序约束专题课视频。

2022-03-16 09:17:19 3255

3255

上一篇《FPGA时序约束分享01_约束四大步骤》一文中,介绍了时序约束的四大步骤。

2022-03-18 10:29:28 1323

1323

本文章探讨一下FPGA的时序input delay约束,本文章内容,来源于配置的明德扬时序约束专题课视频。

2022-05-11 10:07:56 3462

3462

很多读者对于怎么进行约束,约束的步骤过程有哪些等,不是很清楚。明德扬根据以往项目的经验,把时序约束的步骤,概括分成四大步

2022-07-02 10:56:45 4974

4974

明德扬有完整的时序约束课程与理论,接下来我们会一章一章以图文结合的形式与大家分享时序约束的知识。要掌握FPGA时序约束,了解D触发器以及FPGA运行原理是必备的前提。今天第一章,我们就从D触发器开始讲起。

2022-07-11 11:33:10 2922

2922

本文章探讨一下FPGA的时序input delay约束,本文章内容,来源于明德扬时序约束专题课视频。

2022-07-25 15:37:07 2379

2379

时序约束是我们对FPGA设计的要求和期望,例如,我们希望FPGA设计可以工作在多快的时钟频率下等等。因此,在时序分析工具开始对我们的FPGA设计进行时序分析前,我们必须为其提供相关的时序约束信息

2022-12-28 15:18:38 1893

1893 本章节主要介绍一些简单的时序约束的概念。

2023-03-31 16:37:57 928

928

FPGA/CPLD的综合、实现过程中指导逻辑的映射和布局布线。下面主要总结一下Xilinx FPGA时序约束设计和分析。

2023-04-27 10:08:22 768

768 的数据交换可靠?如何使用I/O逻辑单元内部的寄存器资源?如何进行物理区域约束,完成物理综合和物理实现?为了解决大家的疑难,我们将逐一讨论这些问题。(注:以下主要设计时序约束)

2023-05-29 10:06:56 372

372

前面几篇文章已经详细介绍了FPGA时序约束基础知识以及常用的时序约束命令,相信大家已经基本掌握了时序约束的方法。

2023-06-23 17:44:00 1260

1260

STA(Static Timing Analysis,即静态时序分析)在实际FPGA设计过程中的重要性是不言而喻的

2023-06-26 09:01:53 362

362

FPGA开发过程中,离不开时序约束,那么时序约束是什么?简单点说,FPGA芯片中的逻辑电路,从输入到输出所需要的时间,这个时间必须在设定的时钟周期内完成,更详细一点,即需要满足建立和保持时间。

2023-06-26 14:42:10 344

344

FPGA设计中,时序约束对于电路性能和可靠性非常重要。

2023-06-26 14:53:53 820

820

今天介绍一下,如何在Vivado中添加时序约束,Vivado添加约束的方法有3种:xdc文件、时序约束向导(Constraints Wizard)、时序约束编辑器(Edit Timing Constraints )

2023-06-26 15:21:11 1847

1847

很多小伙伴开始学习时序约束的时候第一个疑惑就是标题,有的人可能会疑惑很久。不明白时序约束是什么作用,更不明白怎么用。

2023-06-28 15:10:33 828

828

本文主要介绍了时序设计和时序约束。

2023-07-04 14:43:52 692

692

电子发烧友App

电子发烧友App

评论