VHDL中Loop动态条件的可综合转化

- vhdl(131484)

相关推荐

热点推荐

VHDL中while循环中的警告

我想通过VHDL代码制作模数程序,我已经制作了这个代码库IEEE;使用IEEE.std_logic_1164.all;使用IEEE.std_logic_arith.all

2019-01-21 13:45:55

VHDL与verilog中if判断条件的一点小区别

进行VHDL和verilog混合编程,发现其间if判断条件的一点小区别,归纳如下:VHDL:if 内容如果是signal类型如signal a,只能写成if(a = '0'),不能

2012-04-09 09:24:22

vhdl实用教程pdf下载

8章)、VHDL综合和可综合的VHDL程序设计技术(第9章)、VHDL基本设计和实用设计(第10、11章)、多种常用的支持VHDL的EDA软件使用(第12章)、VHDL数字系统设计实践(第13章

2008-06-04 10:31:29

可综合的VerilogHDL设计实例

可综合的VerilogHDL设计实例在前面七章里我们已经学习了VerilogHDL的基本语法、简单组合逻辑和简单时序逻辑模块的编写、Top-Down设计方法、还学习了可综合风格的有限状态机

2009-11-23 16:01:33

DDR SDRAM参考设计VHDL版(有详细的文档,仿真综合文件)

DDR SDRAM参考设计VHDL版(有详细的文档,仿真综合文件)File/Directory Description

2012-08-11 09:33:30

FPGA vhdl语言 process for loop循环

process(a)beginfor i in 1 to 27 loop 当a变化一次 for循环执行几次?

2019-03-19 10:45:47

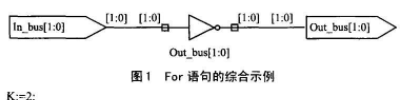

FPGA实战演练逻辑篇38:可综合的语法子集3

( or )begin//具体逻辑End(7) 运算操作符:各种逻辑操作符、移位操作符、算术操作符大多是可综合的。(特权同学,版权所有)Verilog中绝大多数运算操作符都是可综合的,其列表如下:+// 加

2015-06-17 11:53:27

ISE 自带可综合模块的问题

,都有Xilinx公司自己写好的可综合的模块,想请教一下为什么要分成这样两项?它们里面的模块有区别吗?2、上述谈到的可综合模块和ISE 自带的IP core又有什么区别呢?

2013-09-28 18:17:54

ISE 自带可综合模块的问题

,都有Xilinx公司自己写好的可综合的模块,想请教一下为什么要分成这样两项?它们里面的模块有区别吗?2、上述谈到的可综合模块和ISE 自带的IP core又有什么区别呢?

2013-09-28 18:20:29

verilog HDL 可综合模型的结构

可综合模型的结构如果程序只用于仿真,那么几乎所有的语法和编程语句都可以使用。但如果程序是用于硬件实现,那么我们就必须保证程序的可综合性,即所编写的程序能被综合器转化为相应的电路结构。不可综合的HDL

2012-10-20 08:10:13

verilog可综合与不可综合-学习一下

会报错。 如:a=#10 b; 这里的#10是用于仿真时的延时,在综合的时候综合工具会忽略它。也就是说,在综合的时候上式等同于a=b; 13、与X、Z的比较 可能会有人喜欢在条件表达式中把数据和X(或Z)进行比较,殊不知这是不可综合的,综合工具同样会忽略。所以要确保信号只有两个状态:0或1。

2015-01-05 19:42:44

【FPGA学习】VHDL 顺序语句描述方法 VHDL的if、case、LOOP、NEXT语句怎么写

序流、控制、条件和迭代等。VHDL 中的顺序语句有 WAIT 语句、断言语句、IF 语句、CASE 语句、LOOP 语句、NEXT 语句、过程调用语句和 NULL 语句,下面就对它们进行详细介绍

2018-09-13 09:39:31

介绍FPGA的综合(转)

XST支持哪些语言?VHDL, Verilog-2002, 以及Mixed Language of VHDL and Verilog。所支持的可综合的VHDL和Verilog的子集可以查看XST

2018-08-08 10:31:27

关于动态调用可重入vi的问题!

vi设置成可重入的方式,又做了一个动态调用的这个视频存储vi的vi,然后现在一动态调用就整个labview关闭?如果提前打开这个视频存储vi,再次动态调用,将不会崩溃,请问怎么这是什么情况?

2021-03-07 15:18:31

关于是否可综合的问题

“在进行信号定义的语法结构中,对信号赋初始值的操作是不可综合的,只能用来仿真。”请教一下各位,我在一段VHDL中对一个定义的数组信号赋初始值,仅此一个操作,然后通过spi协议与dsp传输,并且在监控屏上显示出来了,这是否理解为“综合后”的结果?可又与上面一段话相违背,该如何理解?

2017-07-21 17:21:06

勇敢的芯伴你玩转Altera FPGA连载33:可综合的语法子集4

大多是可综合的。Verilog中绝大多数运算操作符都是可综合的,其列表如下:+// 加-// 减!// 逻辑非~// 取反&// 与~&// 与非|// 或~|// 或非

2017-12-19 21:36:24

在verilog中调用VHDL模块

郁闷了,表示只看过VHDL语法但没写过。暂且不说VHDL模块的内容,我应该如何在测试平台中例化它并对它进行测试呢?稍微查了一下,其实很简单,只要把VHDL中的组件名、端口统统拿出来,按照verilog

2018-07-09 01:14:18

基于VHDL逻辑电路设计与应用

加法器的实现 串行加法器的VHDL描述由移位寄存器和加法器有限状态机组成。可以把移位寄存器作为一个子电路,在主程序中可以多次调用。 3.1移位寄存器实现 下面是4位移位寄存器的VHDL代码,采用

2018-11-20 10:39:39

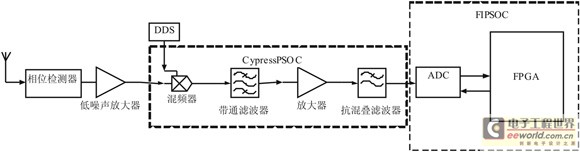

基于PAD的接收机动态可重构结构应用

和ASIC电路高速性的解决方案。在笔者所从事的系统设计中,当模拟器件的一些性能改变但又不能及时更新调整后端的数字基带处理时,比如滤波器由于工作时间过长引起的温漂特性所带来的影响,此时就可以用可编程模拟器件替代一部分前端固定模拟器件,进而可以实时的对FPGA模块进行动态可重构操作,最终达到系统性能的最优化。

2019-07-10 07:56:06

如何为后综合模拟和/或后PAR网表模拟生成VHDL或Verilog网表?

嗨,Vivado的新手问题;是否有可能为后综合模拟和/或后PAR网表模拟生成VHDL或Verilog网表?谢谢,埃里克

2019-11-11 07:33:05

如何用VHDL、Verilog HDL实现设计输入?

如何在ALTERA公司的Quartus II环境下用VHDL、Verilog HDL实现设计输入,采用同步时钟,成功编译、综合、适配和仿真,并下载到Stratix系列FPGA芯片EP1S25F780C5中。

2021-04-15 06:19:38

怎么将VHDL生成循环索引

want to increment vhdl generate loop index by 2.An example is show below, LABEL: for i in 1 to CNTR_WIDTH -1 generateREG1(i)

2019-01-16 08:12:42

怎么设计PAD在接收机动态可重构结构中的应用?

可重构结构是一种可以根据具体运算情况重组自身资源,实现硬件结构自身优化、自我生成的计算技术。动态可重构技术可快速实现器件的逻辑重建,它的出现为处理大规模计算问题提供了一种兼具通用处理器灵活性和ASIC电路高速性的解决方案。

2019-08-13 07:56:00

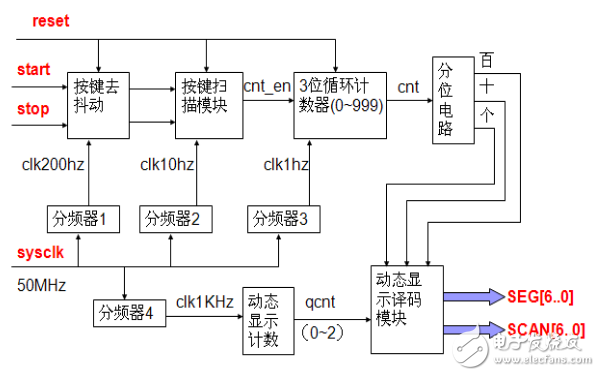

求助帮忙用vhdl实现一段fpga框图,(价钱可商议),急用!...

求助帮忙用vhdl实现一段fpga框图,(价钱可商议),急用!!!!求助帮忙用vhdl实现几个fpga框图,(价钱可商议),急用!!!!已经有现成的vhdl程序编码主要是想完成资料里面已经有的框图出来,,写材料需要用的~~~有意者请联系我的QQ:444741540 或者***~~越快越好~~~~

2013-03-29 18:04:41

浅谈IC设计中逻辑综合

和面积约束,按照一定的算法对翻译结果进行逻辑重组和优化。1.3映射:根据所施加的时序和面积约束,从目标工艺库中搜索符合条件的单元来构成实际电路的逻辑网表。约束条件是综合过程的重要组成部分,综合正是通过

2013-05-16 20:02:50

给VHDL/Verilog的初学者的一些实用建议

一本能完全将清楚所有的问题!今天无意中看到这篇文章,看来对于是否可综合依然是要靠经验判断!希望有一天能对常用的综合问题有个细致的了解!一、HDL不是硬件设计语言过去笔者曾碰到过不少VHDL或

2019-03-27 07:00:00

X-HDL v3.2.55 VHDL/Verilog语言翻译器

X-HDL:软件简介—SoftWare Description: X-HDL v3.2.55 VHDL/Verilog语言翻译器

一款VHDL/Verilog语言翻译器。可实现VHDL和Verilog语言的相互智能化转化。这分别是windows、linux、solaris版本。

2006-03-25 12:00:47 357

357

357

357VHDL中Loop动态条件的可综合转化

论述VHDL 中Loop 语句动态表达式的可综合性问题,提出三种解决方法:直接代入法、边界扩充法和计数器法, 并对比这三类方法的适用性。

2009-04-16 09:12:12 8

8

8

8VHDL在高速图像采集系统中的应用设计

介绍高速图像采集系统的硬件结构及工作原理, 讲述FPGA 在图像采集与数据存储部分的VHDL 模块设计, 给出采集同步模块的VHDL 源程序。

2009-04-16 10:45:55 15

15

15

15VHDL语言及其应用

VHDL语言及其应用的主要内容:第一章 硬件模型概述第二章 基本的VHDL编程语言第三章 VHDL模型的组织第四章 VHDL综合工具第五章 VHDL应用样例附录A VHDL

2009-07-20 12:06:15 0

0

0

0可转化的基于EIGamal环签名方案

可转化的环签名是允许真实签名人通过揭露关于此环签名的一些信息而把环签名转化为普通签名,并证明他是真实环签名人的签名方案。本文详细分析并指出文献[1]中基于EIGamal

2009-08-21 08:41:33 21

21

21

21高动态范围条件重置方法的改进研究

条件重置方法是提高CMOS 图像传感器动态范围的有效方法之一,但方法本身存在着一些缺点。为了提高条件重置方法的准确度,文章对条件重置方法进行了分析,对存在的缺点进行了

2009-08-31 14:20:44 5

5

5

5vhdl数字系统设计

vhdl数字系统设计是数字电路自动化设计(EDA)入门的工具书。其内容主要包括:用VHDL语言设计的基本组合电路、时序电路、数字综合电路、电路图输入法要领概述、实用VHDL语句

2009-10-08 21:54:01 0

0

0

0VHDL基础教程

VHDL基础教程:VHDL语言及其应用目录:第1章 VHDL基本概念 1.1 数字系统建模 1.2 建模的域和级 1.3 建模语言 1.4 VHDL建模的概念 1.5 一个VHDL设计实例 1 6

2009-10-16 18:17:58 359

359

359

359VHDL数位电子钟

VHDL 数位电子钟在这个数位电子钟我们使用可支持VHDL 格式的MAX+plusII 软件开发工具来做设计,利用VHDL 硬件描述语言的方式,将一个复杂的电路写成一颗IC,有错误也不用像以前

2009-11-22 17:50:38 174

174

174

174在PLD开发中提高VHDL的综合质量

介绍可编程逻辑器件的开发流程,叙述EDA工具Quartus II和LeonardoSpectrum在Altera公司CPLD器件开发中的应用,给出提高VHDL综合质量的几点经验。关键词:电子设计自动化 可编程逻辑

2010-07-18 10:38:50 22

22

22

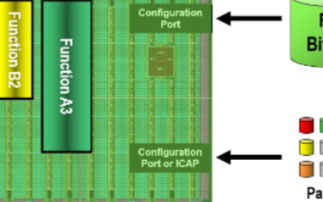

22FPGA的全局动态可重配置技术

FPGA的全局动态可重配置技术主要是指对运行中的FPGA器件的全部逻辑资源实现在系统的功能变换,从而实现硬件的时分复用。提出了一种基于System ACE的全局动态可重配置设计方法,

2011-01-04 17:06:01 54

54

54

54Selectable-Range Current Loop

Abstract: This article shows an example of implementing a 4-20mA or 0-20mA current-loop output

2009-04-20 11:22:47 1262

1262

1262

1262

在PLD开发中提高VHDL的综合质量

介绍可编程逻辑器件的开发流程,叙述EDA工具Quartus II和LeonardoSpectrum在Altera公司CPLD器件开发中的应用,给出提高VHDL综合质量的几点经验。

关键词 电子设计自动化 可编程逻辑

2009-06-16 08:55:30 550

550

550

550

在PLD开发中提高VHDL的综合质量

摘 要:介绍可编程逻辑器件的开发流程,叙述EDA工具Quartus II和LeonardoSpectrum在Altera公司CPLD器件开发中的应用,给出提高VHDL综合质量的几点经验。

关键词:电

2009-06-20 12:06:06 887

887

887

887

VHDL设计中电路简化问题的探讨

摘 要:从描述方法、设计规则、逻辑函数分析了VHDL设计中容易引起电路复杂化的原因,并提出了相应的解决方法。

关键词:VHDL 电路简化

2009-06-20 12:36:47 1188

1188

1188

1188

VHDL在高速图像采集系统中的应用设计

摘要:介绍高速图像采集系统的硬件结构及工作原理,讲述FPGA在图像采集与数据存储部分的VHDL模块设计,给出采集同步模块的VHDL源程序。

关键

2009-06-20 14:35:02 919

919

919

919

设计与验证复杂SoC中可综合的模拟及射频模型

设计与验证复杂SoC中可综合的模拟及射频模型

设计用于SoC集成的复杂模拟及射频模块是一项艰巨任务。本文介绍的采用基于性能指标规格来优化设计(如PLL或ADC等)的方

2009-12-26 14:38:13 802

802

802

802PAD在接收机动态可重构结构中的应用设计

PAD在接收机动态可重构结构中的应用设计

可重构结构是一种可以根据具体运算情况重组自身资源,实现硬件结构自身优化、自我生成的计算技术。动态可重构技术可快

2009-12-28 09:15:32 998

998

998

998

VHDL基本语言现象和实用技术教程

本书比较系统地介绍了VHDL 的基本语言现象和实用技术全书以实用和可操作 为基点简洁而又不失完整地介绍了VHDL 基于EDA 技术的理论与实践方面的知识 其中包括VHDL 语句语法基础知识第1 章第7 章逻辑综合与编程技术第9 章 有限状态机及其设计第10 章基于FPGA

2011-03-03 15:47:13 0

0

0

0基于动态阈值的视频对比度调节电路设计

提出了基于动态阈值的视频对比度调节算法! 并通过VHDL 进行硬件描述! 采用SMIC CNOS工艺标准单元库进行逻辑综合及布局布线!最后!进行了后级仿真

2011-05-17 10:48:28 0

0

0

0VHDL程序实例

本书是数字电路电子设计自动化(EDA)入门的工具书,其内容主要包括:用 VHDL 设计的基本组合电路、时序电路、数字综合电路、电路图输入法要领概述、实用VHDL语句等;附录部分介绍了

2011-08-04 10:17:43 0

0

0

0HDL的可综合设计简介

本文简单探讨了verilog HDL设计中的可综合性问题,适合HDL初学者阅读 用组合逻辑实现的电路和用时序逻辑实现的 电路要分配到不同的进程中。 不要使用枚举类型的属性。 Integer应加范围

2012-01-17 11:17:03 0

0

0

0VHDL语言要素

VHDL语言要素,大学EDA课程必备资料,在实际的应用中,VHDL仿真器讲INTEGER类型的数据作为有符号数处理,而综合器将INTEGER作为无符号数处理. VHDL综合器要求利用RANGE子句为

2016-11-21 15:40:34 0

0

0

0关于ZYNQ HLS图像处理加速总结的分享

HLS工具 以个人的理解,xilinx将HLS(高层次综合)定位于更方便的将复杂算法转化为硬件语言,通过添加某些配置条件HLS工具可以把可并行化的C/C++的代码转化为vhdl或verilog,相比于纯人工使用vhdl实现图像算法,该工具综合出的代码的硬件资源占用可能较多。

2019-10-12 17:34:00 2937

2937

2937

2937

可重构技术分析及动态可重构系统设计

基于SRAM的FPGA的问世标志着现代可重构技术的开端,并极大地推动了其发展。可编程FPGA可以根据不同算法设计合理的硬件结构,以达到提高执行效率的目的。动态可重构FPGA可以在程序运行中动态完成

2017-11-25 10:20:01 14505

14505

14505

14505

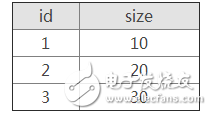

SQL中on条件与where条件的区别

SQL中on条件与where条件的区别 数据库在通过连接两张或多张表来返回记录时,都会生成一张中间的临时表,然后再将这张临时表返回给用户。 在使用left jion时,on和where条件的区别如下

2017-11-28 14:34:50 3635

3635

3635

3635

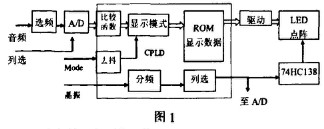

基于VHDL语言和CPLD器件实现频谱电平动态显示电路的设计

LED点阵显示屏具有醒目、动态效应好、省电节能、亮度较高、用途广等优点,是现代 化城市的主要标志之一。利用VHDL硬件描述语言设计了以CPLD器件为核心的控制电路, 在LED点阵屏上实现了音频信号的频谱型电平动态显示, 而且具有显示模式多样化、易编程 修改,颜色可变、动态效果好等优点。

2019-04-26 08:08:00 3076

3076

3076

3076

如何设计可综合的Verilog代码和应该遵循什么原则

在接触Verilog 语法参考手册的时候,我们发现其提供了一组非常丰富的功能来描述硬件。所以大家往往会疑惑那些Verilog语句是可综合的,那些是只能用于写Testbench的,其实,参考手册中只有

2019-04-20 10:59:39 5221

5221

5221

5221loop设备是Linux系统中不可缺少的一环

loop设备是一种伪设备,是使用文件来模拟块设备的一种技术,文件模拟成块设备后, 就像一个磁盘或光盘一样使用。在使用之前,一个 loop 设备必须要和一个文件进行连接。这种结合方式给用户提供了一个替代块特殊文件的接口。

2019-04-28 15:09:58 2025

2025

2025

2025VHDL硬件描述语言入门教程资料免费下载

本文档的主要内容详细介绍的是VHDL硬件描述语言入门教程资料免费下载包括了:1. VHDL语言基础,2. VHDL基本结构,3. VHDL语句,4. 状态机在VHDL中的实现,5. 常用电路VHDL程序,6. VHDL仿真,7. VHDL综合

2019-04-08 08:00:00 54

54

54

54Verilog可综合的循环语句

Verilog中提供了四种循环语句,可用于控制语句的执行次数,分别为:for,while,repeat,forever。其中,for,while,repeat是可综合的,但循环的次数需要在编译之前就确定,动态改变循环次数的语句是不可综合的。forever语句是不可综合的,主要用于产生各种仿真激励。

2019-10-13 12:23:00 20332

20332

20332

20332vhdl语言怎么仿真_vhdl语言的基本结构

在VHDL程序中,实体(ENTITY)和结构体(ARCHITECTURE)这两个基本结构是必须的,他们可以构成最简单的VHDL程序。通常,最简单的VHDL程序结构中还包含另一个最重要的部分,即库(LIBRARY)和程序包(PACKAGE)。

2020-04-23 15:43:38 5841

5841

5841

5841在没有综合工具情况下,如何设计数字电路?

虽然在FPGA中,利用综合工具来可以将VHDL或者Verilog代码转化成电路。但是作为FPGA工程师而言,在没有综合工具的情况下,如何设计出数字电路呢?如果已经知道需要实现的功能的状态机,如何将它转化成数字电路呢?和设计出数字电路呢?

2020-06-17 16:33:38 3746

3746

3746

3746如何在VHDL中解决综合工具使用转化问题

其措施能力超越了数字逻辑集成电路的范围。而现有的EDA工具基本上只能支持VHDL的子集,特别是针对FPGA/CPLD器件进行的不同的综合工具,其综合子集并非统一,不少初学者很难掌握。

2020-09-11 18:03:09 3287

3287

3287

3287

VHDL的参考手册免费下载

本手册讨论VHDL和Synario可编程IColution。本手册旨在补充可编程IC入门手册中的材料本手册中讨论了以下主题HDL语言结构如何编写可合成的VHDL如何控制VHDL设计的实现VHDL数据

2021-01-21 16:02:13 34

34

34

34VHDL最经典的参考指南资料免费下载

VHDL黄金参考指南是一个紧凑的快速参考指南VHDL语言,其语法,语义,综合和应用程序的硬件设计。《VHDL黄金参考指南》并不打算取代IEEE标准VHDL语言参考手册。与该文档不同的是,《黄金

2021-01-21 16:30:54 36

36

36

36浅谈条件语句的可综合性

条件语句的可综合性 HDL语言的条件语句与算法语言的条件语句,最大的差异在于: 1.不管条件:当前输入条件没有对应的描述,则该条件为不管条件(Don’t Care)。对应不管条件的信号称为不管信号

2021-05-12 09:12:22 2329

2329

2329

2329

简述HDL中循环语句的可综合性

在HDL的循环语句中,在指定的循环过程中,其代码块(循环体)输出同名信号,则构成顺序-循环(SAS-LOOP),其代码块(循环体)输出不同名信号,则构成并发-循环(CAS-LOOP)。 包括循环语句

2021-05-12 09:27:48 2830

2830

2830

2830

FPGA动态可重构技术是什么,局部动态可重构的时序问题解决方案

所谓FPGA动态可重构技术,就是要对基于SRAM编程技术的FPGA实现全部或部分逻辑资源的动态功能变换。根据实现重构的面积不同,动态可重构技术又可分为全局重构和局部重构。

2021-07-05 15:41:29 4214

4214

4214

4214

VHDL-AMS格式热电联合仿真

模型,从而电子部件可以进行系统仿真。 VHDL-AMS格式热电联合仿真 基于IEEE标准1076.1标准,校核过的电子产品模型在Simcenter Flotherm中可转化为Spice格式的热网络模型

2021-08-13 09:25:59 2876

2876

2876

2876LOOP指令——汇编语言学习笔记3

因为嵌入式系统学习需要,开始学习汇编语言学习资料是B站的视频:汇编语言程序设计 贺利坚主讲 (P25)这里写目录标题LOOP功能与格式一、LOOP指令实例二、LOOP指令执行的要求三、用LOOP指令

2022-01-18 08:30:55 4

4

4

4verilog语言的可综合性和仿真特性

综合就是将HDL语言转化成与,非,或门等等基本逻辑单元组成的门级连接。因此,可综合语句就是能够通过EDA工具自动转化成硬件逻辑的语句。

2023-06-28 10:39:46 3474

3474

3474

3474动态电路中,零输入响应是仅由动态元件的初始贮能产生的响应对吗?

动态电路中,零输入响应是仅由动态元件的初始贮能产生的响应对吗? 在动态电路中,零输入响应指的是由于初始条件引起的响应,而与输入信号无关。它是仅由动态元件的初始贮能产生的响应。当输入信号为零时(也即

2023-11-21 15:22:32 1869

1869

1869

1869arduino如何停止loop循环

退出这个循环。本文将详细介绍如何在Arduino中停止loop循环。 在Arduino中,可以通过使用一个布尔变量或条件语句来实现停止loop循环的功能。下面我们将逐步讨论这些方法。 一、使用布尔变量停止loop循环 一种简单的方法是在loop循环的外部使用一个布尔变量来

2024-02-14 16:24:00 6724

6724

6724

6724动态无功补偿的三个必要条件

在现代电力系统中,电能的有效利用是保证经济发展的重要因素。然而,随着电力需求的增加和非线性负载的普遍出现,电力系统面临的挑战也日益严峻。动态无功补偿作为一种提高系统稳定性、改善电能质量的有效手段,其

2024-11-12 14:05:57 1026

1026

1026

1026

AN76-OPTI-LOOP架构可降低输出电容并改善瞬态响应

电子发烧友网站提供《AN76-OPTI-LOOP架构可降低输出电容并改善瞬态响应.pdf》资料免费下载

2025-01-08 13:54:35 0

0

0

0 电子发烧友App

电子发烧友App

评论