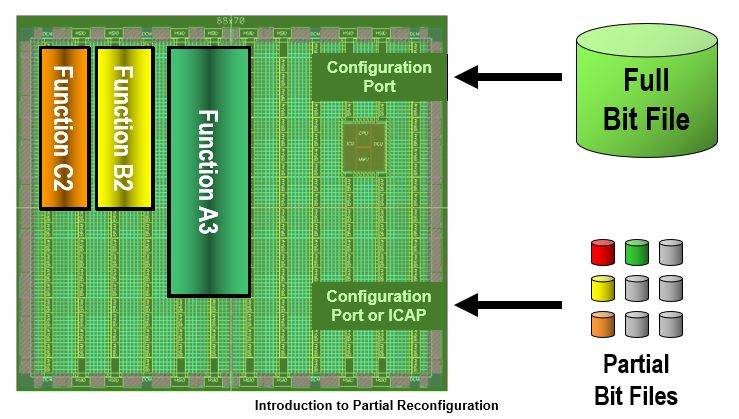

所谓FPGA动态可重构技术,就是要对基于SRAM编程技术的FPGA实现全部或部分逻辑资源的动态功能变换。根据实现重构的面积不同,动态可重构技术又可分为全局重构和局部重构。

1、何为局部动态可重构

局部动态可重构可以简单的理解为通过下载局部分区bit 文件来动态修改对应分区的逻辑功能,同时其余分区的逻辑功能持续运行而不中断。

2、局部动态可重构技术的优势

a、系统灵活性:可以在保持通信连接的同时执行更多的系统功能;

b、降低FPGA资源和成本:通过分时复用的方式降低FPGA硬件尺寸;

c、降低功耗:通过卸载掉暂时不用的局部逻辑的方式降低FPGA功耗;

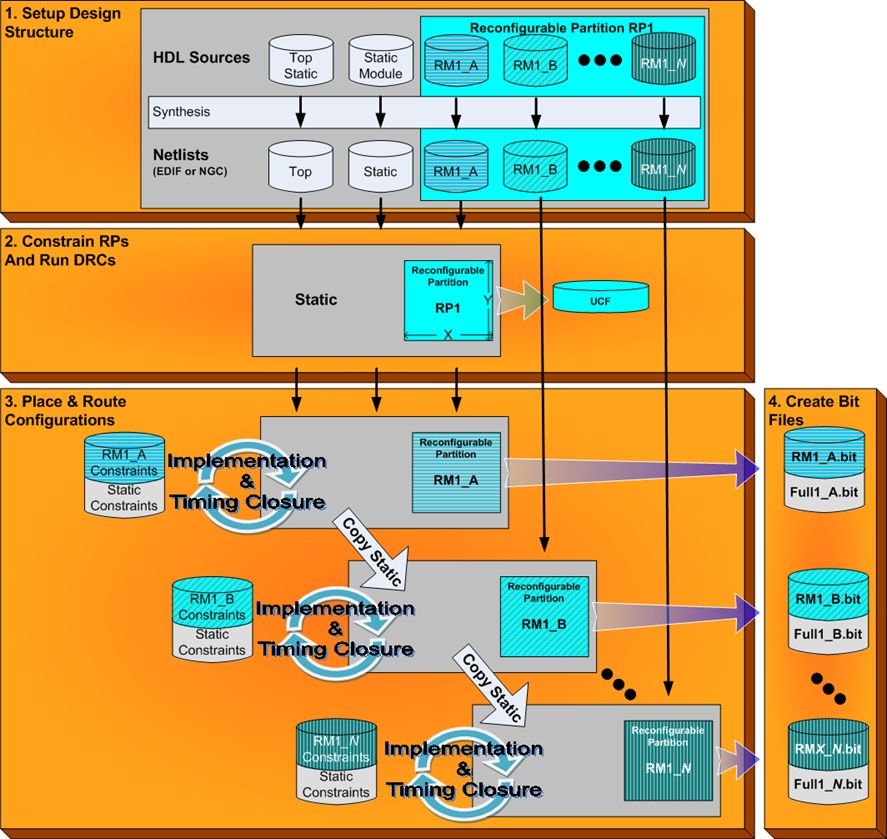

3、FPGA局部动态重构流程

a、规划系统整体框架和可重构模块框架,编写各模块HDL代码,综合生成各子模块网表文件;

b、规划分区以及给各分区分配足够资源,创建各分区及静态部分的时序约束文件,执行DRC检查;

c、对各分区进行布局布线配置;

d、遍历各种可能的配置,编译生成全局bit文件和可重构模块的局部bit文件。

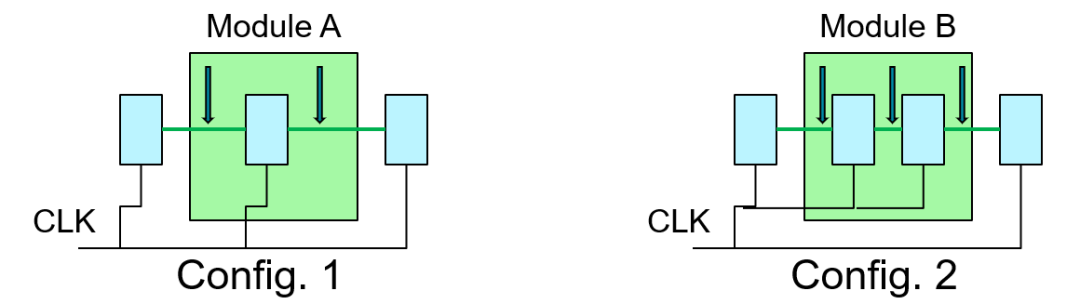

4、局部动态可重构的时序问题

如上图所示,局部重构会带来时序路径的变化,使得局部可重构工程的时序约束问题变得更加复杂。

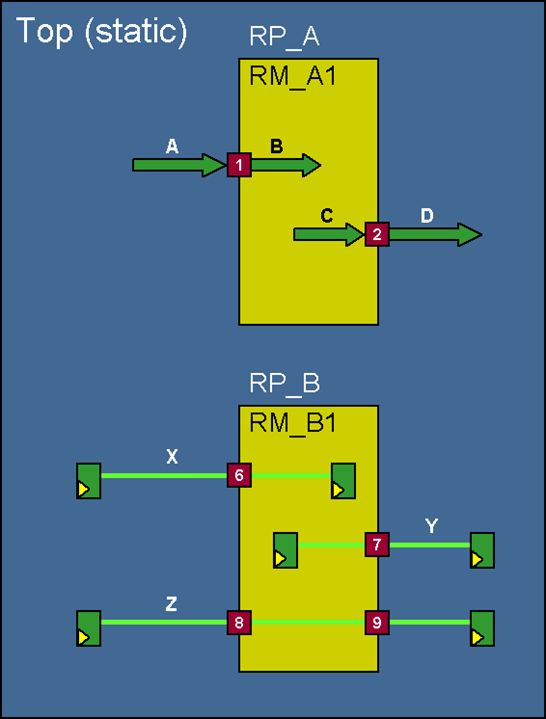

解决方法:在静态逻辑和可重构模块间的信号传递路径上添加代理逻辑点,如下图红色数字点,将单条时序路径分割为两个独立的部分,然后分别对两部分的路径进行单独约束,以达到时序要求。

文章出处:【微信公众号:OpenFPGA】

责任编辑:gt

-

FPGA

+关注

关注

1664文章

22503浏览量

639288 -

代码

+关注

关注

30文章

4976浏览量

74384

原文标题:浅析FPGA局部动态可重构技术

文章出处:【微信号:Open_FPGA,微信公众号:OpenFPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

智慧配电新标配:基于“动态拓扑重构”的固态变压器(SST)故障自愈实测研究

探索TRAC020LH:完全可重构模拟电路的卓越之选

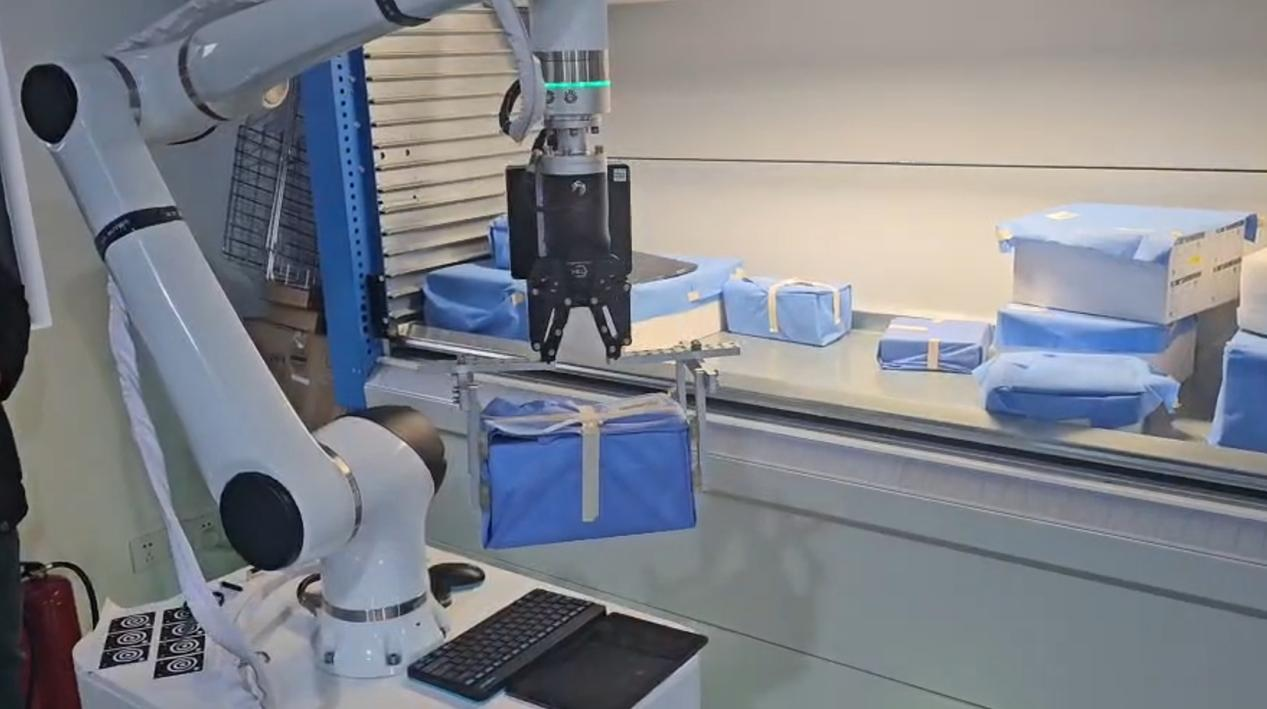

复合机器人可重构柔性装配 赋能智能制造产线全面升级

小型自重构机器人能不能帮忙做一个?

【OFDR】实时感知、动态重构与历史状态回溯!昊衡科技-三维场重构软件

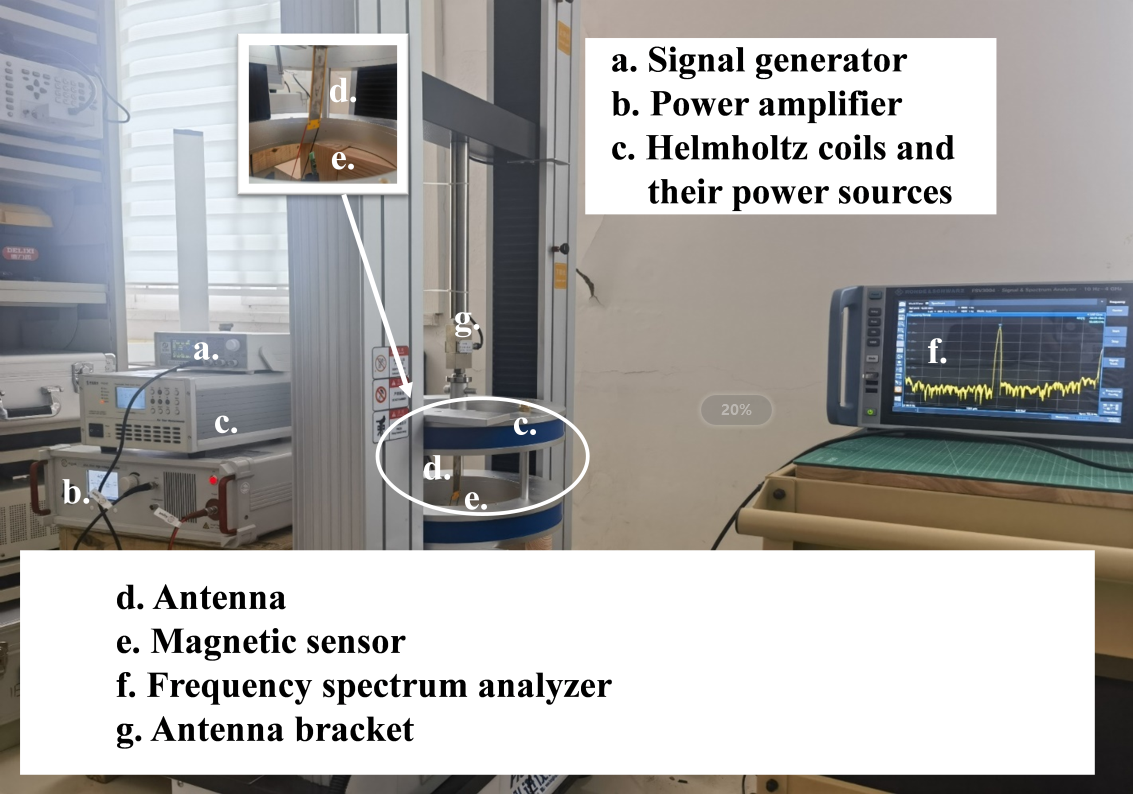

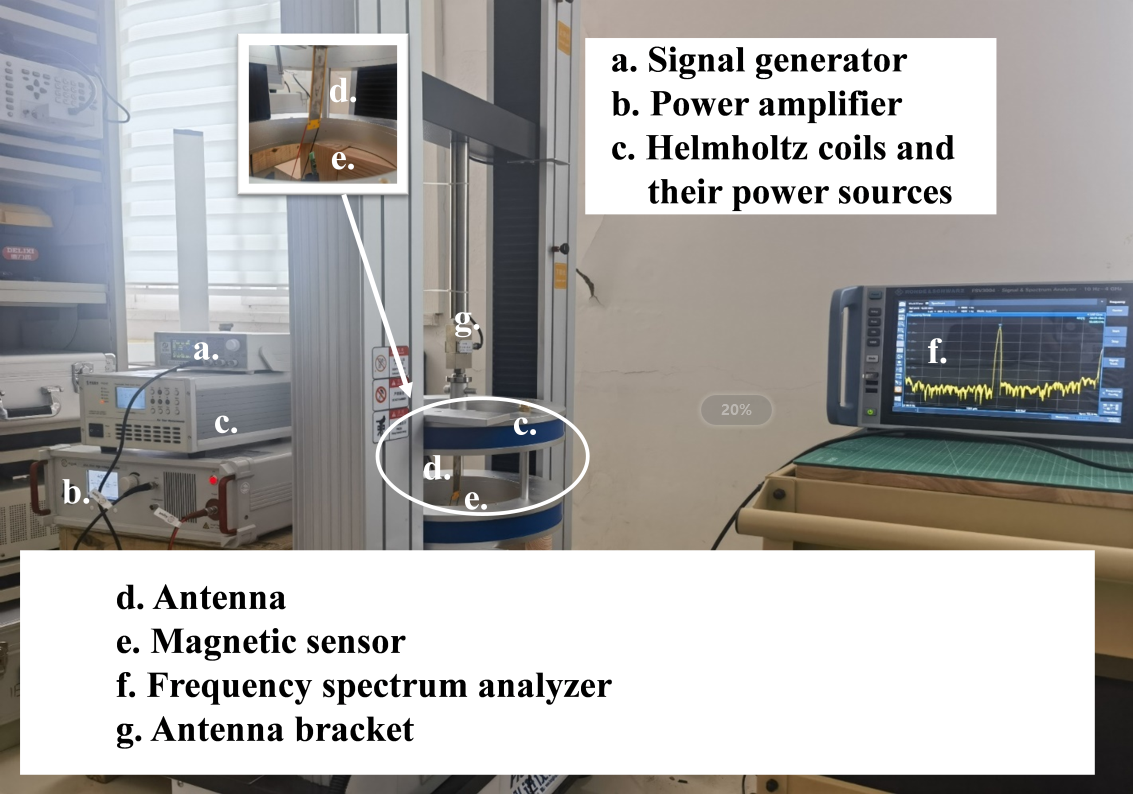

高压放大器在激励低频可重构磁电天线中的应用

AMD利用可重构FPGA设备Moku实现自定义激光探测解决方案

基于Moku的功率器件动态参数测试系统:精准、高效、经济的一体化测试方案

AES和SM4算法的可重构分析

ATA-7010高压放大器:开启低频可重构磁电天线激励的新篇章

PLL技术在FPGA中的动态调频与展频功能应用

清微智能官宣:国产可重构芯片全球出货量突破2000万颗

中科亿海微可重构智能超表面电磁单元控制方案:多维调控电磁波,助力6G无线中继

数字孪生热管理:NTC热敏电阻阵列与热场重构算法的动态适配

FPGA动态可重构技术是什么,局部动态可重构的时序问题解决方案

FPGA动态可重构技术是什么,局部动态可重构的时序问题解决方案

评论