PCI Express (PCIe)即将于2021年迎来6.0规范,意味着其数据传输速率将高达64GT每秒并采用PAM-4调制。有消息指出,铜互连线路虽然覆盖范围较小,但使用寿命更长。

PCI特别兴趣小组(SIG)正在为主流设计厂商提供PAM-4功能。目前,SerDes开发人员已经开始在56G以及更高速率的高端系统之上使用这项功能。着眼于最前沿,另一些组织已经开始研究112G规范,部分专家甚至表示200G铜链路也已经拥有了清晰的发展思路。

但困扰研究人员的永恒难题在于,链路速度越快,其传播距离也就越短。有说法称,通过采用更为昂贵的电路板印刷材料或者重新定时芯片能够有效缓解这类难题。而另一大考量因素,则是在采用PAM-4的同时需要配合正向纠错(FEC)块,但后者会提升延迟水平。

为了实现升级,系统设计师已经将目光转向服务器与网络设备内部的有线链路,希望避免因引入重新定时芯片或者优质电路板材料而带来的成本增长。SIG目前仍在争论其6.0规范的延迟设定,一位专家表示其至少需要与延迟仅为数十纳秒的DRAM相匹配。

PAM-4与FEC都是PCIe规范中的新产物,而在此前的规范当中,一直依赖于更为宽松的非归零(NRZ)技术。

SIG主席Al Yanes表示,“这项工作颇具挑战性。我们将从各个角度进行探索——包括材料、连接器等等,但这些都有其对应成本……问题的核心在于PHY以及模拟与误码率,但我们很幸运,因为我们的组织当中有着众多睿智的工程师人才。”

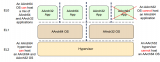

作为6.0规范,Gen6方案将需要向下兼容全部早期PCIe规范,以确保主板与网卡能够在不同的时间段内逐步完成演进。但Yanes也指出,提供一项帮助产品在NRZ与PAM-4方案之间转换的规范本身,同样会带来“成本负担”。

大型云计算服务供应商正是此次提速工作当中的重要驱动因素之一。SIG在上个月完成了32 GT每秒 Gen5规范,并已经开始为AI加速器、、数据中心处理器以及存储系统提供芯片产品。此外,在大型数据中心内掀起的由400 G到800 G的网络升级行动,也推动了市场对于快速互连方案的需求。

Yanes指出,“在我们与电气工作组就Gen6进行面对面讨论之前,我们先休息了一个月,因为现在的这一切都与PHY有关。”所谓PHY,也就是高度模拟化的物理层模块。

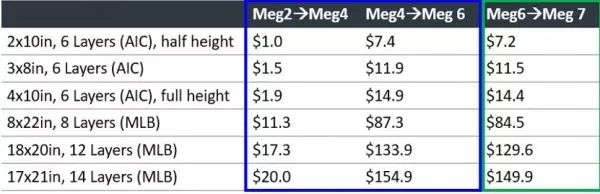

升级PC板材料的成本很高,Meg7可能要到明年或者更晚才能获得认证。

虽然PCIe与其它铜缆互连方案正在保持着高速发展,但未来的道路正变得愈发艰难。为了能够实现与前几代升级相同的提升效果,工程师们必须采用更好的电路板材料或者引入重新定时芯片——这两种方案通常都成本不菲。

在PCIe 1.0的时代,在主流FR4板上可发送的信号距离高达20英寸,甚至能够直接穿越两个连接器。而基于现有16 GT每秒PCIe 4.0规范的高端产品信号,可能在抵达一个连接器之前就已经消失。

从Gen4规范开始,由于设计多样化程度越来越高,SIG决定停止报告规范中所支持的信号传输距离。相反,新的规范以眼状图的形式为良好信号定义出高度与宽度。此外,新规范还提供关于信号丢失问题的粗略指导——Gen4为28 dB、Gen5为36 dB。预计Gen6还将具有类似的损耗,但具体定义尚未公布。

谈到对Gen6的预期,来自Keysight公司的一位SIG董事会成员表示,“我们还不清楚特定设计的串扰、连接器反映以及所使用的具体材料——目前还有太多未知因素。”

为了削减成本,各OEM厂商正越来越多地倾向利用短电缆对安装在系统之内多块小板上的组件进行连接。

HPE公司研究员Michael Krause在与合作伙伴们分享系统设计思路时表示,“举例来说,相较于设计一块与机箱等长的主板,我们完全可以在系统当中隔离出一个个很小的机械装置,其中只能容纳插槽与DIMM,并利用线缆跨越任意距离将其连接起来。目前已经有很多平台供应商都正在或者即将转向这种模块化设计方式。”

模块化服务器能够利用有线链路实现成本削减。

Kraus认为,OEM厂商需要对目前的几种小型电路板及连接器进行标准化,从而在提高产量的同时降低新方案的制造成本。他补充称,一部分标准化组织已经在对其外形进行定义。

Yanes指出,“我们在外部PCIe布线方面没能取得多少进展,但我听说有一些成员已经开始使用内部布线方案——其实二十年之前,人们普遍认为布线是一种差劲的解决方式。”

在年度SIG大会上,不少IP与测试供应商都展示了自己的Gen4与Gen5设计演示方案。Synopsys公司的工程师表示,该公司拥有160份Gen4 IP许可,匮包括来自初创企业Habana的AI加速器。

在年度SIG大会上,Marvell公司的一支IP小组展示了x4 Gen5测试模块的工作演示,未来其有可能成为固态硬盘控制器的一部分。英特尔方面也表示,其将在2021年支持Gen5处理器。

Synopsys公司的一位工程师指出,目前已经有多家客户在实际芯片与产品当中使用Gen5 IP,而且主要集中在16纳米及以下的高端产品当中。PLDA描述了其面向两台桥接交换机销售的Gen5 IP,且计划在今年4月之前投入实际使用。

-

芯片

+关注

关注

463文章

54416浏览量

469206 -

pcb

+关注

关注

4417文章

23963浏览量

426108 -

数据传输

+关注

关注

9文章

2226浏览量

67730 -

PCIe

+关注

关注

16文章

1477浏览量

88914

原文标题:PCIe正在为64G跃升进行筹备

文章出处:【微信号:cunchujie,微信公众号:存储界】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

【PCIe 6.0 连载 · 下篇】测试才是关键:PCIe 6.0 如何保证稳定量产?(行业干货)

【PCIe 6.0 连载 · 上篇】64GT/s 时代来临:AI与算力爆发下的高速互联新基石

【PCIE732】光纤卡,具备PCIe接口的万兆光纤卡

基于成都华微ADC芯片HWD08B64G的高端示波器应用方案

【PCIE736】基于 PCIE X16 总线架构 4 路 QSFP28 100G 光纤通道处理平台(基于 VU3P FPGA)

华为马亮分享AI时代体验跃升的网络发展蓝图

Amphenol PCIe® Gen 6 Mini Cool Edge IO连接器:下一代高速互连解决方案

瑞萨 Titan board RA8P1 sdcard demo例程识别64G、256G exfat的SD卡挂载失败的原因?

求 CS32G020移动电源EVB用户使用指南 中的清晰原理图

这个接口没有自己想要的5G模组?别急!启明智显5G CPE主板已经实现PCIe/USB模组通吃了!

PCIe正在为64G跃升进行筹备 已经拥有清晰的发展思路

PCIe正在为64G跃升进行筹备 已经拥有清晰的发展思路

评论