在当今飞速发展的电子设计领域,高速化和小型化已经成为设计的必然趋势。与此同时,信号频率的提高、电路板的尺寸变小、布线密度加大、板层数增多而导致的层间厚度减小等因素,则会引起各种信号完整性问题。因此,在进行高速板级设计的时候就必须考虑到信号完整性问题,掌握信号完整性理论,进而指导和验证高速PCB的设计。在所有的信号完整性问题中,串扰现象是非常普遍的。串扰可能出现在芯片内部,也可能出现在电路板、连接器、芯片封装以及线缆上。本文将剖析在高速PCB板设计中信号串扰的产生原因,以及抑制和改善的方法。

串扰的产生

串扰是指信号在传输通道上传输时,因电磁耦合而对相邻传输线产生的影响。过大的串扰可能引起电路的误触发,导致系统无法正常工作。

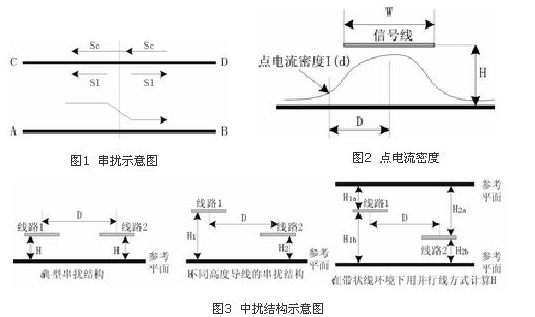

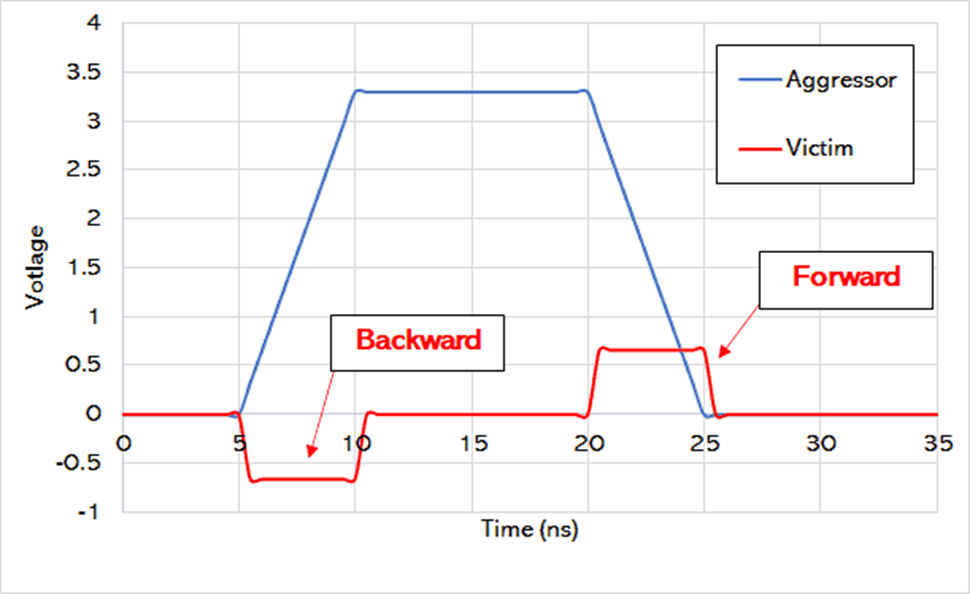

如图1所示,变化的信号(如阶跃信号)沿传输线由A到B传播,传输线C到D上会产生耦合信号。当变化的信号恢复到稳定的直流电平时,耦合信号也就不存在了。因此串扰仅发生在信号跳变的过程当中,并且信号变化得越快,产生的串扰也就越大。串扰可以分为容性耦合串扰(由于干扰源的电压变化,在被干扰对象上引起感应电流从而导致电磁干扰)和感性耦合串扰(由于干扰源的电流变化,在被干扰对象上引起感应电压从而导致电磁干扰)。其中,由耦合电容产生的串扰信号在受害网络上可以分成前向串扰和反向串扰Sc,这两个信号极性相同;由耦合电感产生的串扰信号也分成前向串扰和反向串扰Sl,这两个信号极性相反。

互容和互感都与串扰有关,但需要区别考虑。当返回路径是很宽的均匀平面时,如电路板上的大多数耦合传输线,容性耦合电流和感性耦合电流量大致相同。这时要精确地预测二者的串扰量。如果并行信号的介质是固定的,即带状线的情况,那么,耦合电感和电容引起的前向串扰大致相等,相互抵消,因此只要考虑反向串扰即可。如果并行信号的介质不是固定的,即微带线的情况,耦合电感引起的前向串扰随着并行长度的增大要大于耦合电容引起的前向串扰,因此内层并行信号的串扰要比表层并行信号的串扰小。

串扰的分析与抑制

高速PCB设计的整个过程包括了电路设计、芯片选择、原理图设计、PCB布局布线等步骤,设计时需要在不同的步骤里发现串扰并采取办法来抑制它,以达到减小干扰的目的。

串扰的计算

串扰的计算是非常困难的,影响串扰信号幅度有3个主要因素:走线间的耦合程度、走线的间距和走线的端接。在前向和返回路径上沿微带线走线的电流分布如图2所示。在走线和平面间(或走线和走线之间)的电流分布是共阻抗的,这将导致因电流扩散而产生的互耦,峰值电流密度位于走线的中心正下方并从走线的两边向地面快速衰减。

当走线与平面间的距离间隔很远时,前向和返回路径间的环路面积增加,使得与环路面积成比例的电路电感增加。下式描述了使前向和返回电流路径构成的整个环路电感最小化的最优电流分布。它所描述的电流也使存储在信号走线周围磁场内的总能量最小。

式中i(d)是信号电流密度,I0是总体电流,H是走线距地层的高度,D是距走线中心线的距离。

各种串扰结构的示意图如图3所示,因为位置的不同所以结果也有所不同。图3a所示为同层传输线之间的情况,

串扰表示为被测噪声电压与驱动信号的比。常数K依赖于电流上升时间及干扰走线的长度,这个值总是小于1,在大多数情况下,近似取1。加大并行信号之间的间距或者减小信号与平面层之间的距离都有助于减小同层信号之间的串扰。 对于距离介质高度不同的微带线,如图3b所示,

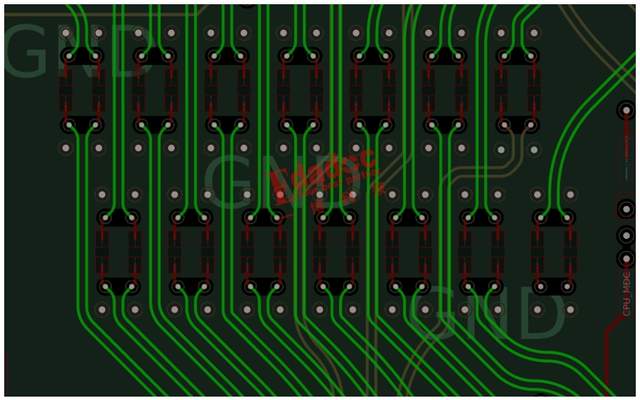

对于处于不同层的带状线,如图3c所示,使用对两个参考层高度的并联来决定, ,然后再用上面的公式计算得到。由以上各式可看出,避免或最小化平行线间串扰的最好方法是最大化走线间隔或使走线更接近参考层。长时钟信号和高速并行总线信号的布线应该遵循这一规则。

,然后再用上面的公式计算得到。由以上各式可看出,避免或最小化平行线间串扰的最好方法是最大化走线间隔或使走线更接近参考层。长时钟信号和高速并行总线信号的布线应该遵循这一规则。

******************************************************************

更多内容:高速PCB板设计中的串扰问题和抑制方法 (下)

-

PCB设计

+关注

关注

396文章

4907浏览量

94131 -

华强PCB

+关注

关注

8文章

1831浏览量

29134 -

华强pcb线路板打样

+关注

关注

5文章

14629浏览量

44396

发布评论请先 登录

EXCUSE ME,表层的AC耦合电容和PCB内层的高速线会有串扰?

隔离地过孔要放哪里,才能最有效减少高速信号过孔串扰?

SiC MOSFET并联均流及串扰抑制驱动电路的研究

埋孔技术在PCB多层板中的应用案例

高速PCB板设计中的串扰问题怎样解决

高速PCB板设计中的串扰问题怎样解决

评论