随着冠心病日益严重,在治疗过程中,先要正确找出冠状动脉堵塞位置,然后才能对症下药。

因此,集合超声显像和导管技术的血管内超声导管,可以通过血管超声成像来检查诊断冠状动脉、外周血管等管腔内血液和血管壁病患,成为越来越受欢迎的诊断工具。

客户D看中了这个商机,但在量产血管内超声导管时,始终没法达到理想的良率,妨碍公司大规模生产的计划。客户D决定与环球仪器APL合作,对现行生产工序进行检查,并加以优化。

APL在进行产品失效分析后,给客户D开发了一条包含印刷机、贴片机、回流炉等等设备的生产线。

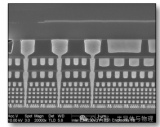

血管内超声导管堪称是全世界最微小间距焊合的倒装芯片互连,APL的解决方案如下:

采用仅有12μm厚的柔性PI基底层

使用PZT焊盘、吸嘴

锡球只有22μm高、25μm直径(人类头发才~80μm)

在75μm间距的倒装芯片上放置多个倒装晶片

22μm高、25μm直径的锡球放在

75μm间距的倒装芯片上

客户在采用APL的工艺流程后,在12个月内,将产品良率提升至99+%,因而加快了产品的生产速度,市场占有率持续上升,最终成为全球最大供应商。客户jkxs后不单把公司上市,更以高价出售。

APL设备齐全

APL之所以能确保为客户开发工艺流程,并确保切实可行,皆因APL拥有一条完整的SMT生产线,并全备的检测工具,能在实验室试行整个生产过程。

1SMT生产线10台设备包括:

DEK丝网印刷机

环球仪器的贴片机

Vitronic Soltec压迫热对流回流炉

Asymtek底部填充点胶

CyberOptics自动视觉检查

Metcal返修台

2产品检测13台设备包括:

Dage XD7600 X光系统

Kohyoung Zenith 检测系统

Cyber Optics SE500 3D 锡膏厚度测试仪

Leica光学显微镜

Philips扫描电子显微镜 w/EDS

CyberOptics激光轮廓仪

Metcal光学检测系统

-

芯片

+关注

关注

463文章

54389浏览量

469047 -

smt

+关注

关注

45文章

3211浏览量

77026 -

APl

+关注

关注

0文章

8浏览量

8219

原文标题:要挑战全球最微细间距的倒装芯片互连?环球仪器APL做得到。

文章出处:【微信号:UIC_Asia,微信公众号:环仪精密设备制造上海】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

用于3D集成的精细节距Cu/Sn微凸点倒装芯片互连工艺研究

0.25mm超微间距连接器:智能穿戴设备高密度互连与信号完整性的技术挑战

超细间距倒装芯片灌封胶渗透与空洞控制 |铬锐特实业

从内存接口到PCIe/CXL、以太网及光互连,高速互连芯片市场分析

环球仪器EPIQx新一代智能高速贴片机的创新亮点

TE推出的AMPMODU互连系统有何特点?赫联电子怎么样?

环球仪器助力mPower公司扩大太空级太阳能组件产能

SGTOOLS为什么这些功能是灰色的,没法用?

TE推出AMPMODU互连系统具有哪些产品特性?-赫联电子

XSR芯片间互连技术的定义和优势

要挑战全球最微细间距的倒装芯片互连?环球仪器APL做得到

要挑战全球最微细间距的倒装芯片互连?环球仪器APL做得到

评论