微控制器(MCU)多年来一直致力于低端,数字信号处理(DSP)中心应用,数字信号控制器(DSC)中的硬件乘法累加(MAC)单元极大地扩展了DSP功能。尽管如此,集成外设和存储器的MCU仍远低于专用的DSP中心处理器和微处理器所提供的性能水平,这些处理器和微处理器也集成了辅助DSP内核。然而,德州仪器(TI)和恩智浦半导体等供应商提供的多核MCU产品的性能差距正在缩小。让我们探讨面向DSP挑战的嵌入式设计人员的最新选择,但也面临系统占用和功耗问题,这通常会导致基于MCU的方法。

MCU中强大的以DSP为中心的功能可以追溯到十年前推出的第一款DSC。 Microchip推出了dsPIC30系列,结合了16位PIC24 MCU和硬件乘法累加(MAC)功能以及其他以DSP为中心的功能(如桶形移位器),从而创造了DSC术语。 TI以不同的方式接触该部门,利用其DSP核心传统的处理器技术,并将其集成到具有C2000系列内存和外设的MCU架构中。

多核MCU

上面提到的DSC架构是基于MCU或DSP遗留的单核设计。然而,最新的TI和NXP以DSP为中心的产品是真正的多核设计。每种情况下的意图是将核心专用于最适合的任务。

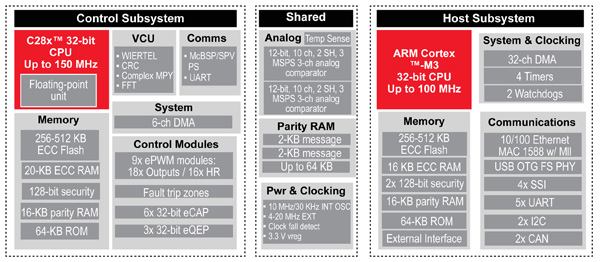

TI新的Concerto系列如XF28M35H52C1RFPT结合了C28x以DSP为中心的内核,包括浮点单元(FPU),它基本上是从TMS320F283x Delfino MCU系列演变而来的,该系列采用ARM Cortex-M3 RISC内核已用于Stellaris MCU系列。实际上,使用Concerto的设计人员将两个MCU合二为一,如框图所示(图1)。每个内核都有自己专用的内存和外设。还有一块共享资源,支持电源时钟和时钟分配,以及处理器间通信,并实现基本的模拟外设。

图1:TI的Concerto MCU包括独立的RISC和以DSP为中心的内核,每个内核都有一组专用的外设和内存资源。

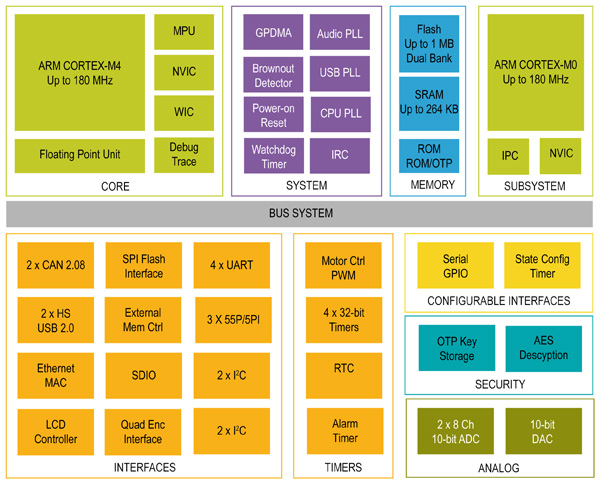

恩智浦在图2所示的LPC43xx MCU系列中采用了略微不同的方法。对于初学者来说,两个CPU都基于ARM内核。该系列不使用核心相同的同构多核方法。相反,DSP功能集中在Cortex-M4内核中,包括MAC,SIMD(单指令多数据)执行单元和FPU。同时,Cortex-M0内核是ARM为MCU提供的基准32位RISC产品。恩智浦架构提供了一组由内核共享的内存和外设功能,尽管设计可以将特定内存块和外设专用于单个内核。

从编程角度来看,嵌入式设计人员面临着TI和NXP多核MCU面临的不同挑战。在NXP的情况下,除了只有Cortex-M4支持数学指令外,内核在指令集方面基本兼容。这应该简化应用程序开发以及将任务分配到两个核心的过程。

图2:恩智浦在LPC43xx中结合了ARM-Cortex-M0和-M4核心系列,内核共享一组内存和外设资源。

在Concerto的情况下,核心具有完全不同的指令集。但TI表示,其开发工具可以缓解异构内核引入的任何复杂问题。该公司为两个内核提供ControlSUITE集成开发环境(IDE)版本,为开发团队提供统一的开发窗口。编程通常使用高级语言完成,ControlSUITE支持双核调试功能。有关详细信息,请在Digi-Key网站上查看ControlSUITE产品培训模块。

控制任务消耗DSC

当然,问我们为什么需要具有两个内核的MCU这一问题是公平的。 MCU部分与通用微处理器部分非常不同。在后者中,多个同构核既加速了多线程应用,又提高了单个微处理器的聚合处理能力。

在MCU的情况下,应用程序的实时控制环处理要求通常决定了处理器的选择,并且这种控制环路通常不能分布在多个内核上。多核MCU通常将以DSP为中心的核心专用于控制环路和通用核心系统管理任务。

当然有许多已部署的示例,其中传统DSC处理控制循环处理,同时还处理系统管理功能和通信接口。然而,TI表示,其C2000 DSC的大量用户群将IC与通用MCU相结合。做出这个决定是因为系统管理任务会限制DSC可以处理实时控制的保真度。

让我们考虑一个例子来说明需要两个核心以及突出显示其他一些Concerto功能。 Concerto MCU中的C28x内核擅长电机控制等任务。高分辨率PWM外设支持该应用。同时,一些电机控制应用还需要专门的通信,例如电力线调制解调器。 Cortex-M3 CPU可以处理高级通信功能,但需要C28x内核来处理调制解调器功能。电机控制和调制解调器算法的结合将禁止C28x内核充当系统管理器。

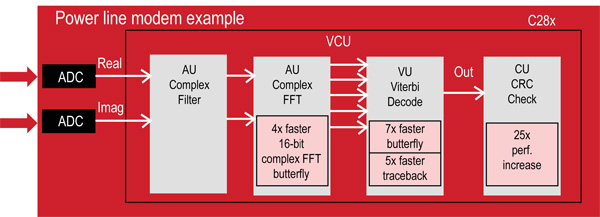

Concerto中使用的C28x内核包括一个称为VCU(Viterbi数学复合单元)的硬件模块,TI也在其他一些最近发布的C2000 MCU上提供了该模块。图3描绘了可能在电力线调制解调器中使用的维特比解码链。在VCU上实现该算法导致的性能比使用C28x上的软件实现可实现的性能高25倍。事实证明,双核设计不仅能够实现无法在单核设备中实现的应用,还能够支持以前可能需要更高端微处理器和DSP处理器组合的应用。

图3:对于以通信为中心的应用,如电力线调制解调器,Concerto集成了VCU(Viterbi数学复合单元),以加速维特比解码器等应用。

确实,支持多核的MCU的不断发展的功能将支持新的应用类,并为设计团队带来新的挑战。电力线通信等应用非常复杂。 TI通过DSP内核库和更高级别的应用程序库提供帮助。例如,该公司提供用于电机控制,数字电源控制,电力线通信和其他功能的应用程序库。

TI还提供了一种既定的方法,可以提供开发工具和套件,使设计团队能够轻松地尝试新的基于C2000的MCU。该公司为C2000系列中的每个MCU提供所谓的ControlCARD。 ControlCARD托管处理器,并通过标准化连接器访问所有MCU信号。设计团队可以使用ControlCARD连接器开发单个应用板,并评估目标应用中的许多C2000 MCU。 TI还提供结合了ControlCARD和通用基板的实验套件。对于协奏曲,TI提供TMDXCNCDH52C1 ControlCARD和TMDXDOCKH52C1实验套件。

结论

下次遇到性能密集型设计挑战时,请确保考虑集成多个内核的MCU的新兴趋势。正如摩尔定律推动微处理器部门采用混合均匀和异构核心的产品一样,这一趋势肯定会升级。在MCU领域,您可以期待专注于针对应用程序特定元素的内核的设计。对于TI和NXP,您将获得一个RISC核心,它擅长作为系统管理器和以DSP为中心的核心来处理粒度控制环路和实时响应。编程此类设备可能比您最初预期的要简单。

-

dsp

+关注

关注

561文章

8275浏览量

368276 -

mcu

+关注

关注

147文章

19128浏览量

403983 -

调制解调器

+关注

关注

3文章

887浏览量

41151

发布评论请先 登录

客户案例 | 国创灵梭 IntarkDB 助力创维装备从“经验驱动”向“数据驱动”跃迁

SQPI PSRAM为单片机提供RAM扩展方案

解析Linux的进程、线程和协程

Altera全新推出MAX 10 FPGA封装新选择

英飞凌推出专为高功率与计算密集型应用而设计的400V和440V MOSFET

AS32S601型MCU芯片在商业卫星电源系统伺服控制器中的性能分析与应用解析

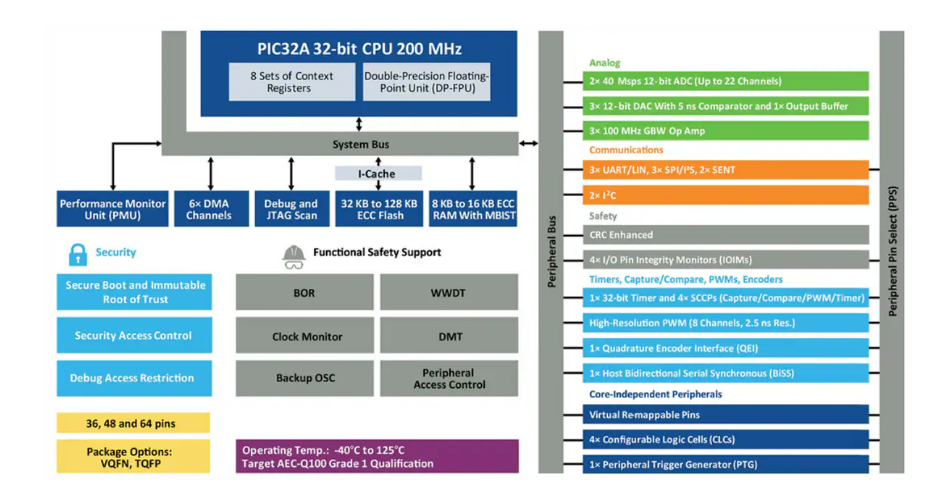

PIC32AK1216/GC41064:高性能32位MCU,集成FPU与高速ADC,面向电机控制与实时处理

永磁同步电机高性能控制系统研究

I/O密集型任务开发指导

CPU密集型任务开发指导

TaskPool和Worker的对比分析

借助NVIDIA技术实现机器人装配和接触密集型操作

睿擎多核 SMP 开发:极简开发,超强性能——睿擎派开发板0元试用

采用多核MCU实现性能密集型应用设计

采用多核MCU实现性能密集型应用设计

评论