本视频介绍了使用IP Integrator(IPI)创建简单硬件设计的过程。 使用IPI可以无缝,快速地实现DDR4和PCIe等块 连接在一起,在几分钟内创建硬件设计。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

赛灵思

+关注

关注

33文章

1797浏览量

133132 -

IP

+关注

关注

5文章

1849浏览量

154890 -

PCIe

+关注

关注

16文章

1420浏览量

87527

发布评论请先 登录

相关推荐

热点推荐

复杂的软件算法硬件IP核的实现

硬件加速 IP 核 HDL 文件的生成分为两个步骤,首先根据将要接入的 SOPC 系统的总线的特性,将算法做适当的包装、暴露相关的接口以及调用方法,即适配总线接口。不同的 SOPC 总线有不同的时序以及

发表于 10-30 07:02

安防硬件设备中的防水防尘IP等级代表什么?IP66是什么水平

我们在选择安防硬件厂家的产品时,在规格表或产品详情页中常常会看到一个防护等级的指标,有的是IP65.有的是IP66等级,这些安防设备产品的IP等级高低又分别代表什么呢?下面让天波小编为

AMD Vivado IP integrator的基本功能特性

我们还将带您了解在 AMD Zynq UltraScale+ MPSoC 开发板与 AMD Versal 自适应 SoC 开发板上使用 IP integrator 时,两种设计流程之间存在的差异。

FPGA利用DMA IP核实现ADC数据采集

DMA IP核来实现高效数据传输的步骤,包括创建项目、配置ADC接口、添加和连接DMA IP核、设计控制逻辑、生成比特流、软件开发及系统集成。文章还强调了系统实现中不可或缺的ip_re

MicroBlaze处理器嵌入式设计用户指南

*本指南内容涵盖了在嵌入式设计中使用 MicroBlaze 处理器、含存储器 IP 核的设计、IP integrator 中的复位和时钟拓扑结构。获取完整版《 MicroBlaze 处理器嵌入式设计用户指南》,请至文末扫描二维码

如何在Unified IDE中创建视觉库HLS组件

Vivado IP 流程(Vitis Unified),在这篇 AMD Vitis HLS 系列 3 中,我们将介绍如何使用 Unified IDE 创建 HLS 组件。这里采用“自下而上”的流程,从 HLS

如何使用AMD Vitis HLS创建HLS IP

本文逐步演示了如何使用 AMD Vitis HLS 来创建一个 HLS IP,通过 AXI4 接口从存储器读取数据、执行简单的数学运算,然后将数据写回存储器。接着会在 AMD Vivado Design Suite 设计中使用此 HLS

Xilinx Shift RAM IP概述和主要功能

Xilinx Shift RAM IP 是 AMD Xilinx 提供的一个 LogiCORE IP 核,用于在 FPGA 中实现高效的移位寄存器(Shift Register)。该 IP 核利用

AI应用激增,硬件安全防护更关键,Rambus 发布CryptoManager安全IP解决方案

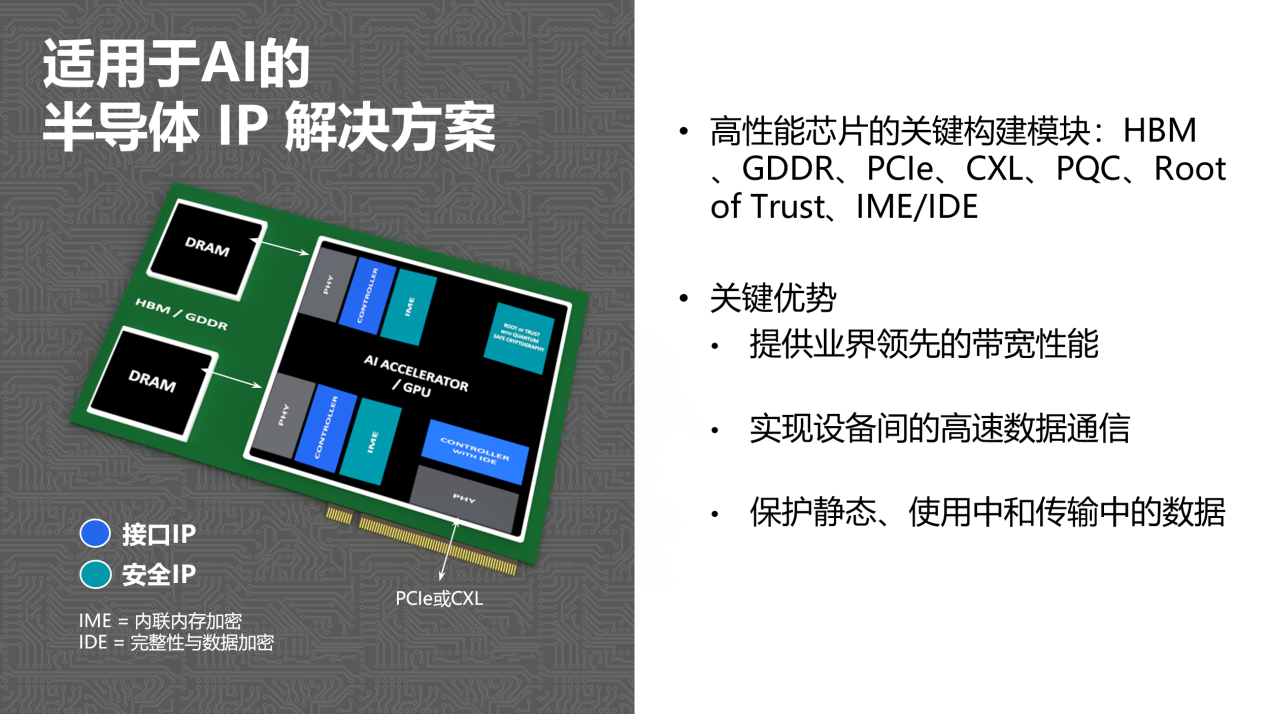

知名半导体IP和芯片供应商Rambus以创新为基础打造三大半导体解决方案,包括基础技术、半导体IP和芯片。基础技术方面,35年以来公司开发了约2700项专利。半导体IP方面,提供接口IP

RT-Thread Ethernet/IP 协议技术实践|技术集结

工业设备之间的实时通信。由于Ethernet/IP兼容现有的以太网硬件和网络,企业能够在不需要专用硬件的情况下,实现工业设备间的互联互通,提升生产效率和系统可靠性

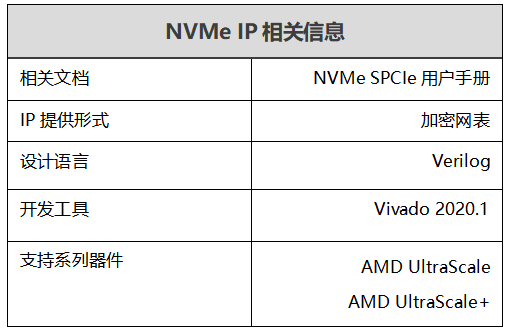

ALINX NVME SPCle IP 特性详解

。 NVMe SPCle IP 正是为这样的场景量身定制。通过结合 PCIe 软核 IP 与 NVMe 主机控制器,让开发人员 在无硬核的情况下,也能轻松接入 NVMe SSD ,突破了传统存储方案的硬件限制。 简单来说, NV

如何理解芯片设计中的IP

本文主要介绍如何理解芯片设计中的IP 在芯片设计中,IP(知识产权核心,Intellectual Property Core)是指在芯片设计中采用的、已经开发好的功能模块、设计或技术,它可以是硬件

检测电流最大为1mA,最小为20pA,如此该如何设置DDC112?

1. IN1中有Integrator A,Integrator B, IN2中也有Integrator A和Integrator B, A,B该如何处理?可否只使用其中一个?

2.

发表于 01-16 06:06

Altera JESD204B IP核和TI DAC37J84硬件检查报告

电子发烧友网站提供《Altera JESD204B IP核和TI DAC37J84硬件检查报告.pdf》资料免费下载

发表于 12-10 14:53

•0次下载

如何使用IP Integrator创建硬件设计

如何使用IP Integrator创建硬件设计

评论