Xilinx System Generator™for DSP是Simulink的一个插件,使设计人员能够为Xilinx FPGA开发高性能DSP系统。设计人员可以使用MATLAB,Simulink和Xilinx bit / cycle-true模型库来设计和仿真系统。然后,该工具将自动生成映射到Xilinx预优化算法的可综合硬件描述语言(HDL)代码。然后可以合成此HDL设计,以便在Xilinx FPGA和All Programmable SoC上实现。因此,设计人员可以定义系统级设计的抽象表示,并轻松地将此单个源代码转换为门级表示。此外,它还提供自动生成HDL测试平台,可在实施时进行设计验证。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

dsp

+关注

关注

561文章

8275浏览量

368204 -

赛灵思

+关注

关注

33文章

1798浏览量

133646 -

HDL

+关注

关注

8文章

332浏览量

49041

发布评论请先 登录

相关推荐

热点推荐

关于OSIF_COUNTER_SYSTEM问题求解

在串口中使用OSIF_COUNTER_SYSTEM功能,使用这个功能之后是否是在串口接收到信息之后3ms内无后续数据即结束数据接收,那么我下面的初始化操作是否正确,在此请教大家,谢谢

发表于 03-20 08:28

Vector为科世达颁发ISO/SAE 21434汽车网络安全CSMS流程证书

System)流程证书。该证书的取得,意味着科世达已建立起完整且高质量的汽车网络安全CSMS流程,并具备在产品研发、生产、售后运维等全生命周期中高效落实网络安全管理的能力。科世达与Vector中国的相关代表共同参加了此次颁证仪

借助 AI 从流程可视化到流程优化的 6 个步骤

借助 Minitab Solution Center与 Simul8,将日常流程损耗转化为可量化的效能提升 生活各处都看到流程的影子,无论是逛杂货店、排队买咖啡,还是收拾行李准备度假。你是否曾发现

IBM Storage Scale System 6000焕新升级

没有数据的 AI 工厂就像没有燃料的引擎,根本无法运转。IBM Storage Scale System 6000 的全局命名空间和 Active File Management (AFM) 功能

DSP的基础

高速数字信号处理技术是以DSP为核心,具有高速,实时的特点的一种信息处理技术。其本质是信息的变换和提取。DSP(Digital Signal Processor),即数字信号处理器,是一种专用

发表于 11-20 06:35

【技术分享】正确编写SysV Init脚本以实现Systemd兼容(上)

嵌入式的ubuntu系统如何写好SysVInit脚本呢?与system服务又有什么差别呢?一起随着文章来探究吧。问题背景许多传统Linux服务仍使用SysVInit脚本(/etc/init.d

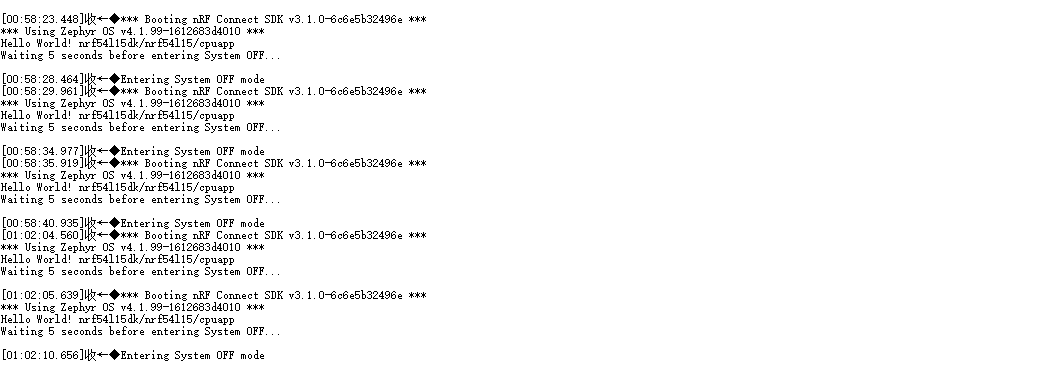

【NCS随笔】如何进入system_off深度睡眠模式以及配置GPIO中断唤醒

【NCS随笔】如何进入system_off深度睡眠模式以及配置GPIO中断唤醒 本文章主要是讲解NCS下面使用nRF54L15如何进入system_off模式,以及如何配置通过按键唤醒 一、如何进

DSP芯片与800G光模块的核心关系:Transmit Retimed DSP、LPO与LRO方案的探讨

本文深入探讨DSP芯片在800G光模块中的核心作用,包括Transmit Retimed DSP架构与新兴LPO/LRO方案的对比分析。DSP在信号均衡、误码控制与长距离传输中不可或缺,而LPO/LRO以低功耗优势适用于短距互联

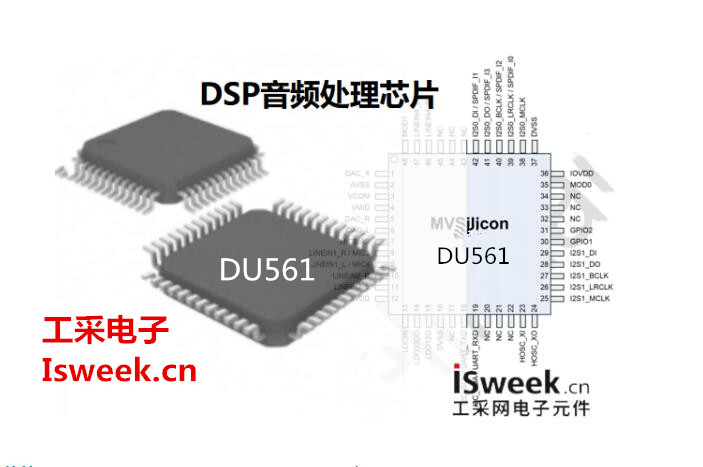

音频DSP设计与应用

DSP(即数字信号处理器)对于音频处理技术至关重要。

新唐DSP集成了Waves(Maxx音频),DSP 算法的全球领导者。这包括专用的扬声器校准算法和心理声学算法。此外,它还具有强大的音频算法

发表于 09-05 07:45

一文看懂芯片的设计流程

引言:前段时间给大家做了芯片设计的知识铺垫(关于芯片设计的一些基本知识),今天这篇,我们正式介绍芯片设计的具体流程。芯片分为数字芯片、模拟芯片、数模混合芯片等多种类别。不同类别的设计流程也存在一些

深度剖析 RT-Thread 线程调度流程

RT-Thread调度第一个线程的主要流程分如下:rtthread_startup:RTT的启动函数,主要负责板级驱动,调度器,系统线程初始化,启动调度的工作

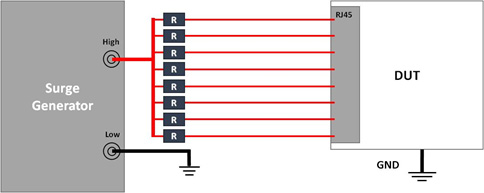

“System Level EOS Testing Method”可以翻译为: “系统级电性过应力测试方法”

“System Level EOS Testing Method”可以翻译为:

“系统级电性过应力测试方法”

智多晶FIFO_Generator IP介绍

FIFO_Generator是智多晶设计的一款通用型FIFO IP。当前发布的FIFO_Generator IP是2.0版本,相比之前的1.1版本主要新增了非等比输入输出数据位宽支持和异步FIFO跨时钟级数配置功能。

System Generator for DSP的设计流程

System Generator for DSP的设计流程

评论