了解如何使用BootGen为Zynq-7000 All Programmable SoC构建完整的映像。 引导映像通常包括第一级引导加载程序,至少一个软件应用程序和PL的比特流。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

赛灵思

+关注

关注

33文章

1798浏览量

133699 -

soc

+关注

关注

40文章

4638浏览量

230360 -

程序

+关注

关注

117文章

3849浏览量

85518

发布评论请先 登录

相关推荐

热点推荐

为什么无法在 i.MX93 平台上构建映像?

我尝试使用以下命令为 i.MX93 平台构建 Scarthgap 映像:

比特贝克 imx-image-multimedia

但是,构建失败并出现以下错误:

错误:_exec_cmd:

发表于 04-30 06:51

无法获得在 StarFive 上运行的 StarFive Linux 映像的 55 或 69 版本,怎么解决?

刷新固件VisionFive 2 Debian 镜像发布 -,它有效,但我仍然无法启动到 55 或 69 映像。我唯一可以启动的镜像是构建根镜像。

发表于 03-20 07:39

XC7Z020-2CLG484I 双核异构架构 全能型 SoC

Zynq-7000 系列的核心型号,创新性地将双核 ARM Cortex-A9 处理器与 7 系列 FPGA 可编程逻辑深度集成,构建起 “软件可编程 + 硬件可定制” 的异构计算架构,为多领域智能设备提供了一体化

发表于 02-28 23:37

如何在Zynq UltraScale+ MPSoC平台上通过JTAG启动嵌入式Linux镜像

在之前文章中,我们介绍了如何使用 XSCT 工具通过 JTAG 在 Zynq SoC 上启动嵌入式 Linux 镜像(从 JTAG 启动 Zynq-7000 嵌入式 Linux:使用 XSCT 全

深入剖析AP61200/AP61201/AP61202/AP61203同步降压转换器

61203.pdf 一、产品概述 AP61200/AP61201/AP61202/AP61203是一款输入电压范围为2.3V至5.5V、输出

具备物联融合能力的WAPI室内AP构建未来仓储神经末梢

,成为构建部队仓储坚固无线专网的关键节点。 一、军工级可靠性,适应复杂严苛仓储环境 部队仓储环境多样,从恒温恒湿的精密仪器库到空间开阔的普通物资库,温湿度条件差异巨大,且要求设备能够长期稳定运行。 此款AP采用工业级设计,具备

【VPX650 】青翼凌云科技基于 VPX 系统架构的 VU13P FPGA+ZYNQ SOC 超宽带信号处理平台

系列 FPGA(XCVU13P)作为主处理器,完成复杂的数 据采集、回放以及数据预处理。采用 1 片 ZYNQ SOC 来完成信号处 理算法。

Zynq7100 BSP移植,MSH终端不能正确显示是为什么?

由于新版本的RT Thread的BSP不再提供Zynq7000的支持。所以同事从RT Thread(4.0.3)中的Zynq7000移植了一份Zynq 7100的BSP。但是MSH终端和串口输出

发表于 09-19 06:26

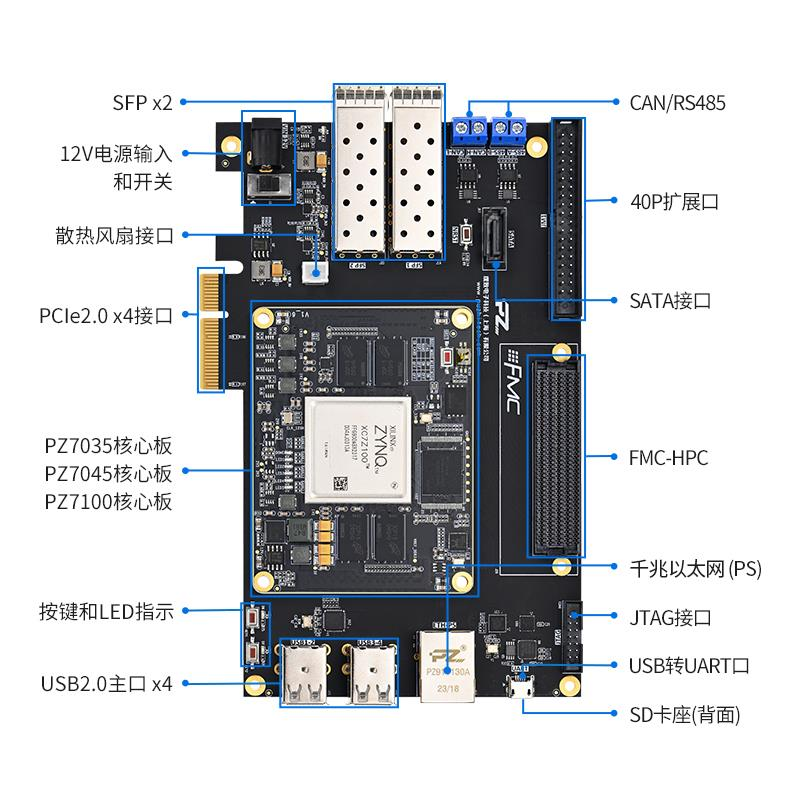

fpga开发板 璞致ZYNQ 7000 系列之 PZ7035/PZ7045/PZ7100-FH 核心板与开发板用户手册

本文介绍了Xilinx Zynq-7000系列可扩展处理平台及其开发板应用。Zynq-7000采用双核ARM Cortex-A9处理器与28nm FPGA架构,支持高性能嵌入式开发。开发板采用核心板

Zynq-7000 SoC与7系列设备内存接口解决方案数据手册

关于 AMD/Xilinx 7系列FPGA存储器接口解决方案(UG586) 的用户指南,其主要内容和技术要点可概括如下:1. 文档定位与核心内容定位:该文档是7系列FPGA中存储接口控制器的官方技术手册,适用于使用LogiCORE IP核(如DDR3/DDR2 SDRAM、RLDRAM II、QDRII+)进行存储器接口设计26。核心功能:IP核配置与时序:详细说明Xilinx MIG(Memory Interface Generator)IP核的使用方法,包括信号定义、时序约束、物理层(PHY

发表于 07-28 16:17

•3次下载

CH367连接zynq问题

通过四线SPI连接CH367和zynq时,CH367使用CH367StreamSPI函数设置为四线模式,然后设置SDI为MISO,SDX为MOSI,SCS和SCL

发表于 07-03 10:10

Veloce Primo补全完整的SoC验证环境

0 1 简介 SoC 设计团队的任务是在创建昂贵的生产掩膜之前完成完整的系统级验证。这意味着彻底审核所有硬件模块、这些模块之间的所有交互以及为最终应用创建的所有专用软件,而且所有这些任务都要

如何使用BootGen为Zynq-7000 AP SoC构建完整的映像

如何使用BootGen为Zynq-7000 AP SoC构建完整的映像

评论