01

简介

SoC 设计团队的任务是在创建昂贵的生产掩膜之前完成完整的系统级验证。这意味着彻底审核所有硬件模块、这些模块之间的所有交互以及为最终应用创建的所有专用软件,而且所有这些任务都要在芯片构建之前完成。虽然硬件加速器和桌面原型板是这项验证中两个众所周知的参与者,但企业原型同样具备重要的意义。

尽管仿真在设计的早期阶段占据主导地位,但由于性能的原因,其更多的适用于模块级验证。一旦开始全芯片验证,势必需要以更快的速度处理实现完整覆盖率所需的庞大数量的测试。硬件加速仿真承担了其中大部分的工作负荷,而桌面原型单元则主要协助软件开发人员检验他们的应用代码。

最近,市场上出现了填补硬件加速器的强大功能与原型设计系统性能之间缺口的需求。这种解决方法被称为企业原型设计,因为它融合了硬件加速仿真和桌面原型设计的特性,可以满足在数据中心环境减轻硬件加速器负荷的新型使用案例的需求。利用它,验证团队可以在优化总体拥有成本的同时,强化其基于高速硬件的验证资源。将硬件加速仿真、企业原型设计和桌面原型设计相结合,可以将 SoC 更快地推向市场,并增强对于芯片正确性的信心。

02

硬件加速器任务 — 新旧比较

硬件加速器已成为 SoC 硬件验证的主力军。它们的执行速度能够高出普通仿真几个数量级,是审核布置在单个芯片上大量硬件的关键要素。

硬件加速器设计体现了性能、实现各种可能的设计所需的基础设施,以及最重要的,在出现问题时可实现全面调试的众多工具之间的平衡。即使它们的运行速度达不到最终应用的速度,但要执行关键软件仍旧绰绰有余,这也意味着,它们可以在启动操作系统的同时探索类似软件的低层驱动程序。

在线硬件加速仿真 (ICE) 是硬件加速器的另一种任务,这种任务在以前比较常见。ICE 的目标是为被测设计 (DUT) 输入真实世界的工作负载,连接网络或其他硬件以提供真实的数据流。由于 ICE 连接需要速率适配器来降低数据速率,以匹配硬件加速器的速度,因此验证团队已转而使用虚拟化流量生成器,而不是 ICE。

VirtuaLab 虚拟化流量生成器可根据命令创建真实的工作负载。由于硬件加速器现在位于可从世界任何地方访问的数据中心内,这些激励源可通过网络建立连接,轻而易举地匹配硬件加速器的速度。因此,硬件速率适配器不是必要的,并且还能轻松、灵活地支持更广泛的工作负载。

03

硬件加速器需要减负

硬件加速器承担了 SoC 验证的中央角色。这意味着每当电路发生变化时,必须重新运行回归测试。这些回归套件必须以尽可能快的速度执行数量持续增长的测试。这些测试已经通过一次,因此除非暴露出回归错误,否则它们预计都会通过后续的每次测试。这意味着通常不需要硬件加速器的众多调试功能。如果有失败的回归测试,那么硬件加速器可能是确定失败原因的最佳角色,但正常而言,这只是极少的例外情况。

04

企业原型设计填补缺口

硬件加速仿真减负是企业原型设计单元的作用之一。它采用与硬件加速器相同的方式安装在机架中并可远程访问。于是便可以将回归套件从稀缺且更昂贵的硬件加速器转移到成本较低的企业原型上。如果回归测试失败并且需要硬件加速器提供调试资源,则可以轻松地将该测试移回到硬件加速仿真环境进行根本错误原因调试。

除了以更低的成本提供更大容量之外,硬件加速器 DUT 也可以直接在原型上运行,几乎不需要手动修改,运行速度大约是在硬件加速器上运行时的五倍。借助一些额外的 FPGA 优化工作,相比 Emulation,往往可以将回归性能提升到 10 倍之多。这意味着回归套件的运行速度也会加快,有助于分担夜间回归工作负荷,避免硬件加速器不堪重负。

最后,就像他们的桌面竞争产品一样,企业原型也可以用于 ICE,利用非虚拟化的直接数据源连接。虽然由于网络连接的原因,用于硬件加速仿真的虚拟化数据源会遭遇额外的事务处理延迟,但直接数据连接提供的数据更接近于实时数据。

通过承担回归、软件验证和 ICE 测试任务,企业原型可以减轻硬件加速仿真工作负载,同时实现原型在功能、速度和成本方面的优势。

硬件加速器可在任何时候加载任意数量的设计。它们甚至大到足以同时加载多个项目。它们可以通过网络轻松进行配置,有助于最大限度地提高它们的利用率。因此,一组给定的测试可能第一天在一个硬件加速器上运行,第二天又在另一个硬件加速器上运行。

相形之下,由于企业原型通常使用专用硬件配置,例如布线配置或 ICE 外围设备,因此更典型的做法是,在项目持续期间配置一组特定的企业原型。包括连接 ICE 数据源在内,配置操作发生在项目开始时,之后便可根据需要使用这些原型,直到项目完成。这时便可以将它们重新用于另一个项目,而无需发运到世界各地。

05

桌面原型板的作用

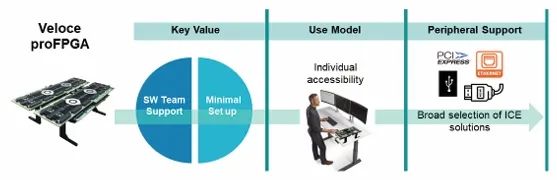

桌面原型板是应用软件的更优解决方案。一旦硬件设计稳定下来,就会对原型验证板进行配置,并且在剩余的验证周期内只进行少量的改动。它们通常采用 FPGA,可以在实现 DUT 的过程中优化性能。它们的运行速度可能比硬件加速器快一个数量级。

将这些低成本的原型板分发给软件开发人员,由他们将这些板插入自己的桌面服务器。当需要运行软件测试时,他们就可以更快地收到基于实际硬件设计的结果。

由于它们的速度很快,将这些板直接连接到真实世界的数据源也更加轻松。于是,ICE 便基本上从硬件加速器转移到桌面原型板上。

06

完整的 SoC 验证环境

Veloce 提供了三种关键的基于硬件的完整 SoC 验证工具:

Veloce Strato 硬件加速器提供了验证大型 SoC(包括硬件、软件驱动程序、操作系统和部分应用代码) 所需的容量和调试可见性

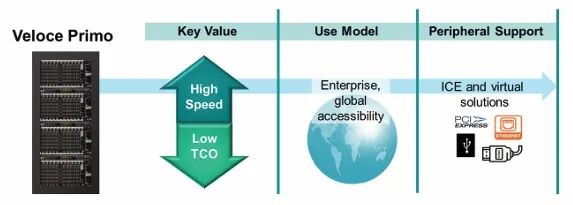

Veloce Primo 企业原型为运行硬件加速仿真回归套件、执行 ICE 测试和验证应用软件提供了更高性能的硬件

对于希望更直接地接触其原型板以进行本地测试的软件开发人员,则可使用 Veloce proFPGA 桌面原型。此外,开发人员还可以将桌面原型发送给他们的客户,以便顺利进行系统集成、验证和有效性确认

Veloce Primo 企业原型系统提供了比桌面原型更高的容量,以及比硬件加速器更低的每门成本和每 MHz 成本。这有助于验证团队降低其硬件验证资源的总体拥有成本,同时也有助于加快验证周期。

-

soc

+关注

关注

38文章

4514浏览量

227631 -

芯片验证

+关注

关注

5文章

40浏览量

47878 -

硬件加速器

+关注

关注

0文章

43浏览量

13345 -

Veloce

+关注

关注

0文章

14浏览量

14149 -

西门子EDA

+关注

关注

1文章

10浏览量

135

原文标题:Veloce Primo 补全完整的 SoC 验证环境

文章出处:【微信号:Mentor明导,微信公众号:西门子EDA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

肖克利 | 极端环境测试,让验证与实战同频!

在Linux ubuntu上使用riscv-formal工具验证蜂鸟E203 SoC的正确性

Wisim DC电源完整性EDA物理验证仿真工具介绍

西门子 Veloce CS 助力 Arm Neoverse 计算子系统验证与确认

西门子桌面级原型验证系统Veloce proFPGA介绍

【道生物联TKB-620开发板试用】TK8620 RISC-V开发环境搭建和固件编译和烧录

中微公司ICP双反应台刻蚀机Primo Twin-Star取得新突破

AMD技术赋能西门子FPGA原型设计解决方案

西门子EDA邀您相约2025玄铁RISC-V生态大会

新思科技推出全新硬件辅助验证产品组合

西门子Veloce硬件辅助验证平台升级

Oracle数据库的多功能集成开发环境

Veloce Primo补全完整的SoC验证环境

Veloce Primo补全完整的SoC验证环境

评论