声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1664文章

22508浏览量

639447 -

收发器

+关注

关注

10文章

3840浏览量

111472 -

赛灵思

+关注

关注

33文章

1798浏览量

133673

发布评论请先 登录

相关推荐

热点推荐

Xilinx FPGA中IDELAYCTRL参考时钟控制模块的使用

IDELAYCTRL 是 Xilinx FPGA(特别是支持高速 I/O 的系列,如 Virtex-5/6/7、Kintex-7、Artix-7、Spartan-6/

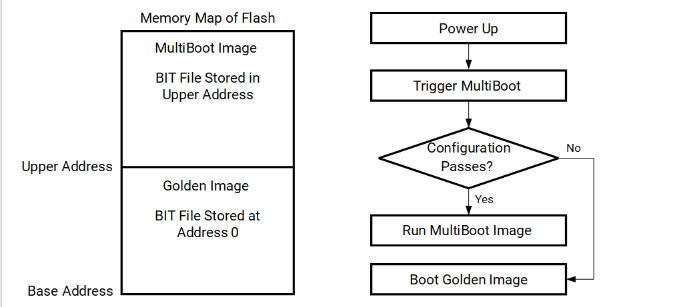

【ALINX 教程】FPGA Multiboot 功能实现——基于 ALINX Artix US+ AXAU25 开发板

教程目的 本教程介绍如何在 ALINX Artix US+ AXAU25 FPGA 开发板上,通过 Multiboot 实现多个 bitstream 的存储与动态切换,并在配置失败时自动回退

FPGA 专业级开发平台性价比之选,ALINX Artix US+ PCle AXAU25

在 FPGA 选型中,很多工程师会因为需要 16Gbps 的收发器而不得不选购昂贵的 Kintex 系列。但如果你的算法并不需要上百万的逻辑资源,这种为了带宽买逻辑的做法其实是巨大的成本浪费

急急急!我正在使用vivado2019.2,请帮忙生成一个项目。

请帮忙生成一个项目:输入一个整数,输出该整数各位数之和,在触摸屏输入整数,在触摸屏输出计算结果。

使用的板子的family是Artix-7,package是fbg676,speed是-2,产生的代码

发表于 12-19 23:17

请问如何将蜂鸟E203移植到Xilinx NEXYS A7 FPGA 开发板上?

如何将蜂鸟E203移植到Xilinx NEXYS A7 FPGA 开发板上?有参考教程吗?小白求教

主要是引脚分配,我这边有移植到Xilinx Artix-7 系列XC7A100T-f

发表于 11-11 07:44

如何不用olimex ARM-USB-TINY-H debugger实现调试?

/board.tcl中将型号改为xc7a100ticsg324-1L,然后到e200_opensource/fpga/artydevkit/constrs/arty-master中,根据Art

发表于 11-10 08:15

【开源FPGA硬件】硬件黑客集结:开源FPGA开发板测评活动全网火热招募中......

式发布啦!现面向全网招募第一批工程师/硬件爱好者,开发板免费试用测试啦!

优秀试用报告,将作为板卡配套资料发布~

相关链接: 拥抱开源!一起来做FPGA开发板啦!火爆开发中 | 开源FPGA

发表于 10-29 11:37

一代蜂鸟E203移植普通Artix7核心板中IDE的cfg配置文件修改

大家好,本次我们团队想要分享的是如何将一代蜂鸟E203移植入自己的FPGA并协同NucleiStudio进行Debug时,其中cfg配置文件的修改;

首先我们使用的是Xilinx Artix-7

发表于 10-29 06:45

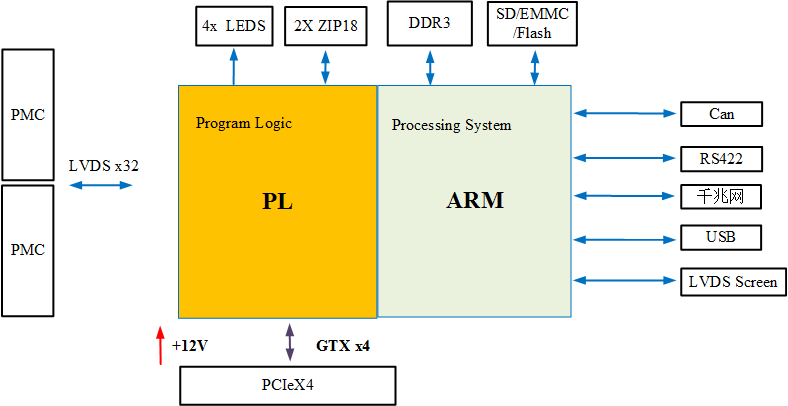

PCIe接口卡设计原理图:124-基于XC7Z015的PCIe低速扩展底板

板卡由SoC XC7Z015芯片来完成卡主控及数字信号处理,XC7Z015内部集成了两个ARM Cortex-A9核和一个Artix 7的FPGA

fpga开发板 璞致Artix-7系列之PA-Starlite Artix7 A735T 75T 100T 200T开发板用户手册-学习板

Artix-7系列开发板是一款基于Xilinx XC7A35T/75T/100T/200T芯片的低成本FPGA开发平台。该系列开发板具有功耗低、体积小(90x60mm)、外设丰富等特点,提供两种供电

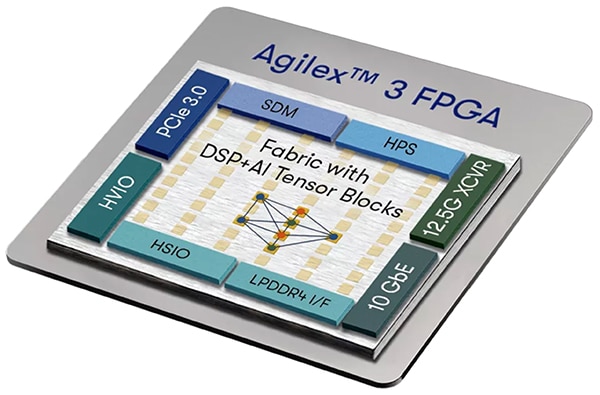

如何在资源受限型应用中使用 FPGA

的性能需求,同时在严格的功耗、尺寸和成本限制内运行。现代现场可编程门阵列 (FPGA) 可以满足这些相互竞争的需求。 本文回顾了为资源受限型应用选择 FPGA 时需要考虑的关键设计标准。然后,以 [Altera] 经过[功率和成

企业级HDFS高可用与YARN资源调度方案

作为一名在大数据运维领域摸爬滚打8年的老兵,我见过太多因为基础架构不够健壮而导致的生产事故。今天,我想和大家分享一套经过实战检验的 HDFS 高可用与 YARN 资源调度方案,这套方案帮助我们团队将平台可用性从 99.5% 提升

火爆开发中 | 开源FPGA硬件板卡,硬件第一期发布

设计,详细分工见下文。

01 最终硬件方案

7月6日,相关硬件人员进行了会议讨论,最终确定硬件方案确定如下:

电源:外部电源输入采用电源适配器输入,使用电源芯片为

发表于 07-09 13:54

火爆开发中|开源FPGA硬件板卡,硬件第一期发布

开源FPGA项目自发布以来,得到了众多开发者的关注,涉及工业、通信、车载等多个行业的100+位工程师报名参与设计,并分为:硬件组、FPGA组、linux组。其中硬件组率先开始启动项目,

Artix-7 FPGA中可用的专用硬件资源介绍

Artix-7 FPGA中可用的专用硬件资源介绍

评论