文章来源:老千和他的朋友们

原文作者:孙千

本文主要讲述薄膜应力与晶圆曲率法。

薄膜是现代微电子、光子学与微机电系统(MEMS)器件最基础的构成单元,小到芯片里的导电层、绝缘层,大到光学镜头的镀膜、MEMS传感器的微结构,都离不开薄膜材料,而这些薄膜的性能稳定性、器件使用寿命,核心都由内部的残余应力所决定。

这种应力并非微电子时代才出现的新问题,早在传统电沉积加工、光学涂层制备的年代,科研人员就已经发现薄膜应力会直接影响产品质量,经过数十年的研究探索,薄膜应力的测量早已从经验判断发展为严谨的定量检测技术。

在众多测量手段中,晶圆曲率法凭借通用性强、检测无损、适配工业场景的优势,成为纳米至微米级薄膜双轴应力测量的首选方案,也是连接材料基础研究与实际器件制造的关键技术支撑。

薄膜应力本质上是一种依附于基底存在的二维力学状态,薄膜的厚度通常只有纳米到微米级别,和横向的延展尺寸相差极大,因此应力无法向三维空间释放,只能集中在薄膜的平面内形成双轴应力,这种面内应力会持续作用于薄膜与基底的结合界面,带动整个基底与薄膜的复合结构发生均匀或非均匀的弯曲,我们只需要精准测量出这种弯曲的程度,就能通过经典的Stoney公式反向计算出薄膜内部的平均应力。

薄膜应力的两大成因:本征应力与热应力

薄膜最终呈现的应力状态,是本征应力与热应力共同叠加的结果,二者的产生机制与作用场景各不相同。

本征应力在薄膜生长沉积的过程中就已经形成,是薄膜自身微观结构带来的固有应力,当薄膜与基底的晶格常数存在差异时,界面处的原子为了保持排列共格会发生弹性形变,超过一定厚度后,部分形变释放,剩余的部分就成为本征应力。

而沉积过程中的高能粒子轰击、晶粒不断生长粗化、杂质原子掺入或是材料发生相变,也会让原子排列变得不规则、局部体积出现收缩或膨胀,进一步加剧本征应力的形成,比如工业中常用的溅射沉积工艺,就会因为高能粒子的持续轰击,让生成的薄膜带有明显的压应力。

热应力则是由温度变化引发的力学效应,薄膜与基底的热膨胀系数天生存在差异,当薄膜沉积后从高温冷却至室温,或是器件工作时温度发生波动,二者的膨胀与收缩幅度无法同步,界面之间就会相互约束拉扯,进而产生热应力。

若薄膜的热膨胀系数大于基底,冷却后薄膜会被基底限制收缩,从而承受压应力,反之则会形成张应力,高温沉积的薄膜在降温过程中,这种热失配带来的应力会让整片晶圆出现碗状的宏观翘曲,直接影响超大规模集成电路制造中光刻工艺的聚焦与套准精度,降低芯片生产良率。

从应力带来的实际影响来看,张应力会让薄膜被过度拉伸,出现细微裂纹甚至整片剥离,压应力则会让薄膜被挤压褶皱、鼓起屈曲,最终同样会发生脱落失效,两种应力一旦超出合理范围,都会直接破坏薄膜结构,缩短器件的使用寿命。

薄膜应力的主流测量技术对比

为了精准捕捉薄膜内部的应力状态,科研与工业领域逐步研发出多种测量技术,整体可分为直接力学测量与间接应变换算两类,不同方法的适用场景与优缺点十分清晰。

X射线衍射法是针对结晶薄膜的半无损检测技术,能够聚焦1到2毫米的小区域测量弹性应变,再通过应变推算应力,但这种方法容易受材料织构、射线偏转角度校准、晶粒尺寸等因素影响,测量范围与精度存在一定局限。

接触式探针曲率法也就是常见的台阶仪,虽然能覆盖微米级微区到毫米级宏观区域的测量,也不需要提前输入薄膜的参数,但探针与样品表面直接接触,会对超薄或质地柔软的薄膜造成物理损伤,且微米级的探针定位难度极高,多次测量的数据重复性较差,无法满足工业量产检测的需求。

相比之下,激光曲率法的综合优势尤为突出,它采用非接触式的光学检测,不会对薄膜造成任何损伤,不需要提前知晓薄膜的弹性性能与微观结构,几乎适用于所有类型的薄膜材料,只要求样品表面平整可以反射激光、结构变形处于弹性范围内,同时具备测试速度快、检测范围广的特点,测量结果能代表毫米级区域内的平均应力,也正是这些优势,让激光辅助的晶圆曲率法成为薄膜应力检测的金标准。

晶圆曲率法:Stoney公式与核心测量逻辑

晶圆曲率法是行业内应用最广泛的应力测量方式,测量基底弯曲主要分为两种路径,一种是测量位移,可通过机械与机电量规、高倍显微镜观察或光学干涉数条纹实现,另一种是直接测量曲率,既可采用光学手段,单晶衬底还能借助X射线衍射技术完成。

测量位移与测量曲率都能达到所需灵敏度,二者存在明确的几何对应关系,当曲率半径R=100m、测试宽度w=100mm时,位移量h仅为12.5μm,角度θ仅为10⁻³弧度,若要达到1%的测量精度,位移需精确测量至125纳米,角度需精确至10⁻⁵弧度,这也对检测设备的精度提出了严苛要求。

位移测量与角度测量的对比。当R=100m、w=100mm时,h=12.5μm,θ=10−3弧度。要达到1%的测量精度,h得测到125纳米,θ得测到10−5弧度。

晶圆曲率法的定量计算核心是经典的Stoney公式,这个公式将测量得到的曲率半径与薄膜应力直接关联,公式中只需要用到基底的杨氏模量、泊松比、厚度以及薄膜厚度这几个参数,完全不需要了解薄膜的内部结构与力学特性。

Es是衬底的杨氏模量(衬底抗拉伸的能力),vs是衬底的泊松比(拉伸时横向收缩的比例),hs是衬底厚度,hf是薄膜厚度。k是曲率,k=1/R,R为曲率半径。

针对不同取向的单晶基底,研究者Brantley已经给出标准化的E/(1−ν)参考值,实际检测时直接取用即可,大幅降低了测量的操作难度。

这套方法的核心逻辑是对比测量,先在薄膜沉积前测量裸晶圆的初始曲率,作为基准数据,再测量镀膜后晶圆的曲率,将两次数据逐点做差,剔除基底本身曲率的影响,就能精准得到薄膜带来的真实应力变化,这种简洁且灵敏的检测方式,让Stoney公式成为晶圆曲率测量技术沿用数十年的核心理论基础。

工业级薄膜应力仪

自Sinha首次提出激光扫描测量曲率的技术后,该技术经多人改良优化,成为成本低、速度快、易自动化的高性价比方案,也成为商用薄膜应力仪的核心原理,完美适配了超大规模集成电路制造的严苛需求。

微电子制造中会用到金属、半导体、无机绝缘体、聚合物等各类薄膜材料,这些薄膜在制备后大多处于高应力状态,应力引发的失效分为两种,一种是即时失效,比如金属导线直接断裂造成电路断路,另一种是延迟失效,比如钝化层出现微裂纹,水汽与杂质渗入后引发内部腐蚀,最终导致器件损坏。

因此用于芯片制造的应力测量设备必须满足多项关键要求,既要具备足够的灵敏度与重复性,能捕捉微小的应力变化,又要在薄膜的原始基底上原位测量,保留沉积工艺与界面作用的真实状态,同时还要能追踪应力随温度、时间的动态变化,适配繁多的材料与工艺,支持计算机自动化无人值守测试,兼顾大幅度翘曲与微小变形的检测,拥有足够宽的动态范围。

速普仪器研发的FST系列薄膜应力仪,正是基于激光曲率法与Stoney公式打造的商用化设备,采用635纳米与670纳米双波长激光对样品轮廓进行非接触式扫描,通过对比镀膜前后的曲率变化,结合基底参数精准计算薄膜应力。

该系列包含三款适配不同场景的型号,FST5000支持室温下的手动上样与自动面扫Mapping,FST5000H在基础款之上新增500℃真空加热功能,可满足高温环境下的应力测试需求,FST6000则实现了自动上样与全自动常温测量,适配量产化的检测流程。

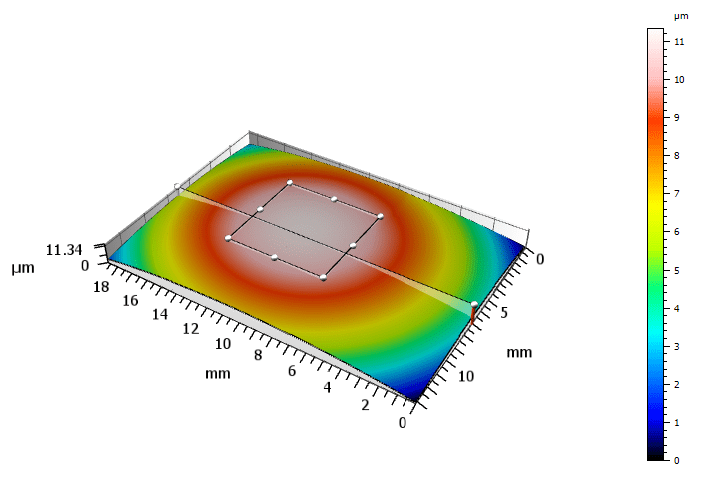

无论是硅、砷化镓这类不透明基底,碳化硅、铌酸锂这类半透明基底,还是蓝宝石、石英这类透明基底,都能完成精准的应力检测,还能生成详细的三维应力分布图谱,清晰呈现薄膜的应力分布特征,无论是微米级到百微米级翘曲的样品,还是十兆帕到千兆帕级应力的薄膜,都能稳定捕捉数据,目前已广泛应用于半导体生产线、MEMS器件研发以及高校科研实验室,经过十年技术迭代,成为薄膜应力检测领域的主流设备。

晶圆曲率法的固有局限

尽管晶圆曲率法是目前最实用的薄膜应力测量技术,但它依然存在无法回避的局限性,其核心短板就在于它是一种必须依赖基准的对比测量方法。即便高纯度的单晶硅晶圆,本身也存在一定的初始曲率,且这个曲率的大小与薄膜应力引发的弯曲曲率十分接近,若不先测量裸晶圆的基准数据,就无法剥离出薄膜的真实应力。同时晶圆的弯曲通常并非均匀分布,沉积前后两次测量时,晶圆在检测载台上的摆放位置必须精准对齐,否则会产生明显的系统误差。

在多层薄膜堆叠的结构中,这种对比测量会出现大数相减取小数的精度丢失问题,误差会被大幅放大,比如在高应力的介质薄膜上沉积金属薄膜,金属薄膜的应力远小于介质层,其带来的曲率变化微乎其微,很难被精准分辨。

实际检测过程中,温度波动也是影响精度的重要因素,硅基底上的铝薄膜仅2℃的温度变化,就会对应数兆帕的应力误差。

薄膜应力的双面影响:调控与失效

薄膜应力对材料性能与器件应用的影响具有鲜明的两面性,合理调控可以成为提升性能的有效手段,控制不当则会引发严重的失效问题。在积极应用层面,可控的应力能够精准优化材料的关键性能,半导体领域成熟的应变硅技术就是最典型的案例,通过人为向PMOS晶体管施加压应力提升空穴迁移率,向NMOS晶体管施加张应力增强电子迁移率,能显著提高晶体管的运行速度,降低工作电压,且完全兼容现有的芯片制造工艺,成为先进半导体工艺的核心技术之一。

在消极影响层面,过量的应力会直接导致薄膜附着力下降、开裂脱落,大尺寸或薄基底的晶圆在应力作用下发生翘曲,会直接破坏光刻工艺的精度,导致芯片良率降低,同时应力还会改变光学薄膜的反射透射光谱、磁性薄膜的磁各向异性,让MEMS器件出现结构变形、谐振频率漂移等问题,影响器件的稳定性与可靠性。

针对这些问题,科研人员已经研发出针对性的应力工程解决方案,航空航天光学窗口的增透膜通过设计梯度过渡层或引入柔性层,缓冲薄膜与ZnS基底之间的热应力,高功率激光反射膜通过材料配对优化、沉积工艺调整与后退火处理,降低并稳定内部应力,MEMS微悬臂梁传感器采用双材料层应力补偿设计,能将温度漂移降低60%,RF MEMS开关则通过复合膜层设计与精细的工艺控制,将应力调节至理想范围,有效延长器件使用寿命。

金属与介质薄膜的应力特征差异

金属薄膜与介质薄膜的应力行为存在明显差异,其中金属薄膜的应力机制最为复杂,也是研究最透彻的体系,其初始应力的大小核心取决于沉积温度与金属熔点的比值,这个参数直接决定了金属原子在沉积过程中能否自由扩散。

铝这类低熔点金属在室温或稍高温度下沉积时,原子拥有足够的动能移动,形成的薄膜结构致密,应力水平极低,而钨这类高熔点金属在常温下原子几乎无法扩散,会形成非平衡结构,初始应力极大,溅射钨薄膜通常呈现高压应力,化学气相沉积的硅化钨则多为高张应力。

若金属薄膜在结晶基底上实现外延生长,即便原子可以自由移动,晶格失配也会让薄膜天生携带应力,后续的加热冷却、相变、塑性变形等过程,还会持续改变薄膜的应力状态。沉积在非晶衬底上的铝基金属化层,在中等温度沉积时结构稳定,其塑性变形应力可通过公式σ=τ⋅(1−T/TF)计算,τ是绝对零度下无热激活的极限应力,TF是流动应力归零的假设温度,二者的关系能清晰解释金属薄膜的应力变化。

介质薄膜的应力行为则更具规律性,高温条件下制备的热氧化介质膜初始应力极小,室温下观测到的少量应力仅由热膨胀系数差异导致,热循环过程中不会出现应力滞后,常温下性能十分稳定。

而低温沉积的介质膜会形成非平衡结构,初始应力普遍偏高,磷硅玻璃(PSG)在室温潮湿环境中会吸收水分,压应力持续增大,加热到中等温度后水分散失,应力从压应力转为拉应力,400℃以下该过程完全可逆,继续升温则会发生致密化,消除内部微孔,不再大量吸水,硼磷硅玻璃(BPSG)也遵循相同的失水与致密化规律。

硼磷硅玻璃(BPSG)中因失水和致密化引起的应力变化

等离子体增强化学气相沉积的氮化硅薄膜,初始多为高压应力,加热到400℃以上时,沉积过程中被困在薄膜内部的氢原子会逐步扩散释放,引发不可逆的应力变化,甚至从压应力转变为张应力,这种恒温下的应力变化,可用扩散方程的解完美拟合,与硅基玻璃水分扩散的规律高度一致。

等离子体增强化学气相沉积(PECVD)氮化硅在加热过程中的应力变化

晶圆曲率法的价值

晶圆曲率法凭借光学检测的便捷性,能够快速准确地获取微电子、MEMS、光学薄膜等领域关键薄膜的应力数据,以及应力随时间、温度的变化规律。在薄膜应力的诸多影响因素中,薄膜与基底的热膨胀差异固然会产生应力,但沉积过程中形成的初始本征应力、微观结构演化、水分得失、氢气释放等因素,对应力的影响往往远大于热膨胀效应。

想要全面掌握一类薄膜的应力特性,就必须追溯其从沉积到后处理的完整工艺历史,同时选择适配的测量设备与测试方案,精准获取应力数据,这也是优化薄膜材料性能、提升器件可靠性与生产良率的核心环节。而晶圆曲率法也将持续作为薄膜应力测量的核心技术,支撑着薄膜材料与器件制造领域的不断发展。

-

薄膜

+关注

关注

1文章

374浏览量

46258 -

mems

+关注

关注

129文章

4529浏览量

199538 -

晶圆

+关注

关注

53文章

5448浏览量

132740

原文标题:薄膜应力与晶圆曲率法

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

解析LED晶圆激光刻划技术

什么是晶圆测试?怎样进行晶圆测试?

圆片RTA退货步后出现SiN薄膜破裂现象

WD4000系列晶圆几何量测系统:全面支持半导体制造工艺量测,保障晶圆制造工艺质量

清洗晶圆去除金属薄膜用什么

深度解析薄膜应力与晶圆曲率法

深度解析薄膜应力与晶圆曲率法

评论