双锁相环邻频调制器制作,Phase-locked loop

关键字:锁相环调制器电路图

作者:林德耀

本制作是在单片机控制下,通过复位开关对双锁相环邻频调制器输出的电视频道进行递增或递减的切换,基于上期(09年第七期)所描述的双锁相环邻频调制器设计与制作的基础上,在MC145152AP、MC12022锁相分频的环节上,对电视频道的本振频率(比欲设频道的图像载频高38MHz)进行数字编码,根据编码规则所获得的信息进行C语言的程序设计。仿真测试通过后将程序烧录在AT89C52单片机芯片内,制作成的电路通过两个复位开关进行电视频道的切换,并将有关数据显示在LCD液晶显示屏上。

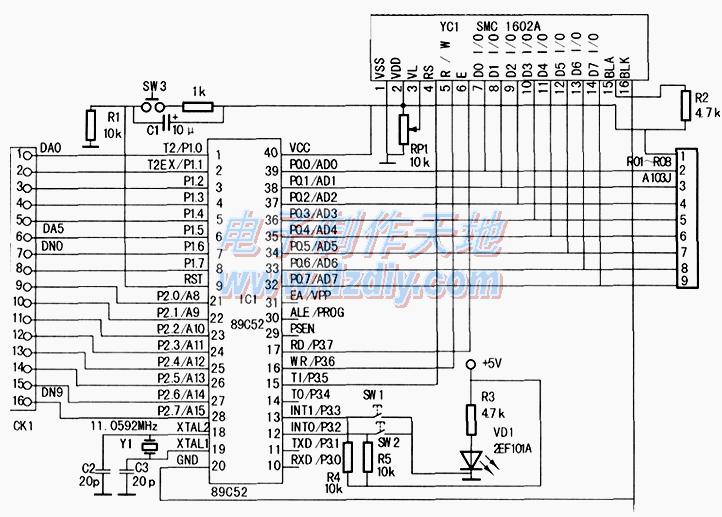

一、单片机控制电路原理

单片机控制电路如下图所示,SW3为复位开关,当按下复位开关SW3时,电路复位,单片机处于起始工作状态(1CH);按下复位开关SW1或SW2,双锁相环邻频调制器输出的电视频道分别作步进递增或递减的变换。

一、单片机控制电路原理

单片机控制电路如下图所示,SW3为复位开关,当按下复位开关SW3时,电路复位,单片机处于起始工作状态(1CH);按下复位开关SW1或SW2,双锁相环邻频调制器输出的电视频道分别作步进递增或递减的变换。

所有的这些信息传递,都是经系统软件处理后由P1、P2口输出欲设频道本振频率相应的数字编码信息至CK1插座上,CK1插座与上期(09年第七期)所描述的MCl45152AP相应端口相连,迫使双锁相环邻频调制器根据人们的意愿进行电视频道的切换,并在LCD液晶显示屏上显示当前所设置的频道数和本振频率。

数字编码信息与LCD液晶显示屏所显示预设频道数及本振频率对应关系一览表如下表所示。

|

频道数

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

发布评论请先 登录 相关推荐

热点推荐

高性能低噪声锁相环LTC6948:设计与应用全解析的高性能、低噪声的6.39GHz锁相环,看看它究竟有何独特之处,以及在实际设计中如何发挥其优势。 文件下载: LTC6948.pdf 一、LTC6948概述 LTC6948是一款集成了VCO的高性能低噪声锁相环,它内部包含参考分频器

深入解析MC44BS374CA:高性能音频/视频调制器的技术奥秘是一款多标准、PAL/NTSC调制器,通过片上高速 (I^{2}C) 兼容总线接收器设置频道。它采用锁相环(PLL)技术

深度解析NXP MC44BS373CA音频视频调制器设备。它通过片上高速 (I^{2}C) -兼容总线接收器设置频道,采用锁相环(PLL)在整个UHF范围内调谐调制器。该调制器集成了声音副

探索CDC516:高性能3.3V锁相环时钟驱动器探索CDC516:高性能3.3V锁相环时钟驱动器 在电子设计领域,时钟驱动器对于确保系统的稳定运行至关重要。今天我们要深入探讨的是德州仪器(Texas Instruments)的CDC516,一款

CDC2516:高性能锁相环时钟驱动器的深度解析CDC2516:高性能锁相环时钟驱动器的深度解析 在电子设计领域,时钟驱动器是确保系统稳定运行的关键组件之一。今天,我们就来详细探讨一款高性能的锁相环时钟驱动

CDC509:高性能3.3V锁相环时钟驱动器CDC509:高性能3.3V锁相环时钟驱动器 在电子设计领域,时钟驱动是一项关键技术,尤其是在同步DRAM应用中,需要高精度、低抖动的时钟信号来确保数据的准确传输。德州仪器(Texas

CDCVF25081:高性能锁相环时钟驱动器深度解析CDCVF25081:高性能锁相环时钟驱动器深度解析 引言 在电子设计领域,时钟驱动器起着至关重要的作用,它直接影响着系统的稳定性和性能。今天我们要深入探讨的是德州仪器(TI)的CDCVF25081

TLC2932A高性能锁相环芯片详解:设计与应用指南介绍的是德州仪器(TI)推出的TLC2932A高性能锁相环芯片,它具有出色的性能和丰富的功能,能为工程师们的设计带来更多便利和可能性。 文件下载: tlc2932a.pdf 一、TLC2932A概述 TLC2932A专为锁相环系统设计,主要由压控振荡

探索TLC2933A高性能锁相环:特性、应用与设计要点,了解其特性、工作原理及应用中的设计要点。 文件下载: tlc2933a.pdf 一、TLC2933A概述 TLC2933A专为锁相环系统设计,主要由电压控制振荡器(VCO)和边缘触发型相位频率检测器

CDCVF2510 3.3V锁相环时钟驱动器技术文档总结该CDCVF2510是一款高性能、低偏斜、低抖动、锁相环 (PLL) 时钟驱动器。它使用锁相环 (PLL) 将反馈 (FBOUT) 输出与时钟 (CLK) 输入信号在频率和相位上精确对齐。它专为

基于锁相环的无轴承同步磁阻电机无速度传感器检测技术使用场合。为实现无轴承同步磁阻电机高速超高速、低成本、实用化运行,提出了一种基于锁相环法的无速度传感自检测技术。通过应用锁相环原理,设计出无轴承同步磁阻电机无速度传感器,并基于 Matlab

发表于 07-29 16:22

高压放大器在锁相环稳定重复频率研究中的应用实验名称: 锁相环稳定重复频率的系统分析 实验内容: 针对重复频率的漂移,引入两套锁相环系统反馈控制两个激光器的重复频率,将其锁定在同一个稳定的时钟源上。本章主要阐述了经典锁相环的原理

Analog Devices Inc. ADF4382x小数N分频锁相环 (PLL)数据手册Analog Devices ADF4382x小数N分频锁相环 (PLL) 是一款高性能、超低抖动、小数N分频锁相环 (PLL)。它集成了压控振荡器 (VCO),是5G或数据转换器时钟

|

双锁相环邻频调制器制作,Phase-locked loop

双锁相环邻频调制器制作,Phase-locked loop

评论