深入解析 SN74LVC1GX04 晶体振荡器驱动芯片

在电子设计领域,晶体振荡器驱动芯片是众多应用中不可或缺的一部分。今天,我们就来详细探讨一下德州仪器(TI)的 SN74LVC1GX04 晶体振荡器驱动芯片,看看它有哪些独特的特性和应用场景。

文件下载:74LVC1GX04DBVTG4.pdf

一、芯片概述

SN74LVC1GX04 专为 1.65 - 5.5V 的 (V_{CC}) 工作电压而设计,它将 SN74LVC1GU04(无缓冲输出反相器)和 SN74LVC1G04(反相器)的功能集成到了一个单一的器件中。该芯片特别适用于晶体振荡器应用,能够提供稳定的时钟信号。

二、芯片特性

(一)封装优势

这款芯片提供了德州仪器的 NanoStar™ 和 NanoFree™ 封装,这两种封装技术是集成电路封装概念的重大突破,它们直接将裸片作为封装,减小了芯片的尺寸,提高了集成度。

(二)电压支持

- 供电电压:支持 5V 的 (V_{CC}) 操作,并且输入能够接受高达 5.5V 的电压,这使得它在不同的电源环境下都能稳定工作。

- 输出驱动:在 3.3V 电压下,具有 ±24mA 的输出驱动能力,能够满足大多数电路的需求。

(三)频率适用性

适合常见的时钟频率,如 15kHz、3.58MHz、4.43MHz、13MHz、25MHz、26MHz、27MHz 和 28MHz,为不同的应用场景提供了广泛的选择。

(四)低功耗与高速性能

- 低功耗:最大 (ICC) 仅为 10μA,具有较低的功耗,适合对功耗要求较高的应用。

- 高速性能:在 3.3V 电压下,最大传播延迟 (t_{pd}) 仅为 2.4ns,能够快速响应信号变化。

(五)其他特性

- 部分掉电模式:支持部分掉电模式操作,通过 (I_{off}) 电路,在芯片断电时可以禁用输出,防止损坏性电流回流。

- 静电放电保护:静电放电保护超过 JESD 22 标准,包括 2000V 的人体模型(A114 - A)和 1000V 的充电设备模型(C101),提高了芯片的可靠性。

三、应用场景

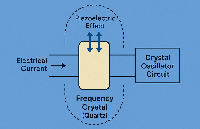

(一)晶体振荡器

SN74LVC1GX04 是晶体振荡器的理想选择,它能够为晶体振荡器提供稳定的驱动信号,确保振荡器的正常工作。

(二)时钟生成

在时钟生成电路中,该芯片可以产生精确的时钟信号,为其他逻辑电路提供稳定的时钟源。

四、芯片引脚配置与功能

| PIN | NAME | I/O | DESCRIPTION |

|---|---|---|---|

| 1 | NC | – | No internal connection |

| 2 | GND | – | Ground |

| 3 | X1 | I | Amplifier input |

| 4 | X2 | O | Amplifier output |

| 5 | VCC | – | Supply power |

| 6 | Y | O | Main output to other logic |

五、电气特性

(一)绝对最大额定值

在使用芯片时,需要注意其绝对最大额定值,超过这些值可能会导致芯片永久性损坏。例如,(V{CC}) 的范围为 -0.5V 到 6.5V,(V{I}) 和 (V_{O}) 的输入输出电压范围也有相应的限制。

(二)ESD 评级

芯片具有良好的静电放电保护能力,人体模型(HBM)的 ESD 评级为 ±2000V,充电设备模型(CDM)的 ESD 评级为 ±1000V。

(三)推荐工作条件

为了确保芯片的正常工作,需要在推荐的工作条件下使用。例如,(V{CC}) 的工作电压范围为 1.65 - 5.5V,不同的 (V{CC}) 电压下,输入输出电流和电压都有相应的要求。

(四)热信息

不同封装的芯片具有不同的热阻,如 DBV(SOT - 23)封装的结到环境热阻为 165°C/W,DCK(SC70)封装为 259°C/W,DRL(SOT)封装为 142°C/W。在设计时需要考虑芯片的散热问题。

(五)电气特性参数

包括输出高电平电压 (V{OH})、输出低电平电压 (V{OL})、输入电流 (I{I})、关断电流 (I{off})、电源电流 (I{CC}) 和输入电容 (C{i}) 等参数,这些参数会随着 (V_{CC}) 电压和温度的变化而有所不同。

(六)开关特性

在不同的负载电容和 (V{CC}) 电压下,芯片的开关特性也会有所变化。例如,在 (C{L}=15pF) 时,不同 (V{CC}) 电压下的传播延迟 (t{pd}) 有不同的取值范围。

六、典型应用电路

(一)皮尔斯振荡器电路

SN74LVC1GX04 在皮尔斯振荡器电路中有典型的应用。在这个电路中,缓冲反相器(SN74LVC1G04 部分)能够产生轨到轨的电压波形。推荐的晶体负载电容 (C_{L}) 为 16pF,其值可以从晶体制造商的数据表中获取。

(二)电路参数计算

- 负载电容 (C_{L}):(C{L}=frac{C{1} C{2}}{C{1}+C{2}}),其中 (C{1}) 和 (C{2}) 的值可以根据需要进行选择,通常 (C{1} equiv C_{2})。

- 限流电阻 (R_{s}):(R{s}=X{C_{2}}),其值取决于晶体的最大功耗,一般在晶体制造商的数据表中会有推荐值。

- 反馈电阻 (R_{F}):通常取值在 1MΩ 到 10MΩ 之间,用于将反相器偏置在线性工作区域。

(三)设计注意事项

- 闭环增益调整:当电源电压降低时,无缓冲反相器的开环增益会减小,从而降低振荡器电路的闭环增益。此时可以减小 (R_{s}) 的值来增加闭环增益,但要确保晶体的功耗在最大限制范围内。

- 低通滤波器:(R{s}) 和 (C{2}) 构成低通滤波器,可以减少杂散振荡。可以根据所需的截止频率调整元件值。

- 相位调整:增加 (C_{2}) 可以增加相移,有助于振荡器的启动,但可能会影响输出电压的占空比。

- 高频处理:在高频情况下,(R{s}) 引起的相移会变得显著,此时可以用电容代替 (R{s}) 来减少相移。

(四)设计步骤

- 空载测试:在没有晶体的情况下,振荡器电路不应振荡。可以用晶体的等效并联谐振电阻代替晶体进行检查。

- 电源电压测试:确保电路在最低 (V{CC}) 和最高 (V{CC}) 下都能以适当的频率振荡。

- 性能测试:确保输出信号的占空比、启动时间和频率漂移在系统要求范围内。

七、电源供应建议

电源电压应在推荐的工作条件范围内,每个 (V{CC}) 端子都应配备一个良好的旁路电容,以防止电源干扰。对于单电源设备,推荐使用 0.1μF 的电容;对于多个 (V{CC}) 端子的设备,每个电源端子推荐使用 0.01μF 或 0.022μF 的电容。可以并联多个旁路电容以抑制不同频率的噪声,并且旁路电容应尽可能靠近电源端子安装,以获得最佳效果。

八、布局设计

(一)布局准则

在使用多位逻辑器件时,输入不应浮空。所有未使用的输入引脚都应连接到高电平或低电平偏置,以防止其浮空。逻辑电平的选择取决于器件的功能,通常会连接到 GND 或 (V_{CC})。

(二)布局示例

虽然文档中没有详细给出布局示例,但在实际设计中,应遵循布局准则,合理安排芯片的引脚和布线,以确保电路的稳定性和可靠性。

九、设备与文档支持

(一)文档支持

相关文档包括《Implications of Slow or Floating CMOS Inputs, SCBA004》,可以帮助工程师更好地理解芯片的使用和注意事项。

(二)社区资源

TI 提供了丰富的社区资源,如 TI E2E™ 在线社区和设计支持,工程师可以在这些平台上提问、分享知识、探索想法和解决问题。

(三)商标信息

NanoStar、NanoFree、E2E 是德州仪器的商标,其他商标归各自所有者所有。

(四)静电放电注意事项

由于芯片的静电放电保护能力有限,在存储或处理时,应将引脚短路在一起或将芯片放置在导电泡沫中,以防止 MOS 栅极受到静电损坏。

(五)术语表

可以参考 SLYZ022 — TI 术语表,了解相关术语、首字母缩写和定义。

十、总结

SN74LVC1GX04 晶体振荡器驱动芯片具有多种优秀的特性和广泛的应用场景。在设计过程中,工程师需要充分考虑芯片的电气特性、应用电路设计、电源供应和布局等方面的因素,以确保芯片能够在不同的应用中稳定可靠地工作。你在使用类似芯片时遇到过哪些问题呢?欢迎在评论区分享你的经验和见解。

-

电子设计

+关注

关注

42文章

2870浏览量

49916

发布评论请先 登录

深入解析DS32kHz:高精度温度补偿晶体振荡器

SN74LVC1G123:单可重触发单稳态多谐振荡器的设计与应用

SN74LVC1G123:单可重触发单稳态多谐振荡器的深度剖析

SN74LVC1G123:单可重触发单稳态多谐振荡器的设计指南

晶体振荡器的主要作用及其在现代社会中的应用

CS-23系列低相位噪声恒温晶体振荡器

压控晶体振荡器参数及选型

深入解析 SN74LVC1GX04 晶体振荡器驱动芯片

深入解析 SN74LVC1GX04 晶体振荡器驱动芯片

评论