简介

DisplayPort(DP)是由视频电子标准协会(VESA)制定的高性能数字视频接口,专为高分辨率显示器和多屏应用设计。

智多晶DisplayPort_RX IP遵循《VESA DisplayPort Standard V1.2a》标准,适用于PC、GPU视频接收或工业视频采集等应用。

IP特性

支持1、2、4 通道

支持线速率1.62、2.7、5.4Gb/s

支持RGB、YCrCb色彩空间

支持最高16bit色彩量化位宽

支持每周期输出1、2、4像素

支持1Mb/sAUX通信

支持eDP与DP接口

支持自定义EDID

支持最高4K*2K@60Hz显示

便利性设计

智多晶DisplayPort_RX IP提供了示例工程,在示例工程中,以源码的形式提供了EDID ROM,用户可以在代码中自行更新EDID信息,也可以通过I2C接口外挂EEPROM存储EDID信息。

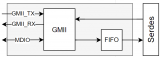

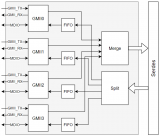

图1 DisplayPort_RX IP示例工程

获取技术文档

技术文档获取:DisplayPort_RX IP已发布,用户可以在HqFpga软件“IP管理”中打开DisplayPort_RX IP界面查看用户指南,或访问智多晶官网(www.isilicontech.com)下载用户指南。

-

接口

+关注

关注

33文章

9588浏览量

157592 -

gpu

+关注

关注

28文章

5259浏览量

136039 -

智多晶微电子

+关注

关注

0文章

24浏览量

258

原文标题:“芯”技术分享|智多晶DisplayPort_RX IP介绍

文章出处:【微信号:智多晶,微信公众号:智多晶】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

SN75DP128A:DisplayPort 1:2 开关的卓越之选

智多晶DSP IP应用介绍

智多晶MCU硬核IP全面升级|CM3和STAR新特性介绍

智多晶MIPI CSI-2 RX IP在固态激光雷达的应用

探索 SN75DP126:DisplayPort 1:2 重驱动开关的特性与应用

智多晶EDA工具HqFpga软件的主要重大进展

智多晶AXI视频通讯DEMO方案介绍

智多晶SGMII IP介绍

智多晶QSGMII IP介绍

智多晶VBO_TX IP产品核心亮点

智多晶eSPI_Slave IP介绍

智多晶FIFO_Generator IP介绍

智多晶DisplayPort_RX IP介绍

智多晶DisplayPort_RX IP介绍

评论