SiC MOSFET 的单管额定电流受芯片面积、封装散热、导通电阻等因素限制,常见的单管额定电流多在几十到两百安培,而轨道交通、新能源并网、高压逆变器等场景,往往需要千安级的电流输出,单管无法满足。因此,SiC MOSFET的并联应用的场景越来越普遍。

不管是SiC MOSFET还是IGBT,并联的目标都是实现电流的均匀分布,且消除芯片间的振荡。为了达到这一目标,我们需要做到三点:

1.并联芯片参数尽可能一致

2.功率回路、驱动回路与散热结构布局一致

3.门极驱动电路的优化设计

作为高速开关器件,SiC MOSFET使其并联应用面临着与IGBT不同的挑战。下面将详细解释实际应用中如何实现以上三点。

器件参数对并联的影响

导通电阻RDS(on)

导通电阻RDS(on)失配会导致静态电流不均衡。这个原理很好理解,MOSFET导通电流时类似于电阻,电流会集中于电阻小的通路。但好在SiC MOSFET的导通电阻是正温度系数,这一特性能有效地对静态电流不均匀形成负反馈。即电流更集中的器件结温更高,导通电阻明显升高,电流转向另外的低阻抗通路,从而实现自动均流的效果。MOSFET导通电阻正温度系数越明显,对静态电流不均衡的抑制效果就越显著。

英飞凌SiC MOSFET系列器件由于采用了沟槽栅技术,其导通电阻具有非常强烈的正温度系数,对静态不均流具有良好的抑制作用。同时,英飞凌所有器件的导通电阻都具有非常低的离散度。下图是英飞凌650V SiC MOSFET导通电阻与平面栅厂家的对比,可以看到,不论额定电阻多少,英飞凌RDS(on)最大值对比典型值的比例都是最低的。

阈值电压VGS(th)

除了静态均流,动态电流不均衡也是困扰并联的一大难题。SiC MOSFEST阈值电压失配是芯片层面导致动态不均流的主要因素。与导通电阻不同,SiC MOSFET阈值电压呈现负温度系数,意味着阈值电压越低的器件,在开通时越容易分到更多的电流,结温升高更明显,阈值电压下降,导致下次开通时得到的电流更高。SiC MOSFET这一特性非常不利于均流,所以阈值VGS(th)一致性的配对就非常重要。不仅常温下阈值要高度匹配,阈值的温度曲线也要尽可能一致。

英飞凌SiC MOSFET阈值电压具有高度一致性。我们测试了4个品牌的各70pcs器件的阈值电压,其中M1是英飞凌的器件。可以看到,英飞凌最大的阈值偏差仅为0.3V,75%的器件偏差值在0.2V以下,明显低于其它厂家,其中M4偏差最大,达到了0.6V,是英飞凌的两倍。

除了常温阈值的严格一致性,相对于平面栅厂家,英飞凌 CoolSiC产品具备更低的栅源阈值电压温度系数,这使得其对动态电流不均流的正反馈就非常弱。这一特性可保障并联运行的稳定性,因此具有显著优势。

英飞凌SiC MOSFET之所以具有良好的阈值一致性以及稳定性,是源于沟槽栅结构的天然优势。MOSFET的阈值电压VGS(th)是使器件开始形成导电沟道所需的最小栅极与源极之间的电压。在平面栅结构中,沟道形成于硅片表面,容易受到后续离子注入、退火等工艺的影响。而在沟槽栅结构中,沟道掩埋于硅片内部,且沟槽内填充多晶硅,可有效保护沟道不受后续工艺影响,从而保证了阈值的一致性。

小结

英飞凌CoolSiC MOSFET更适用于并联应用。沟槽型SiC MOSFET具有参数一致性的天然优势。

功率回路布局对并联的影响

驱动反馈回路不对称

源极回路电感负反馈

如图所示,如果功率回路和驱动回路共用源极,则器件开通时的电流变化率di/dt会在源极电感产生感应电压V=L*di/dt。感应电压与驱动电压方向相反,相当于减弱了门极驱动能力,使得开通速度变慢。如果两个并联的器件源极反馈不一致,就会导致两个管子开通速度不一致,从而影响动态均流。

下图给出了源极回路不对称的常见案例。对于插件式封装,比如TO247,管脚长度不一致,就会造成源极电感失配。

对于贴片式D2PAK封装,器件一左一右放置,右边的器件源极路径就会比左边器件更长。

电容反馈回路不对称

PCB布版中两个导电层相交叠就会形成电容。如果这个寄生电容出现在漏极和栅极之间,相当于增加了器件的米勒电容Cgc,使得关断时dv/dt变慢。

在下图的示例中,右边的器件的栅极引线与漏极引线交叠,这里就会产生一个额外的寄生电容Cgc。

功率回路不对称

主功率换流回路不对称会引起源极电感与漏极电感不对称,不仅会引起电流及损耗的不均衡,也会引起电压过冲的不均衡。

典型的PCB布局及改善方法如下图所示。初版设计中两个D2PAK器件左右放置,源极与漏极功率走线分别朝左右走线。所在左边器件的漏极电感LD较高,右边器件的源极电感LS较高。改版之后,虽仍保持器件左右放置,但功率走线从垂直方向引出,这样就证了两个器件功率回路对称。

改版前

改版后

散热布局不对称

散热路径的不对称,也会对并联均流造成很大影响。在下面的例子中,并联的单管器件在散热器上左右放置,冷却液左进右出,会造成从左至右明显的温度梯度。改善后的布局,冷却液上进下出,并增加了扰流槽,温度梯度呈上下分布,左右两边的器件散热环境一致。

小结

系统设计应尽量对称,对性称可以通过交换器件交叉验证。

如何设计驱动电路设计改善均流

从前面的分析可得知,芯片参数、功率布局等因素都会影响均流。即使器件经过严格筛选,PCB也经过精心设计,这些失配因素也无法彻底消除。这时我们可以通过驱动电路的设计进一步降低这些失配因素对并联均流的影响。

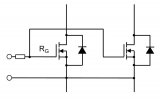

对于驱动电阻的设计,建议使用如下配置网络:

带有辅助源极的器件并联,辅助源极会形成电流回路,可以使用发射极限流电阻Rs,抑制源极电阻环流。

并联器件辅助源极环流

开尔文源极电阻抑制环流

栅极电阻分为共同电阻Rgcom(下图的Common resistor),和独立电阻Rgi(下图的Separate resistors)。共同电阻Rgcom可以抑制阈值Vth/Cgc/Cgs失配引起的动态电流不均衡,独立电阻Rgi可削弱并联芯片间的振荡。

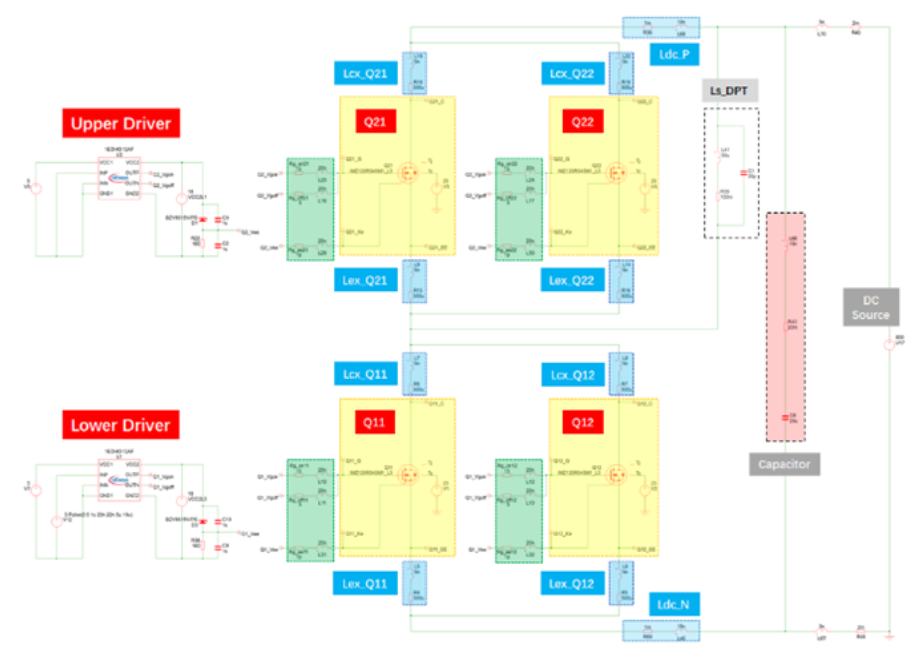

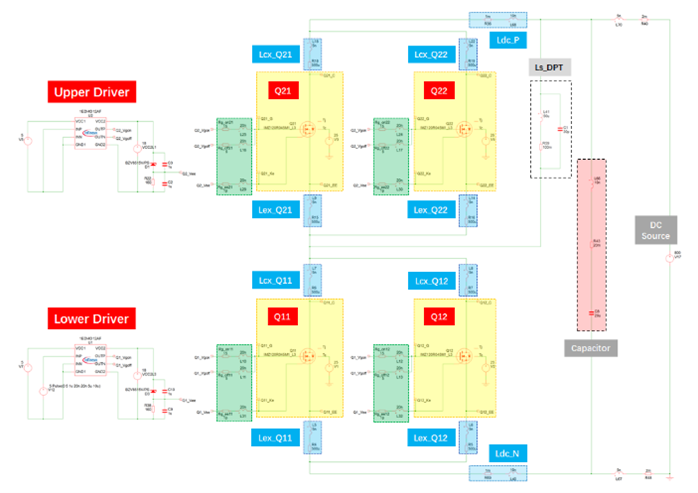

这一结论可以通仿真验证。两个SiC MOSFET并联,给其中一只的漏极和栅极间额外加一个小电容Cgc1,模拟转移电容失配。

栅极网络配置分两种情况,如下表,等效总电阻为Req=2*Rc+Ri,两种情况下都是10Ω。

通过仿真可得开通和关断的波形,虚线为方案1,可见开关瞬间两管间电流偏差较大。第二种方案将共同电阻Rc提升至4Ω,而独立电阻Ri降低至2Ω,如实线所示,动态均流有了很大改善。

并联的器件使用源极电阻Rg,ex、共同栅极电阻Rg,on_com、独立栅极电阻Rg,on之后,总等效电阻为:

其中,Rg,GD为驱动芯片内阻,Rg,int为SiC MOSFET内置门极电阻,n为并联器件的个数。

对于各电阻取值建议:

开尔文源极镇流电阻Rg,ex典型值0.5ohm。

使用分立电阻+功率器件内部电阻约50%,共同电阻+驱动器内阻约50%作为起始值,测试均流与震荡效果,再根据实际结果微调电阻。

门极电阻精度小于1%,尤其在使用低导通电阻器件时。

小结

栅极驱动设计对高速并联至关重要。推荐使用共同电阻、独立电阻以及开尔文源极镇流电阻。

综上所述,SiC MOSFET并联尽管充满挑战,但我们仍有方法可以应对。首先使用参数尽可能一致的管芯,而英飞凌SiC MOSFET因为沟槽栅结构和严格的工艺管控,在各个参数上都具有良好的一致性。其次,系统设计非常重要,驱动回路、功率回路及散热布局要尽可能对称,对性称可以通过交换器件交叉验证。最后,栅极电阻网络的优化设计能够弱化芯片参数失配及布局不对称对均流的影响,推荐同时使用共同电阻、独立电阻以及开尔文源极引脚电阻。

-

芯片

+关注

关注

463文章

54379浏览量

468995 -

MOSFET

+关注

关注

151文章

10759浏览量

234828 -

SiC

+关注

关注

32文章

3847浏览量

70062

发布评论请先 登录

仿真看世界之SiC MOSFET单管的并联均流特性

为何使用 SiC MOSFET

SiC-MOSFET的应用实例

全SiC模块应用要点之缓冲电容器

SiC-MOSFET体二极管特性

SiC-MOSFET功率晶体管的结构与特征比较

SiC-MOSFET与Si-MOSFET的区别

沟槽结构SiC-MOSFET与实际产品

SiC功率器件SiC-MOSFET的特点

浅析SiC-MOSFET

SiC MOSFET单管的并联均流特性

OBC DC/DC SiC MOSFET驱动选型及供电设计要点

SiC MOSFET的并联设计要点

SiC MOSFET的并联设计要点

评论