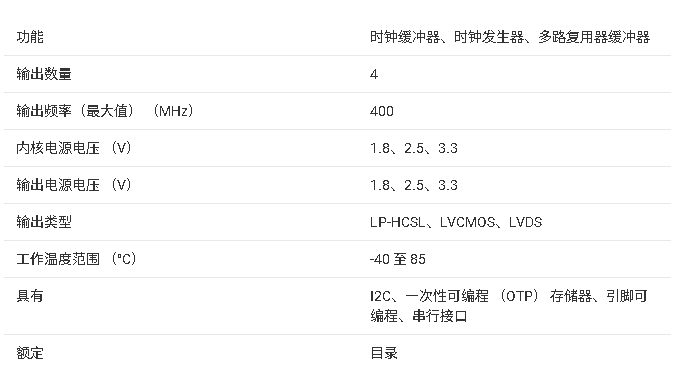

8430S10I-03时钟发生器:Cavium处理器的理想选择

在电子设计领域,时钟发生器对于确保系统的稳定运行至关重要。今天,我们要介绍一款专为Cavium Networks SoC处理器设计的时钟发生器——8430S10I-03,它在满足高性能需求的同时,还具备诸多出色特性。

文件下载:8430S10BYI-03LF.pdf

产品概述

8430S10I-03是一款基于PLL的时钟发生器,专为Cavium Networks SoC处理器量身打造。它能够生成处理器核心参考时钟、DDR参考时钟、PCI/PCI-X总线时钟,以及千兆以太网MAC和PHY的时钟。该设备具有低抖动、低偏斜的时钟输出,其边缘速率轻松满足CN30XX/CN31XX/CN38XX/CN58XX处理器的输入要求。输出频率由25MHz外部输入源或外部25MHz并联谐振晶体产生,扩展的温度范围使其能够满足电信、网络和存储等领域的需求。

应用场景

该时钟发生器适用于多种应用场景,包括使用Cavium处理器的系统、CPE网关设计、家庭媒体服务器、802.11n AP或网关、Soho安全网关、Soho SME网关、无线Soho和SME VPN解决方案、有线和无线网络安全,以及Web服务器和Exchange服务器等。

产品特性

输出接口

- 提供一组可选的差分输出对,适用于DDR 533/400/667,支持LVPECL、LVDS接口电平。

- 拥有九个LVCMOS/LVTTL输出,典型输出阻抗为23Ω。

输入选择

- 可选择外部晶体或差分输入源,晶体振荡器接口设计用于25MHz并联谐振晶体。

- 差分输入对(PCLK,nPCLK)接受LVPECL、LVDS、CML、SSTL输入电平,nPCLK引脚的内部电阻偏置允许用户使用外部单端(LVCMOS/LVTTL)输入电平驱动PCLK输入。

电源模式

提供多种电源模式,包括CORE / OUTPUT为3.3V / 3.3V LVDS、LVPECL、LVCMOS,以及3.3V / 2.5V LVCMOS。

工作温度

环境工作温度范围为 -40°C至85°C,并且提供无铅(RoHS 6)封装。

引脚分配与功能

引脚分配

该设备采用48 TQFP、E-Pad封装,引脚分配清晰明确,涵盖了电源引脚、输入引脚和输出引脚等。

引脚功能

详细的引脚功能在文档中有明确说明,例如:

- VDD为核心电源引脚,用于提供核心电源。

- nOE_D为输入引脚,用于控制Bank D输出的使能,低电平有效。

- nPLL_SEL用于PLL旁路控制,低电平时PLL启用,高电平时PLL旁路。

电气特性

绝对最大额定值

文档中给出了该设备的绝对最大额定值,包括电源电压、输入电压、输出电压和电流等参数。例如,电源电压VDD的最大值为4.6V,输入电压范围为0V至VDD - 0.5V到VDD + 0.5V等。需要注意的是,超过这些额定值可能会对设备造成永久性损坏。

DC电气特性

详细列出了不同电源模式下的DC电气特性,如LVCMOS、LVPECL、LVDS等电源模式下的核心电源电压、模拟电源电压、输出电源电压、电源电流等参数。这些参数对于设计电源电路和评估设备的功耗非常重要。

AC电气特性

包括输出频率、银行偏斜、部分到部分偏斜、RMS相位抖动、周期抖动等参数。这些特性对于确保时钟信号的稳定性和准确性至关重要。例如,在不同的控制输入组合下,输出频率会有所不同,通过合理设置控制输入,可以获得所需的时钟频率。

应用信息

未使用引脚的处理

对于未使用的输入和输出引脚,文档提供了相应的处理建议:

- 对于PCLK/nPCLK输入,若不使用差分输入,可将PCLK和nPCLK浮空,为增加保护,可使用1kΩ电阻将PCLK接地。

- 对于晶体输入,若不使用晶体振荡器输入,可将XTAL_IN和XTAL_OUT浮空,同样可使用1kΩ电阻将XTAL_IN接地。

- 对于LVCMOS控制引脚,由于所有控制引脚都有内部下拉电阻,一般无需额外电阻,但为增加保护,可使用1kΩ电阻。

- 对于LVPECL输出,未使用的LVPECL输出对可浮空,建议不连接走线,差分输出对的两侧应同时浮空或端接。

- 对于LVDS输出,未使用的LVDS输出对可浮空或跨接100Ω电阻,若浮空则不应连接走线。

- 对于LVCMOS输出,所有未使用的LVCMOS输出可浮空,不应连接走线。

差分输入接受单端电平的布线

文档给出了如何将差分输入布线以接受单端电平的建议,通过偏置电阻R1和R2生成参考电压VREF = VDD / 2,旁路电容C1用于过滤DC偏置上的噪声。该偏置电路应尽可能靠近输入引脚,R1和R2的比值可能需要调整以将VREF置于输入电压摆幅的中心。

3.3V LVPECL差分时钟输入接口

PCLK / nPCLK可接受LVPECL、LVDS、CML、SSTL等差分信号,文档给出了不同驱动类型下的接口示例。在实际应用中,若驱动来自其他供应商,应使用其推荐的端接方式,并与供应商确认驱动的端接要求。

晶体接口的过驱动

XTAL_IN输入可通过交流耦合电容接受单端LVCMOS信号,XTAL_OUT引脚可浮空。输入信号的最大幅度不应超过2V,输入边缘速率可低至10ns。通过过驱动晶体振荡器,设备仍可正常工作,但需注意设备性能是通过使用石英晶体来保证的。

输出端接

- 3.3V LVPECL输出端接:LVPECL输出对为低阻抗跟随器输出,需要使用端接电阻或电流源来实现功能。文档给出了两种不同的布局示例,建议板级设计师进行仿真以确保在所有印刷电路和时钟组件工艺变化下的兼容性。

- LVDS驱动端接:标准的LVDS输出结构需要在接收器处并联100Ω电阻,并提供100Ω差分传输线环境。为避免传输线反射问题,100Ω电阻应尽可能靠近接收器放置。

热释放路径

为了最大程度地散热和提高电气性能,需要在印刷电路板(PCB)上的封装焊盘对应位置设计焊盘图案,并通过热过孔将其连接到接地平面。热过孔的数量应根据封装功耗和电导率要求进行确定,建议使用尽可能多的过孔连接到接地,并使用直径为12至13mils(0.30至0.33mm)、1oz铜过孔桶镀的过孔,以避免焊接过程中过孔内的焊料吸锡现象。

应用原理图示例

文档给出了8430S10I-03的应用原理图示例,该示例中设备工作在VDD = VDDA = VDDO_B = VDDO_CD = VDDO_E = VDDO_REF = 3.3V的条件下,使用18pF并联谐振25MHz晶体。为保证频率精度,建议使用负载电容Ci = 18pF和C2 = 18pF,实际应用中可能需要根据PCB布局的寄生参数进行微调。同时,为了实现最佳的抖动性能,需要对电源进行隔离,滤波组件应尽可能靠近电源引脚放置。

功率考虑

功率耗散

文档分别给出了LVCMOS/LVDS输出和LVCMOS/LVPECL输出两种情况下的功率耗散计算方法和示例。总功率耗散为核心功率加上负载功率,不同输出频率下的动态功率耗散也有所不同。通过计算可以评估设备在不同工作条件下的功率需求。

结温

结温Tj直接影响设备的可靠性,最大推荐结温为125°C。通过公式Tj = θJA * Pd_total + TA可以计算结温,其中θJA为结到环境的热阻,Pd_total为设备总功率耗散,TA为环境温度。在计算结温时,需要根据实际情况选择合适的θJA值。

可靠性信息与订购信息

可靠性信息

文档提供了θJA与空气流量的关系表,以及晶体管数量等可靠性信息,这些信息对于评估设备的可靠性和散热设计非常重要。

订购信息

给出了8430S10I-03的订购信息,包括不同的订购编号、标记、封装、运输包装和温度范围等,方便用户进行采购。

总之,8430S10I-03时钟发生器以其出色的性能和丰富的功能,为Cavium处理器的应用提供了可靠的时钟解决方案。在实际设计中,工程师需要根据具体需求合理选择和使用该设备,并严格按照文档中的建议进行设计和布局,以确保系统的稳定运行。你在使用这款时钟发生器的过程中遇到过哪些问题呢?欢迎在评论区分享你的经验和见解。

-

时钟发生器

+关注

关注

1文章

357浏览量

70160

发布评论请先 登录

探索 ICS844201I - 45:PCI Express 时钟发生器的卓越之选

AD9574以太网时钟发生器:设计指南与应用解析

深入解析AD9575:高性能网络时钟发生器的卓越之选

AD9577 时钟发生器:高性能与灵活性的完美结合

AD9522-5:高性能时钟发生器的设计与应用

AD9518-0:高性能6输出时钟发生器的深度剖析

深入剖析AD9516 - 4:高性能时钟发生器的卓越之选

9FGV0441:PCIe Gen 1 - 4应用的低功耗时钟发生器

深入解析LMK03318:超高性能时钟发生器的卓越之选

深入解析PLL1707-Q1:高性能多时钟发生器的理想选择

深入解析RC22112A FemtoClock时钟发生器:高性能与低功耗的完美结合

探索时钟发生器的竞争优势

LMK3H2104 4-Output PCIe时钟发生器技术文档总结

8430S10I-03时钟发生器:Cavium处理器的理想选择

8430S10I-03时钟发生器:Cavium处理器的理想选择

评论