AD9574以太网时钟发生器:设计指南与应用解析

在当今高速发展的电子领域,以太网和千兆以太网技术的应用日益广泛,对于高性能时钟发生器的需求也愈发迫切。AD9574作为一款专为以太网和千兆以太网线卡应用优化的多输出时钟发生器,凭借其卓越的性能和丰富的功能,成为众多电子工程师的理想选择。本文将深入解析AD9574的特性、工作原理、配置方法以及应用场景,为电子工程师在实际设计中提供全面的参考。

文件下载:AD9574.pdf

特性亮点

冗余输入与监控功能

AD9574具备冗余输入参考时钟能力和参考监控功能,这为系统的稳定性和可靠性提供了有力保障。在实际应用中,当一个参考时钟出现故障时,系统可以迅速切换到另一个备用时钟,确保系统的正常运行。同时,参考监控功能可以实时监测参考时钟的频率和相位,及时发现潜在的问题并进行处理。

低抖动与宽频率范围

该时钟发生器在低抖动性能方面表现出色,例如在156.25 MHz时,10 kHz至10 MHz的均方根抖动仅为0.234 ps,12 kHz至20 MHz的均方根抖动为0.243 ps。这种低抖动特性对于高速数据传输和高精度信号处理至关重要,可以有效减少信号失真和误码率。此外,AD9574支持19.44 MHz或25 MHz的输入频率,并能通过预设的频率转换功能提供多种输出频率,满足不同应用的需求。

集成化设计与灵活配置

AD9574采用了完全集成的VCO/PLL核心和集成式环路滤波器,仅需一个外部电容即可完成环路滤波,大大减少了外部元件的数量,降低了设计复杂度和成本。同时,通过PPRx引脚进行设备配置,用户可以根据具体需求灵活选择不同的频率转换、时钟输出功能和输入参考功能,实现个性化的设计。

多种输出驱动格式

该时钟发生器支持HSTL、LVDS、HCSL以及1.8 V和3.3 V CMOS等多种输出驱动格式,能够与不同类型的电路和设备进行良好的匹配,提高了系统的兼容性和灵活性。

工作原理

AD9574的工作原理基于其内部的PLL(锁相环)结构,主要由频率预分频器、PFD(鉴相器)、电荷泵、环路滤波器、VCO(压控振荡器)和反馈分频器等六个功能单元组成。

频率预分频器

频率预分频器通过×2频率乘法器、÷5分频器和多路复用器实现不同的频率分频比,根据PPRx引脚的设置,可提供1/2、1、5/2或5的分频值,为后续的PLL处理提供合适的输入频率。

PLL核心处理

PFD、电荷泵和环路滤波器协同工作,根据输入时钟和反馈时钟的相位差来调整VCO的输出频率。环路滤波器采用部分集成的三阶RC网络,外部通过连接电容或电容与电阻的串联网络来调整PLL的带宽,以确保VCO输出频率稳定在N倍的PFD输入频率(N为反馈分频器的值)。

输出时钟生成

VCO输出的频率经过反馈分频器和输出分频器的处理后,生成所需的输出时钟信号。OUT0和OUT1通道可提供参考频率的副本,OUT0还具备频率加倍选项;OUT2至OUT6通道则通过集成的整数-N PLL实现不同的频率转换,为系统提供多样化的时钟信号。

PPRx引脚配置

AD9574通过七个PPRx引脚进行设备配置,每个引脚控制特定的功能或功能块。通过连接不同阻值的上拉或下拉电阻到PPRx引脚,并根据电阻的阻值和连接方向确定引脚的状态(共8种状态),实现对设备的各种功能配置。

PPR0 - 参考时钟输入配置

PPR0引脚控制参考时钟输入(REF0_x和REF1_x)的配置,可选择单端3.3 V CMOS缓冲模式或差分模式。在单端模式下,可直接连接3.3 V时钟源到正参考输入引脚,同时将负输入引脚通过0.1 nF电容接地;在差分模式下,需将差分时钟驱动器通过0.1 nF电容交流耦合到两个参考输入引脚,也支持单端1.8 V CMOS时钟源连接。

PPR1 - 频率转换设置

PPR1引脚允许用户从预定义的频率转换组中选择,确定OUT4和OUT5通道的输出频率,同时也影响OUT2和OUT3通道的频率。每个PPR1状态对应一组输出频率,具体的频率值和PLL的设置(如×2倍增器状态和PLL带宽)在数据表中详细给出。

PPR2 - OUT0和OUT1配置

PPR2引脚用于配置OUT0和OUT1通道的输出驱动类型和频率缩放因子,可选择HSTL或3.3 V CMOS驱动,输出频率可以是参考频率的1倍或2倍。

PPR3 - OUT4和OUT5配置

PPR3引脚根据PPR1确定的频率对,选择OUT4和OUT5通道的具体输出频率和输出驱动类型,提供了多种组合选项。

PPR4 - OUT6配置

PPR4引脚用于配置OUT6通道的输出频率和驱动类型,但该通道的配置与PPR1状态相关,在PPR1状态2至7时,OUT6通道将被禁用。

PPR5 - 参考监控阈值

PPR5引脚控制参考频率监控的误差阈值,以ppm(百万分之一)为单位,可设置为±25、±10、±50或±100 ppm,用于实时监测参考时钟的频率准确性。

PPR6 - 监控时钟(MCLK_x)输入配置

PPR6引脚控制MCLK_x输入的配置,包括输入频率和输入类型(单端3.3 V CMOS或差分),可选择0.008 MHz、10 MHz、19.44 MHz、25 MHz或38.88 MHz的固定频率输入。

应用场景与设计要点

双振荡器参考输入应用

在双振荡器参考输入应用中,使用两个晶体振荡器作为参考输入,同时提供一个稳定的振荡器源作为MCLK_x输入,用于参考监控功能。通过FPGA进行控制接口的管理,实现对参考状态和PLL锁定状态的监测,并根据需要进行参考切换。在设计时,需根据实际需求选择合适的PPRx状态,通过连接相应的编程电阻来实现。

单振荡器参考输入应用

对于简单的单振荡器参考输入应用,使用一个晶体振荡器作为参考输入,参考监控功能相对简化。通过将REF_FHI和REF_FLO引脚进行线或连接,并将REF_MON接地,可实现参考存在检测功能。同样,通过设置PPRx状态来配置AD9574的工作模式。

时钟输出接口设计

在与不同类型的时钟输出接口进行连接时,需要注意以下几点:

- CMOS时钟输出:尽量设计点对点网络,使驱动器只有一个接收器,以简化终端方案并减少阻抗不匹配引起的振铃。通常需要在源端进行串联终端匹配,串联电阻值根据板设计和时序要求而定,一般在10 Ω至100 Ω之间。同时,为了保证信号的上升/下降时间和信号完整性,建议CMOS输出的走线长度小于6英寸。

- LVDS和HSTL时钟输出:LVDS和HSTL采用差分输出驱动器,推荐使用图中所示的终端电路进行匹配,以确保信号的稳定传输。

- HCSL时钟输出:HCSL采用差分开漏架构,需要使用外部终端电阻。在某些情况下,为了减少过冲和振铃,可在传输线路中串联一个10 Ω至30 Ω的小电阻。

电源与热设计

AD9574需要3.3 V ± 10%的电源供应,在PCB设计中,应遵循良好的工程实践,合理布局电源走线和接地平面。在电源引脚附近使用足够的旁路电容(如0.1 µF),并在PCB上对电源进行充分的去耦(>10 μF)。此外,AD9574封装的外露金属焊盘需要正确接地,以提供良好的散热路径。根据热性能参数表,可以计算在不同气流条件下的结温,必要时可使用气流源来确保结温不超过规定值。

总结

AD9574以其高性能、高集成度和灵活的配置能力,为以太网和千兆以太网应用提供了可靠的时钟解决方案。电子工程师在设计过程中,需要深入理解其工作原理和配置方法,根据具体的应用场景和需求,合理选择PPRx状态,优化时钟输出接口设计,并注意电源和热设计,以确保系统的稳定运行和高性能表现。希望本文能为电子工程师在使用AD9574进行设计时提供有益的参考和指导。你在实际应用中是否遇到过类似时钟发生器的配置难题?你是如何解决的呢?欢迎在评论区分享你的经验和见解。

-

设计应用

+关注

关注

0文章

212浏览量

5266 -

ad9574

+关注

关注

0文章

5浏览量

4105

发布评论请先 登录

深入解析ADF4360 - 9时钟发生器PLL:设计与应用的全面指南

AD9540:高性能低抖动时钟发生器的深度解析

8430S10I-03时钟发生器:Cavium处理器的理想选择

AD9572:高性能光纤通道/以太网时钟发生器IC的深度解析

解析AD9571:以太网时钟发生器的卓越之选

AD9524:高性能时钟发生器的深度剖析与应用指南

AD9520-3:高性能时钟发生器的深度解析与应用指南

AD9520-4:高性能时钟发生器的深度解析与应用指南

AD9518-2:6输出时钟发生器的详细解析与应用指南

AD9517-1:高性能12输出时钟发生器的深度解析

AD9520-0:高性能时钟发生器的深度解析与应用指南

深入解析 CDC421Axxx:高性能低抖动时钟发生器

LMK03806:超低抖动时钟发生器的技术解析与应用指南

探索时钟发生器的竞争优势

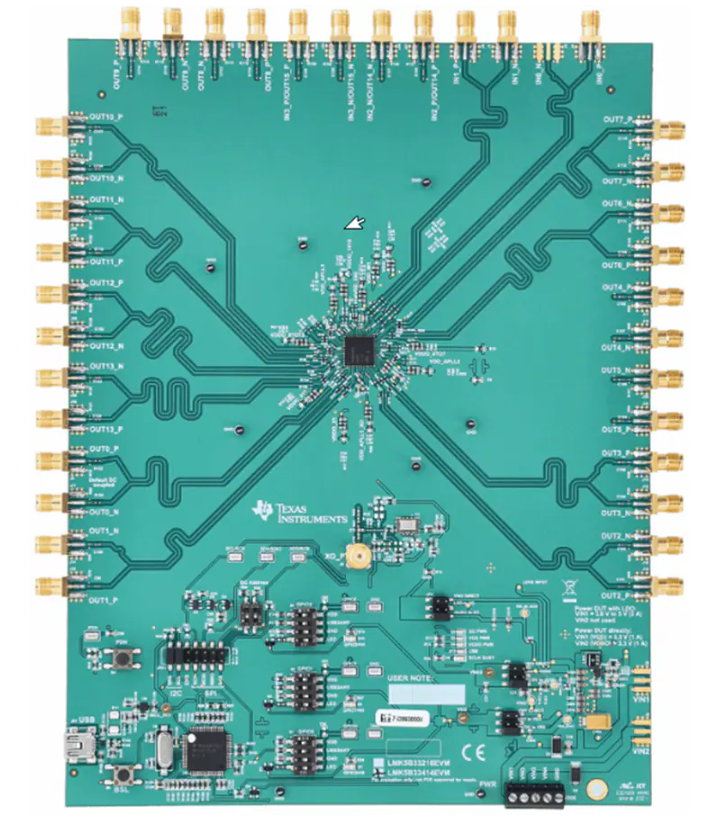

LMK5B33414EVM网络时钟发生器评估模块技术解析

AD9574以太网时钟发生器:设计指南与应用解析

AD9574以太网时钟发生器:设计指南与应用解析

评论