基于非线性电容特性的 SiC MOSFET 开关损耗解析模型建立

碳化硅功率器件技术背景与非线性建模的必要性

在现代电力电子变换器系统的演进过程中,对更高能量转换效率、更小无源器件体积以及更高功率密度的极致追求,正在深刻重塑功率半导体器件的底层材料格局。碳化硅(Silicon Carbide, SiC)作为第三代宽禁带(Wide Bandgap, WBG)半导体的杰出代表,其临界击穿电场强度是传统硅(Si)材料的十倍,热导率是硅的三倍,且具备两倍于硅的饱和电子漂移速度与三倍的禁带宽度 。这些卓越的材料学物理特性,使得 SiC 金属氧化物半导体场效应晶体管(MOSFET)能够在极高的漏源电压阻断条件下,依然保持极其微小的特定导通电阻(RDS(on))和极低的寄生电容 。相较于传统的硅基绝缘栅双极型晶体管(IGBT),SiC MOSFET 属于单极型器件,在开关瞬态过程中不存在少数载流子的复合与拖尾电流现象,因此具备在数百千赫兹(kHz)乃至兆赫兹(MHz)频段运行的巨大潜力 。倾佳电子力推BASiC基本半导体SiC碳化硅MOSFET单管,SiC碳化硅MOSFET功率模块,SiC模块驱动板,PEBB电力电子积木,Power Stack功率套件等全栈电力电子解决方案。

基本半导体代理商倾佳电子杨茜致力于推动国产SiC碳化硅模块在电力电子应用中全面取代进口IGBT模块,助力电力电子行业自主可控和产业升级!

然而,要将 SiC 器件级别的物理优势真正转化为变换器系统级别的性能提升,电力电子设计工程师面临着极为严峻的挑战。随着开关速度的成倍提升(极高的 dv/dt 和 di/dt),器件在极短开关瞬态过程中的电磁行为变得异常复杂。印制电路板(PCB)走线引入的寄生电感、器件封装内部的杂散电感,以及最关键的器件内部高度非线性的寄生结电容,三者之间产生强烈的耦合与谐振 。在以往的常规工程设计中,通常采用基于数据手册提供的静态电容值进行线性近似计算。这种线性模型在评估低速硅器件时误差尚可接受,但在评估具有极强非线性电容特征的 SiC MOSFET 时,往往会导致高达百分之二十以上的开关损耗评估误差 。不准确的损耗模型不仅会导致变换器散热系统设计过度或余量不足,更无法准确预测由极高 dv/dt 引发的桥臂串扰(Crosstalk)和寄生导通(False Turn-on)现象 。

为了实现电力电子变换器的全局最优设计,并在诸如电动汽车(EV)牵引逆变器、高频谐振变换器等对体积和重量极为敏感的应用场景中精确把控热应力,建立一个综合考虑多重寄生参数与高度非线性结电容的 SiC MOSFET 开关损耗解析模型(Analytical Model)显得尤为迫切 。解析模型相比于底层物理模型(如 TCAD 有限元模型)或复杂的行为级仿真模型(如 SPICE 模型),能够在保持极高计算精度的同时,将单一工作点的计算时间缩短至毫秒级别,从而完美契合系统级多目标优化算法在广阔工作范围内的海量迭代需求 。

寄生结电容的物理溯源与非线性数学表征

要构建高精度的瞬态解析模型,首先必须对 SiC MOSFET 内部寄生电容的物理起源及其随施加电压动态变化的非线性规律进行严密的数学表征。在功率 MOSFET 的结构中,由于栅极多晶硅被一层极薄的二氧化硅绝缘层完全隔离,并在半导体基体中形成了复杂的立体空间结构,器件内部天然存在着三个核心的极间电容:栅源电容(Cgs)、栅漏电容(Cgd)和漏源电容(Cds) 。

在器件制造商发布的数据手册中,为了便于标准化测试与标注,通常提供的是宏观的端口等效电容参数,即输入电容(Ciss)、输出电容(Coss)和反向传输电容(Crss,亦即著名的米勒电容)。这三者与内部物理结电容之间遵循严格的代数加和关系:输入电容由栅源电容与栅漏电容并联构成,即 Ciss=Cgs+Cgd;输出电容由漏源电容与栅漏电容并联构成,即 Coss=Cds+Cgd;而反向传输电容则完全等同于栅漏电容,即 Crss=Cgd 。由于栅源电容 Cgs 主要由固定的栅极氧化层厚度和几何重叠面积决定,其容量在整个漏源电压摆动过程中基本保持恒定,受电压变化的影响微乎其微 。

与此形成鲜明对比的是,栅漏电容 Cgd 和漏源电容 Cds 表现出极其强烈的电压依赖性。这两个电容的本质是半导体材料内部垂直 p-n 结的耗尽层电容。当漏源电压(vds)较低时,耗尽层极其狭窄,此时表现出的电容值巨大;而当 vds 迅速上升时,耗尽层迅速向低掺杂的漂移区深处扩展,导致等效电极间距增大,电容值随之呈指数级暴跌 。在 SiC MOSFET 的实际开关轨迹中,这种电容的动态变化比率可达百倍之巨(例如从 0V 到 800V 的区间内),这种强烈的非线性是引起电流电压波形畸变、开关时间延长以及损耗骤增的根本物理诱因 。

为了在解析微分方程中准确再现这一非线性动态过程,学术界与工业界广泛采用幂律(Power Law)方程对随电压变化的 Coss 和 Crss 进行全局曲线拟合 。该非线性电容函数的标准解析表达式可以写为:

C(vds)=(1+Vbvds)rC0+C1

在该公式中,C0 表征了在极低偏置电压(逼近 0V)下,因耗尽层极薄而呈现出的巨大初始本底电容;Vb 是一项与半导体材料内建电势(Built-in Potential)紧密相关的拟合电压参数;指数 r 决定了电容随电压衰减的陡峭程度,其物理意义与外延层掺杂浓度的空间分布梯度息息相关(例如,突变结的 r 接近 0.5,而缓变结则有所不同);C1 则代表在极高漏源电压下,耗尽层完全展开后所残留的微小高压渐近电容值 。通过提取数据手册中提供的 Coss−vds 和 Crss−vds 对数坐标曲线数据,并应用最小二乘法等数值拟合手段,可以精确提取出 C0、Vb、r 和 C1 这四个关键拟合系数,从而为后续的积分运算提供连续、平滑且精确的数学函数输入 。

能量相关电容与时间相关电容的积分推导及其应用边界

尽管非线性幂律方程在微分方程求解中具有不可替代的高精度,但在工程界快速计算开关损耗和谐振腔参数时,设计人员往往更希望将非线性电容等效为一个恒定的标量电容值。这就引出了现代 SiC MOSFET 数据手册中两个极易混淆且至关重要的参数:能量相关有效输出电容(Co(er))与时间相关有效输出电容(Co(tr)) 。

时间相关有效输出电容 Co(tr) 的物理定义是:假设存在一个固定的理想电容,当使用恒定电流对其进行充电,使其端电压从零上升到给定的直流测试电压(通常为额定电压的 80% 或数据手册指定的电压,如 800V 或 400V)时,所需的充电时间与向实际非线性电容 Coss(vds) 充电所需的时间完全一致 。根据电荷守恒定律(Q=I⋅t),充电时间相等意味着在指定电压窗口内积累的总位移电荷量必须完全相等。因此,Co(tr) 的本质是输出电容在指定电压跨度内的电荷等效平均值,其积分推导公式为:

Co(tr)=VDS1∫0VDSCoss(v)dv=VDSQoss

在变换器设计中,Co(tr) 主要用于评估基于恒流充放电特性的时序参数。例如,在设计 LLC 谐振变换器或移相全桥(PSFB)变换器时,为了确保器件在导通前能够完全抽干漏源极之间的电荷以实现零电压开通(ZVS),设计者必须基于 Co(tr) 来计算死区时间(Dead-time)的下限 。使用 Co(tr) 可以确保死区时间的设定既能安全避免桥臂直通,又不会因为死区过长导致体二极管过度导通而增加损耗 。

与此相对应,能量相关有效输出电容 Co(er) 的物理定义是:在从零电压充电至相同指定的直流电压时,该固定电容所存储的电场能量,必须与实际非线性电容 Coss(vds) 所积累的总能量绝对相等 。非线性电容器中存储的能量等于电荷关于电压的积分,因此 Co(er) 的严谨推导公式为:

Co(er)=VDS22∫0VDSv⋅Coss(v)dv=VDS22⋅Eoss

在硬开关(Hard-switching)电力电子拓扑(如标准的两电平逆变器、Boost 升压 PFC)的损耗解析模型中,必须严格采用 Co(er) 或直接使用数据手册提供的储能参数 Eoss。这是因为在器件强制开通的瞬间,先前在关断期间储存在输出电容中的能量 Eoss 将无可避免地通过晶体管的内部导电沟道释放,并完全转化为热能散失。这一机制构成了硬开关导通损耗(Eon)中不可逾越的物理底线 。若在计算硬开关损耗时错误地代入了为了计算死区时间而设定的 Co(tr),将导致计算出的容性放电损耗与实际情况产生巨大偏差。这也正是精确的瞬态解析模型必须内置电容-电压积分引擎,而不能简单套用单一电容标量值的原因所在 。

开尔文源极封装技术与寄生电感耦合效应的解析

构建精确的开关损耗解析模型,必须将目光从器件内部裸管芯(Bare Die)延伸至其外部的物理封装层。在高频开关环境下,由芯片引线键合(Wire Bonding)、封装管脚以及外部 PCB 走线所不可避免引入的杂散电感(Stray Inductance),对动态开关轨迹起到了决定性的重塑作用 。在传统的 TO-247-3 三引脚封装中,功率主回路的源极与栅极驱动回路的源极被迫共用同一段引脚,这段重合的物理路径不可避免地引入了共源极寄生电感(Common-Source Inductance, Ls) 。

在解析模型中列写驱动回路的基尔霍夫电压方程(KVL)时,可以清晰地看到共源极电感的破坏性干预。当驱动芯片发出高电平信号 Vdrive 驱动 SiC MOSFET 开通时,漏极电流 id 开始以极高的斜率攀升(即 did/dt>0)。根据法拉第电磁感应定律,在共源极电感 Ls 上会诱发一个极性为上正下负的感生电动势 vLs=Ls⋅dtdid 。这一瞬态压降直接串联在栅源极真实驱动环路中,导致施加在芯片内部真实栅极与源极之间的有效驱动电压 vgs(effective) 被严重削弱:

vgs(effective)=Vdrive−ig⋅Rg(total)−Lsdtdid

这种典型的物理负反馈机制(Degenerative Feedback)极大地抑制了漏极电流的爬升速率,强行拉长了电流上升与电压下降的交叉重叠时间,进而导致开关损耗呈指数级恶化 。在关断瞬态时,负反馈效应同样会阻碍漏电流的快速下降,延长拖尾时间。

为了从根本上消除这一电气缺陷,业界顶尖的功率器件制造商(如本模型选取的 BASiC Semiconductor 基本半导体)在其高性能 SiC MOSFET 产品线中全面引入了带开尔文源极(Kelvin Source)的四引脚封装技术(如 TO-247-4、TO-247-4L 或 TO-247PLUS-4) 。开尔文源极封装的精妙之处在于,其通过一条完全独立的引线直接连接到内部芯片表面的源极金属焊盘,专门且仅用于返回驱动回路的充放电电流,从而在物理结构上彻底切断了主功率大电流与控制弱电流的共用路径 。

在采用开尔文源极的瞬态解析模型中,驱动环路的电压方程得到了极大的净化,上述负反馈项 Lsdtdid 被彻底剔除 。模型的解析解表明,此时决定漏源电流变化率的因素,仅仅剩下驱动器的输出电压、外部与内部栅极电阻之和(Rg_ext+Rg_int)、输入寄生电容以及器件自身的本征跨导(gfs)。这种物理层面的解耦使得 SiC 器件能够真正释放其材料极限,展现出极其陡峭的瞬态边沿,大幅削减交叉损耗,进而支撑系统向更高的开关频率与更高的功率密度挺进 。

导通瞬态(Turn-on Transient)的高精度分段解析建模

解析模型的核心算法逻辑是将极端非线性的复杂开关瞬态,沿着时间轴严密切割为若干个边界条件明确、物理状态连续的离散子阶段(Sub-stages)。在每一个子阶段内,根据器件是否处于截止区、饱和区或线性区,列写相应的电路微分方程组并求取闭式解(Closed-form Solutions) 。对于典型的感性负载钳位硬开关电路,导通瞬态可精细划分为以下核心阶段:

第一阶段:导通延迟阶段(Turn-on Delay Time, td(on))

在 t=t0 时刻,驱动器输出端突跃至正向驱动电压 Vdr。此时 SiC MOSFET 的栅源电压 vgs 处于关断状态的零电位或负偏压,沟道尚未反型,漏电流 id 为零。外部负载感性电流 IL 完全由对侧的续流二极管(Freewheeling Diode, FWD)承载。由于漏源电压 vds 被坚如磐石的母线电压 VDC 牢牢钳位,Cgd 和 Cds 处于稳态的高压极小值状态。此阶段的电路实质上是一个由总驱动电阻 RG,on 对静态输入电容 Ciss 充电的一阶非线性 RC 响应过程 。当 vgs 逐渐攀升并精确触碰到器件的栅极阈值电压 Vth 时,该阶段宣告结束。其延迟时间可由标准对数方程解析求得:

td(on)=RG,on⋅Ciss⋅ln(Vdr−VthVdr−Vgs(initial))

由于此阶段沟道依然闭锁,id 维持为零,故并未产生实质性的开关交叉损耗,但其精确计算对于评估死区时间余量和数字控制器发波补偿具有指导意义 。

第二阶段:电流上升阶段(Current Rise Time, tri)

一旦 vgs 跨越 Vth 门槛,导电沟道瞬间打通,漏极电流 id 开始以前所未有的斜率急速攀升 。此阶段的终点定义为 id 完全接管负载电感电流 IL。在整个电流上升区间内,由于对侧续流二极管尚未恢复阻断能力,漏源极电压 vds 仍然被迫钳位于母线电压 VDC 不变。因此,位移电流的流向完全聚焦于栅极控制环路。器件此时运行在饱和放大区,沟道电流的微观控制遵循跨导方程 ich=gfs(vgs−Vth)。 需要特别指出的是,高度精确的解析模型必须在此引入漏极诱导势垒降低(Drain-Induced Barrier Lowering, DIBL)效应及短沟道效应对跨导 gfs 的动态调制 。由于 vds 处于高压极值状态,强电场侵入沟道导致实际有效跨导发生漂移。将电路 KVL 与跨导方程联立求解,并忽略非开尔文封装中的 Ls 负反馈效应,可推导出电流上升时间的闭式解析式:

tri=−RG,on⋅Ciss⋅ln(1−gfs(Vdr−Vth)IL)

在这一极其短暂的时间窗口内,高昂的电压 VDC 与持续增长的电流 id 发生深度重叠,贡献了导通损耗的第一部分核心能量 。

第三阶段:电压下降阶段(Voltage Fall Time, tfu)

当 id 达到并微弱超越 IL 时,续流二极管中的少数载流子被抽干并开始承受反向阻断电压,SiC MOSFET 的漏源电压 vds 开始从 VDC 向导通压降 Vds(on) 极速俯冲 。在这个电压断崖式下跌的区间内,栅源电压 vgs 停止上升,被死死钳位在一个被称为米勒平台(Miller Plateau Voltage)的恒定电位上:Vmil=Vth+IL/gfs 。由于 vgs 恒定不动,驱动器提供的所有瞬态电流 ig=RG,onVdr−Vmil 均被强制用于抽取米勒电容 Cgd 上的位移电荷 。

这一阶段的解析建模是最具挑战性且最能体现非线性模型价值的核心环节。由于 vds 从高压迅速滑落至近乎 0V,Cgd(vds) 的电容值将经历几百倍的非线性暴涨。如果在这个积分阶段依然采用常数等效电容,计算出的电压下降时间 tfu 将严重偏离物理事实。高精度的解析模型必须将先前推导的幂律电容函数代入微分方程中进行时间域或电压域的连续积分 :

tfu=Vdr−VmilRG,on∫Vds(on)VDCCgd(v)dv=Vdr−VmilRG,on⋅Qgd,dy

此外,物理机制的深层剖析表明,vds 的急速下降不仅需要外部驱动抽取 Cgd 的电荷,同时还会迫使输出电容 Coss(涵盖 Cds)以及对侧二极管结电容同步放电 。这些巨大的动态位移电流必须通过 SiC MOSFET 的导电沟道泄放,这意味着在此阶段,沟道内部流淌的实际瞬态电流远大于外部可测的负载电流 IL。这一被忽视的微观电流浪涌,是导致电压下降期重叠损耗激增的关键元凶 。

最终,导通总能量损耗 Eon 可以通过对时域电压电流的乘积进行严格积分,并计入本管输出电容能量 Eoss 和对侧二极管反向恢复能量 Err 获得解析表达式 :

Eon=21VDCIL(tri+tfu)+Eoss+Err

对于 SiC 系统而言,由于采用了肖特基势垒二极管(SBD),无少子注入效应,因此 Err 极小,导通损耗的优化极限几乎完全受制于 Eoss 。

关断瞬态(Turn-off Transient)的非对称性解析与能量流转

关断瞬态的物理过程看似是导通瞬态的逆向回放,但在内在能量的转换路径与非线性边界条件的响应上,表现出深刻的非对称特征(Asymmetry) 。这种非对称性的根源在于米勒阶段不同的栅极驱动电流(IGD)充放电能力,以及非线性电容在上升和下降沿对位移电流截然不同的吞吐表现 。

关断延迟与电压上升阶段(td(off) 与 tru)

当驱动信号指令转为零电位或负偏压 Vdr,off 时,首先经历极短的关断延迟 td(off),输入电容电荷泄放,栅压降至新的关断米勒平台 Vmil_off 。随后进入至关重要的电压上升阶段(Voltage Rise Time, tru)。在此期间,沟道电流依然等于负载电流 IL,vds 则从极低的 Vds(on) 冲刺至母线阻断电压 VDC 。解析模型在此处必须同样执行非线性电容的逆向积分:

tru=Vmil_off−Vdr,offRG,off∫Vds(on)VDCCgd(v)dv

在 vds 上升的过程中,部分由电源和负载电感抽取的能量并非全部在沟道内转化为致热的耗散功率,而是被作为静电场能量重新存储回了快速充电的 Coss 之中 。这在能量层面上形成了强烈的缓冲作用。

电流下降阶段(tfi)与关断总损耗评估

当 vds 达到 VDC 后,负载电流平滑转移至对侧续流二极管,SiC MOSFET 的 id 开始断崖式回落,标志着电流下降阶段 tfi 的开始。此阶段的长短受制于栅极回路放电至阈值电压 Vth 的时间常数 。

综合考量能量的流向,高精度解析模型在计算总关断损耗 Eoff 时,必须从传统的 v⋅i 乘积时间积分中,严格剥离掉被电容网络吸收的静电场能量,即执行 −Eoss 的操作 。数学表达式如下:

Eoff=21VDCIL(tru+tfi)−Eoss

这深刻解释了为何在部分极高频轻载工况下,器件通过热量测量评估的真实关断损耗往往远低于传统仪器直接测量的积分视在损耗 。

半桥拓扑中的动态串扰效应(Crosstalk)与抑制机制

解析模型在评估半桥(Half-Bridge)或相桥(Phase-leg)拓扑时,必须将另一侧互补开关管的状态纳入全局方程矩阵中,以精确量化高压高速摆率引发的动态串扰效应(Crosstalk) 。

当桥臂中某一侧 SiC MOSFET 极速导通,导致开关节点(Switching Node)电位发生剧烈跳变时,处于关断状态的另一侧 MOSFET 将被迫承受极高的正向 dv/dt 冲击 。根据麦克斯韦电磁场理论,快速变化的电压会在互补器件的米勒电容 Cgd 两端引发强烈的位移电流,其解析模型可表述为:

iMiller=Cgd(v)⋅dtdvds

这股势如破竹的米勒电流无处遁形,只能通过外部驱动回路电阻 RG 和内部寄生电阻注入到源极,从而在关断器件的栅源极两端强制感生出一个正向的毛刺电压:

vgs(spike)=iMiller⋅RG+LgdtdiMiller

如果这个由 dv/dt 诱发的尖峰电压跨越了器件自身的安全阈值电压 VGS(th),原本关断的器件将被瞬间错误开启(False Turn-on),导致整个桥臂发生灾难性的直通(Shoot-through)短路 。即使直通时间极其短暂不足以烧毁器件,这种寄生现象也会在每一次开关周期中凭空注入巨大的瞬态直通电流,使系统开关损耗飙升 。

通过解析模型的敏感度分析可以得出,抑制串扰的有效路径主要有三条:一是选用 Crss/Ciss 本征比值极小的器件,从物理层面掐断米勒耦合通道 ;二是采用具备米勒钳位(Active Miller Clamp)功能的隔离驱动芯片(如前文述及的 BTD25350 驱动芯片 ),在关断期间提供极低阻抗的旁路通路;三是在关断期间施加适当的负向偏置电压(如 -4V 或 -5V),为误导通尖峰预留充足的电压缓冲余量 。

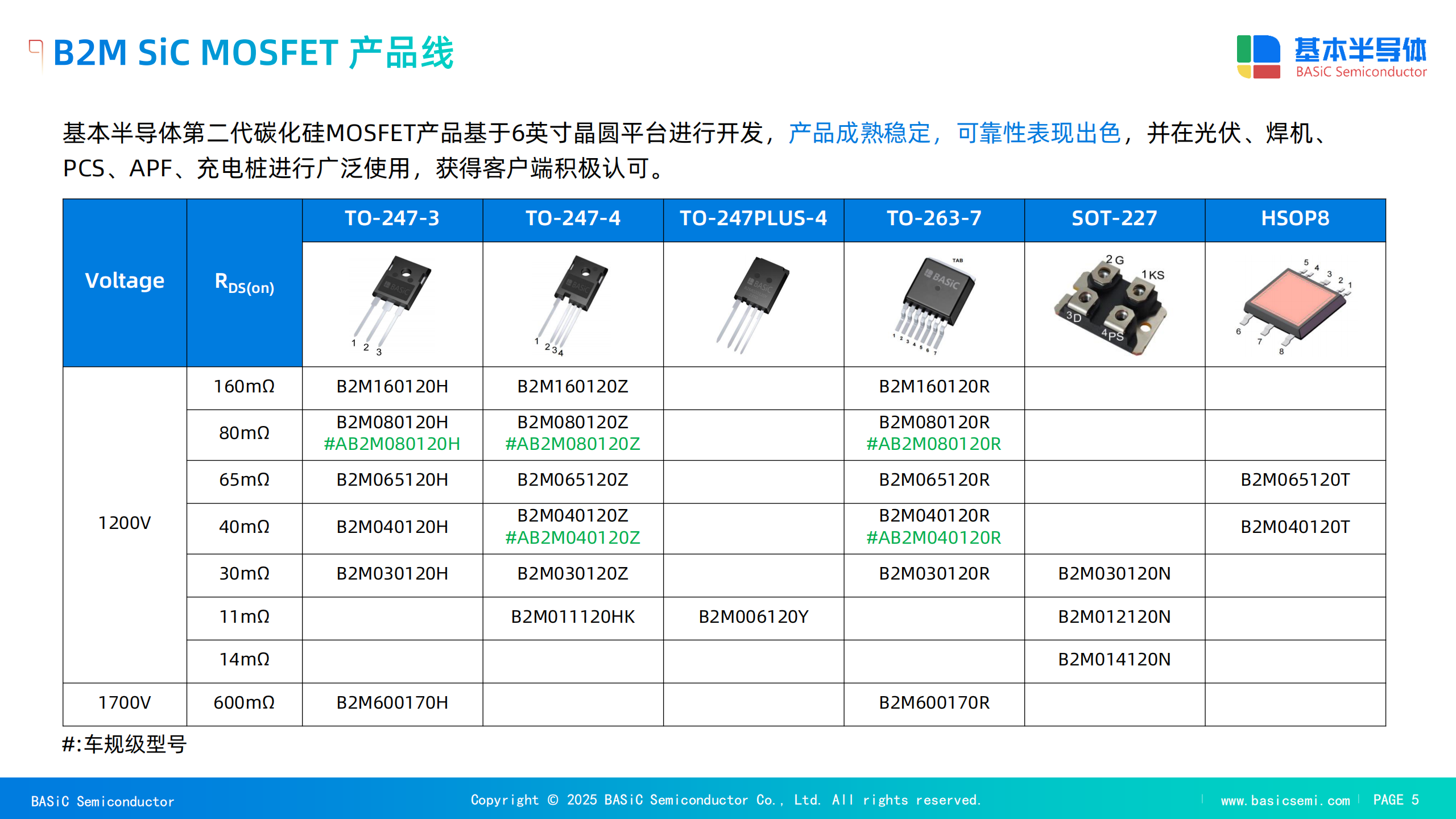

基于基本半导体(BASiC Semiconductor)产品阵列的实证深度解析

为了确保理论解析模型具有切实可行的工业落地能力,必须将其置入真实的商用器件参数矩阵中进行宏观验证与微观适配。以下详尽汇总了从基本半导体(BASiC Semiconductor)新一代 SiC MOSFET 官方技术手册中提取的、涵盖不同耐压等级与电流规格的典型器件参数 。该系列器件广泛支持面向电动汽车电机驱动、光伏逆变与高频储能系统的应用需求 。

宏观电气特性与静态参数矩阵综合概览

(所有参数除特别注明外,均提取自 TJ=25∘C 标准静态环境 )

| 核心器件型号 | 漏源耐压 VDSmax (V) | 连续漏极电流 ID (A) @TC=25°C | 典型导通电阻 RDS(on) (mΩ) | 典型阈值电压 VGS(th) (V) | 跨导特性 gfs (S) | 推荐驱动偏压 VGSop (V) | 封装工艺架构 |

|---|---|---|---|---|---|---|---|

| B3M006C120Y | 1200 | 443 | 6 | 不适用 | 96 | -5 / +18 | TO-247PLUS-4 |

| B3M011C120Z | 1200 | 223 | 11 | 2.7 | 48 | -5 / +18 | TO-247-4 |

| B3M013C120Z | 1200 | 180 | 13.5 | 2.7 | 38 | -5 / +18 | TO-247-4 |

| B3M020120ZN | 1200 | 127 | 20 | 2.7 | 28 | -5 / +18 | TO-247-4NL |

| B3M035120ZL | 1200 | 81 | 35 | 2.7 | 19 | -5 / +18 | TO-247-4L |

| B3M040120Z | 1200 | 64 | 40 | 2.7 | 16 | -4 / +18 | TO-247-4 |

| B3M010C075Z | 750 | 240 | 10 | 2.7 | 46 | -5 / +18 | TO-247-4 |

| B3M025065Z | 650 | 111 | 25 | 2.7 | 22 | -5 / +18 | TO-247-4 |

| B3M040065Z | 650 | 67 | 40 | 2.7 | 10 | -4 / +18 | TO-247-4 |

注:上述阈值电压 VGS(th) 普遍经历了 1ms 的 20V 脉冲预处理条件,以消除表面态俘获电荷对测量的动态干扰 。在 TJ=175∘C 的高温极限工况下,上述器件的阈值电压普遍展现出负温度系数,漂移下降至 1.9V 典型值区间 。

高频交流与寄生电容特性深度映射矩阵

为了服务于解析模型中至关重要的时序与能量积分计算,以下梳理了器件的交流(AC)表征参数。测试统一基准定为 VGS=0V, f=100kHz,VAC=25mV,对于 1200V 系列测试偏压定为 VDS=800V;对于 750V 级别定为 VDS=500V;对于 650V 级别定为 VDS=400V 。

| 核心器件型号 | 输入静电容 Ciss (pF) | 输出非线性电容 Coss (pF) | 米勒反向传输电容 Crss (pF) | 寄生本征米勒比值 (Crss/Ciss) | 额定测试偏压 VDS 下的能量 Eoss (µJ) | 结壳热阻 Rth(j−c) 典型值 (K/W) |

|---|---|---|---|---|---|---|

| B3M006C120Y | 12000 | 500 | 24 | ~0.20% | 212 | 0.08 |

| B3M011C120Z | 6000 | 250 | 14 | ~0.23% | 106 | 0.15 |

| B3M013C120Z | 5200 | 215 | 14 | ~0.27% | 90 | 0.20 |

| B3M020120ZN | 3850 | 157 | 10 | ~0.26% | 65 | 0.25 |

| B3M035120ZL | 2320 | 100 | 8 | ~0.34% | 38 | 0.38 |

| B3M040120Z | 1870 | 82 | 6 | ~0.32% | 33 | 0.48 |

| B3M010C075Z | 5500 | 370 | 19 | ~0.35% | 59 | 0.20 |

| B3M025065Z | 2450 | 180 | 9 | ~0.37% | 20 | 0.38 |

| B3M040065Z | 1540 | 130 | 7 | ~0.45% | 12 | 0.60 |

实验数据的二次物理推演与模型指导价值

深度透视上述涵盖多个代差与物理面积的器件群组,可以从中萃取出极具工程指导意义和解析模型验证价值的宏观趋势:

首先,半导体物理面积与电容特性的残酷博弈在数据中展露无遗。为了实现 1200V 下惊人的 6mΩ 超低导通电阻(如 B3M006C120Y 型号),制造商必须极大地扩张芯片内并联的晶胞数量(Cell Density)与总有源区面积 。这一物理行为的直接代价是其输入电容 Ciss 飙升至 12000pF,等效储能 Eoss 高达 212μJ 。在应用解析模型对这类大功率巨无霸器件进行导通时间 td(on) 和开通能量 Eon 的求解时,巨大的 Ciss 将导致传统弱驱动方案下的门极充电曲线严重平缓化,引发极具破坏性的过渡阶段热耗散 。这就为系统设计工程师提供了一个强烈的定性结论:在这类旗舰级低阻值器件上,绝不可仅仅匹配常规的驱动器,而必须采用高电流峰值(Peak Current)乃至具备强化型负压关断能力的外围电路,以在解析公式中强行缩减 tri 乘积项。

其次,极端优化的微型化米勒比率设计成为了抗击高频串扰的定海神针。仔细观察上述电容矩阵可以发现,无论是面向高压大电流的 1200V / 6mΩ,还是面向紧凑型中功率的 650V / 40mΩ 器件,基本半导体的产品普遍展现出令人惊叹的极低 Crss 绝对值(从 6pF 到仅 24pF) 。更为关键的是,其本征米勒比值(Crss/Ciss)被死死压制在了不到 0.5% 的极度优异范围内。在前面的串扰(Crosstalk)理论解析中提及,引发桥臂误导通的源头在于强 dv/dt 带来的转移位移电流 。这样苛刻的电容比例管控,使得该器件群即使在恶劣的快速开关操作下,反向传输回栅极的电荷积分也被降到了最低限度。解析模型能够明确预测,使用此类器件的变换器将享有更宽广的安全工作区(Safe Operating Area, SOA),并允许激进地减小外部死区时间和关断负偏压。

再者,热力学性能的封装革命与高级互连技术在散热参数上留下了深刻印记。例如对于 B3M010C075Z(750V / 10mΩ)这类用于极高频和严苛散热环境的器件,其结壳热阻 Rth(j−c) 被标注为典型值 0.20K/W 。这种极低的热阻水平,正是得益于银烧结(Silver Sintering)这类前沿晶圆级互连工艺的大规模应用 。传统软钎焊(Solder)在大温波冲击下极易产生热疲劳导致热阻恶化,而银烧结技术能够实现芯片背金到 DBC 基板的近乎原子级熔合,不但使得导热率成倍提升,更赋予了器件更强悍的短路雪崩耐量。对于数字孪生控制算法而言,解析模型中基于环境温度和热阻网络计算得到的瞬态结温(Tj),其收敛速度和峰值预估将因这种极低热阻特性而变得更加乐观和安全。

最后,温度效应的动态交叉反馈不容忽视。从静态特性提取中可见,当器件结温攀升至 175∘C 的极端工况时,VGS(th) 普遍发生负向偏移至 1.9V 。在解析模型的方程组演化中,较低的阈值电压虽然使得导通延迟 td(on) 和电压缓降区间略微提速,但它极大地蚕食了器件抵御寄生米勒噪声的安全裕度(Noise Margin) 。与此同时,高温下晶格散射加剧导致载流子迁移率断崖式下降,使得标称导通电阻 RDS(on) 产生显著的正温度漂移恶化 。这种正负温度系数交织的动态物理表现,进一步凸显了在构建宏观开关系统级数学模型时,绝不能剥离温度参量进行孤立分析,而必须引入热-电全耦合(Electro-Thermal Coupling)方程机制 。

热-电耦合效应与解析模型在数字孪生预测中的前沿应用

随着智能电网与车规级功率硬件迈向高可靠性、长寿命的深水区,单纯依靠离线的器件选型已无法满足对系统极限生存能力的考量。将前述建立在高度非线性电容积分基础上的开关损耗解析模型,进一步通过软件代码化(例如使用 MATLAB 脚本或嵌入至 PLECS 等系统级仿真器中),可以构建一个无需额外硬件探头的热物理量“数字虚拟传感器”(Virtual Junction Temperature Sensor) 。

在这种先进的数字孪生(Digital Twin)架构下,控制器实时捕获变换器母线侧的宏观电气信号——诸如直流母线电压 VDC 和输出相电流 IL 。随后,内置的解析算法引擎会以微秒级的执行周期,即时调用非线性电容拟合函数与温度-电阻函数,分步计算出每一次高频开关动作中由于 tri、tfu 等阶段带来的微焦耳(μJ)级别损耗脉冲 Eon 和 Eoff 。这些损耗能量被转换成发热功率源输入到基于福斯特(Foster)或考尔(Cauer)多阶热阻抗网络建立的热力学传导模型中 。最终,系统无需触碰危险的高压裸露端子,即可实时追踪被硅胶完全密封的功率半导体内部核心结温 Tj 极其快速的波动轨迹 。

这种预测机制深刻影响了电力电子系统的健康管理(Prognostics and Health Management, PHM)。当虚拟解析模型预测到由于长期循环导致器件焊层降级(表现为 Rth 异常增大),或者因过载突发电流导致结温即将冲破 175∘C 安全极限时,主动网侧控制器可实时干预发波逻辑——如动态降低开关频率、增加死区时间,或者启动降额保护算法 。由于本解析模型仅依赖于数据手册提取参数,抛弃了复杂的偏微分矩阵和收敛性噩梦,它成为了真正能在边缘计算 FPGA 节点中实时奔跑的“轻量级大脑” 。

结语与发展前瞻

本文围绕具备极致物理优势的碳化硅(SiC)MOSFET,对其在现代高频电力电子变换系统中的瞬态开关行为进行了深度物理剖析与全解析数学建模。传统基于恒定静态电容的线性化评估方法,因完全忽视了随高电压偏置剧烈崩塌的半导体空间电荷区电容,已在动辄数百伏特/纳秒(V/ns)的高速领域彻底失效。

为了弥合理论预估与实际损耗热应力之间的鸿沟,本模型深刻挖掘了 Ciss、Coss 与米勒核心 Crss 的动态演变规律。通过引入连续可导的非线性幂律参数拟合,并在微观时间轴上对导通延迟、电流飙升、电压跌落等全阶段进行微分方程的时空积分,彻底还原了米勒平台下动态电荷抽取的真实时间尺度。不仅如此,本解析体系清晰界定了数据手册中“时间等效输出电容 Co(tr)”与“能量等效输出电容 Co(er)”在物理学上的绝对分水岭,杜绝了硬开关损耗与软开关死区时间计算中的概念滥用。同时,模型严正阐明了带开尔文独立源极的四引脚(TO-247-4)先进封装,是如何在物理层面上斩断 di/dt 带来的共源极电感破坏性负反馈,进而极大加速电流响应并削减开关交叉热耗散的。

基本半导体(BASiC Semiconductor)一系列工业与车规级量产器件参数矩阵被作为实证标本无缝嵌入至模型逻辑体系中。其全系产品表现出的惊人微小本征米勒电容比与创新的银烧结极限热阻工艺,从硬件实体验证了解析模型所倡导的低串扰与强电流耦合理论。可以预见,随着 SiC 器件晶圆级良率工艺的持续演进及成本结构的平民化突破,这种兼具极高预测精度与轻量化运算负担的非线性开关损耗解析模型,必将成为下一代人工智能驱动的变换器自动化热设计、全寿命周期可靠性评估以及自适应边缘控制策略中的核心基石与灯塔。

审核编辑 黄宇

-

开关损耗

+关注

关注

1文章

76浏览量

13922 -

SiC MOSFET

+关注

关注

1文章

170浏览量

6812

发布评论请先 登录

在哪里可以找到MOSFET功率损耗信息?

onsemi NVTFS4C10N 功率MOSFET的特性与应用解析

NTD4809N与NVD4809N MOSFET:特性、参数与应用解析

深入解析 onsemi NVTFWS005N08XL MOSFET:特性、参数与应用

13.56MHz 射频电源拓扑与 1200V SiC MOSFET 集成:非线性电容补偿

碳化硅 (SiC) MOSFET 双脉冲实验 (DPT) 数据处理与开关损耗精准提取

三菱电机SiC MOSFET在工业电源中的应用

高功率密度碳化硅MOSFET软开关三相逆变器损耗分析

如何平衡IGBT模块的开关损耗和导通损耗

基本半导体碳化硅(SiC)MOSFET低关断损耗(Eoff)特性的应用优势

基于非线性电容特性的 SiC MOSFET 开关损耗解析模型建立

基于非线性电容特性的 SiC MOSFET 开关损耗解析模型建立

评论