做过 PCIe Gen6/7 或 DDR5 Signoff 的工程师,大多遇到过同一个困境:没有一个所有人都认可的标准流程。有的团队遵循 JEDEC 规范,有的依靠长期工程经验给出裕量估算,整体而言仍处于"各凭经验"的阶段。

这不是工具厂商实现得不够好,也不是 EDA 行业还不够努力——根源在于当前主流方法论本身存在算法层面的先天局限,而这一问题正随着新一代高速接口的演进被持续放大。

在 IIC Shanghai 2026,巨霖科技技术支持总监董佳龙以《高速接口 SI Signoff 仿真对 SPICE 的挑战》为题发表主题演讲,从 EDA 工具提供者与 SPICE 算法的视角,系统拆解了这一困局的根源,并分享了方向性思考。

背景:SPICE的三次演进与统计域的崛起

SPICE 的发展史,是一部用效率换取工程可行性的历史,大致以 20 年为一个分界线,经历了三次关键跃迁。

1970 年代,UC Berkeley 推出开源 SPICE,以基尔霍夫定律与牛顿-拉夫逊迭代法精确求解每个电路节点的电流与电压状态,精度极高,很快成为 IC 设计不可或缺的基础工具。到了 1990 年代,随着电路规模扩张至数十万乃至数百万晶体管级别,True-SPICE 所需的仿真时间从数天延伸至数月,工程上已无法接受——FastSPICE 应运而生,通过局部近似换取数量级的速度提升,以可接受的精度损失解决了规模瓶颈。

进入 2010 年代,速率迈入 Gbps 级别,误码率(BER)成为 Signoff 的核心指标,要求验证至 1e-12 乃至 1e-16 的极低错误概率。这意味着理论上需要仿真 10¹⁷ 量级的比特数,即便 FastSPICE 也需数百年——全瞬态方法在此彻底失效。于是,统计域算法(Statistical Eye)作为 SPICE 的自然延伸被引入:以 SPICE 仿真得到的阶跃响应为"原料",在统计域直接计算眼图概率分布与裕量,配合 IBIS 行为级模型,从根本上绕开了 BER 仿真的时间瓶颈。

这三种形态并非谁淘汰谁的关系,而是各有其不可替代的生态位:True-SPICE 是精度基准,FastSPICE 是规模仿真的工程选择,Statistical Eye 是 BER 验证的效率解法。他们之间是共存,而非迭代替代。

困局:现有方法论的结构性裂缝

理解了 SPICE 的演进逻辑,就能理解今天 SI Signoff 面临的困境从何而来。

目前 Signoff 的 SI 仿真大致分为两条路:带 Jitter 仿真与不带 Jitter 仿真。不带 Jitter 的方案依赖 Vendor 预先提供 Jitter 指标,工程师据此对裕量进行修正,要求仿真后达到相应的眼高眼宽即可。这种方式的问题在于,Vendor 给出的 Jitter 值可信度难以独立验证——SoC 往往需要搭配多种 DRAM,不同组合的行为不可能完全一致;加之 Vendor 倾向于给出偏保守的估算以规避责任,实际上会吃掉更大的设计裕量。

带 Jitter 仿真则面临另一个难题:如何对 Jitter 本身建模。通道对 Jitter 存在放大效应,而随机抖动(RJ)的统计特性需要大量比特才能体现——仿真比特数少了,结果失真;比特数多了,仿真时间又不可接受。这一矛盾至今没有令人满意的解法。

统计域算法(Channel Simulation)本身也有其固有局限。整套算法建立在线性叠加的数学假设之上,而真实电路中的串扰、电源噪声等干扰本质上是非线性的,无法被安全地线性化。MER 等后续算法对此有所改善,但精度缺陷根植于算法底层,无法从根本上消除。这一问题并非 EDA 工具厂商实现水平的问题,而是算法框架本身的先天约束。

至于 Bit-by-Bit 仿真,最大的挑战在于外插精度:仿真比特数有限时,必须通过数学模型外插到目标 BER。目前业界普遍采用双 Dirac 模型,但这一假设是否普适,始终存疑。

综合来看,Channel Simulation 速度可用、功能覆盖全,但精度存在算法层面的先天缺陷;Full Transient 精度无可挑剔,但效率与功能灵活性均不满足工程需求——两条路各有软肋,而 Signoff 恰恰需要两者兼顾。正因如此,DDR5 等高速接口至今没有形成业界公认的统一 Signoff 标准,大型厂商凭经验积累自定一套,中小团队则往往不得不在精度与可行性之间做出妥协。

研究基础:从True-SPICE到系统级SI仿真

在讨论上述问题之前,有必要说明巨霖科技在 SPICE 各层级所做的研究与工程实践——这是后续探讨得以成立的前提。

PanosSPICE 是巨霖科技自研的 True-SPICE 仿真引擎,集成了 BSIM3/4、PSP、BSIMCMG、VBIC 等主流器件模型,并与东南大学联合开发了 GaN 与 SiC 第三代半导体 Level 90/91 物理器件模型,填补了新兴功率器件仿真领域的模型空白。在仿真精度方面,PanosSPICE 已通过多家头部客户的独立验证,被认定为模拟/混合信号 IC 设计与 IP 验证场景下达到 Golden 标准的 Signoff 级仿真工具。

SIDesigner 是巨霖在系统级 SI/PI 仿真方向的工程实践成果——一站式 SI/PI 仿真平台,覆盖业界主流 SI/PI 仿真工具的所有核心场景,瞬态仿真与 Statistical Eye 精度均达到 Golden 级别。平台亦涵盖与客户联合开发的若干工程增值功能:DFQ(基于 DOE+RSM+ANOVA 的多变量设计空间优化)、BERC(融合时域与通道仿真的 BER Contour 预测,覆盖 DDR4/5、GDDRx、UCIe 等主流高速并行接口)以及 RS-Code 仿真(评估 RSFEC 在实际通道中的纠错效果)。

这说明一个事实:从 True-SPICE 引擎到统计域算法,再到系统级 SI/PI 全链路仿真,巨霖科技在 SPICE 各个算法层级均有持续的研究投入与工程验证积累。正是基于这一基础,对于当前高速接口 Signoff 所面临的挑战,我们认为有条件做进一步的研究与探索。

答案会不会在另一个方向?

带着上述认知,我们一直在想一个问题:

FastSPICE 是在 True-SPICE 精度与 Statistical Eye 速度之间做了折中,但它本质上仍更偏向 True-SPICE——毕竟是晶体管级的瞬态仿真。那么,有没有可能存在一种"反向的折中"——同样是两者之间的权衡,但这次偏向统计域一侧?

如果说 Channel Simulation 的根本问题在于线性假设带来的精度天花板,那一个可能的思路是:重新把目光转回瞬态仿真,但以不同的方式使用它。

不是跑全量 BER 比特、不追求极致的精度,而是仿真一批具有代表性的 worst-case pattern——这些 pattern 足够长、足够典型,能够反映系统的非线性行为与最差场景;在这个过程中,如果能灵活引入均衡算法甚至 AMI 仿真,就能突破传统 SPICE 流程在功能灵活性上的限制;最后再对这批结果做统计分析,估算 BER 与眼图裕量。

这样的流程,速度上不会像传统 Channel Simulation 那么快,但也许能在几个小时内出结果;精度上不会像 Full Transient 那么完整,但有望在真正的晶体管级仿真基础上,给出比纯统计域方法更可靠的数字。

这只是一个方向性的思考,问题本身远比答案多。能不能做到、做到哪个程度,有待更多的验证。但我们认为,这个方向值得认真探索。

结语

随着 DDR5、HBM、UCIe 等高速接口标准持续演进,以及 AI 芯片对系统级仿真精度要求的不断提升,Signoff 流程的精度门槛只会越来越高,而精度与效率之间的结构性矛盾也将愈发凸显。如何在工程可行的时间窗口内完成真正可信赖的仿真验证,是整个行业必须正视的挑战。

面向未来,巨霖科技将始终秉持"精准仿真,赋能未来"的使命,持续深耕"电路"与"电磁"仿真技术,紧密围绕产业前沿需求,与战略客户及产业链伙伴持续深入合作,不断打造和推出新的业界标杆产品。

-

仿真

+关注

关注

55文章

4532浏览量

138647 -

eda

+关注

关注

72文章

3140浏览量

183665 -

高速接口

+关注

关注

1文章

79浏览量

15340

原文标题:IIC Shanghai | 高速接口 SI Signoff:统计域算法的精度局限与路径重构

文章出处:【微信号:巨霖,微信公众号:巨霖】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

巨霖科技荣膺2026中国IC设计成就奖之年度技术突破EDA公司

巨霖科技PanosSPICE仿真平台的核心技术亮点

浅谈复杂芯片设计中的SPICE仿真困境

巨霖科技首届SI/PI高阶技术研讨会成功举办

巨霖科技荣获2025上海最具投资潜力50佳创业企业

巨霖科技分享国产SI仿真工具的破局之道

巨霖科技ICCAD-Expo 2025圆满收官

巨霖科技荣获2025湾芯奖技术创新奖

巨霖科技荣获安永复旦2025最具潜力企业奖

巨霖科技乔迁仪式隆重举行

基于巨霖SIDesigner实现PCIe仿真的步骤

松霖科技PLM项目正式启动

高速多层板SI/PI分析的关键要点是什么

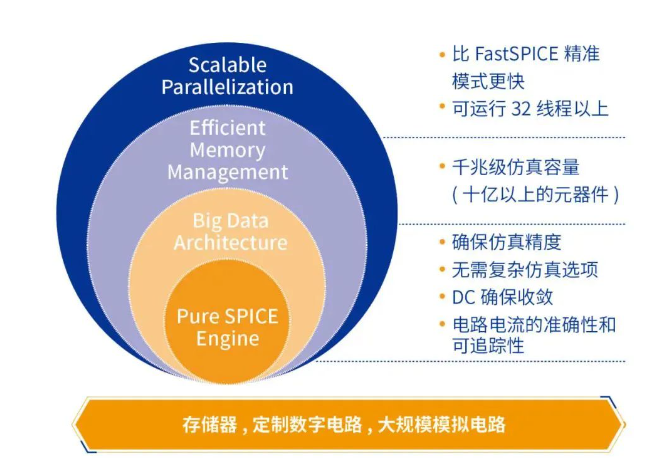

概伦电子电路类型驱动SPICE仿真器NanoSpice X介绍

概伦电子千兆级高精度电路仿真器NanoSpice Giga介绍

巨霖科技畅谈高速接口SI Signoff仿真对SPICE的挑战

巨霖科技畅谈高速接口SI Signoff仿真对SPICE的挑战

评论