探索MAX9315:高性能时钟与数据驱动的理想之选

在电子设计领域,时钟和数据的精确分配至关重要,它直接影响着整个系统的性能和稳定性。今天,我们就来深入了解一款专为时钟和数据分配而设计的低偏斜1至5差分驱动器——MAX9315。

文件下载:MAX9315.pdf

一、基本概述

MAX9315允许在两个输入之间进行选择,所选输入会在五个差分输出端重现。其差分输入可通过将片上VBB电源连接到一个输入作为参考电压,来适应单端输入。该器件具有低输出到输出偏斜(20ps)的特点,非常适合跨背板或电路板的时钟和数据分配。它采用节省空间的20引脚TSSOP封装,为设计带来了更多的灵活性。

二、功能特性

电源灵活性

- 对于差分HSTL/LVPECL操作,电源范围为+2.375V至+3.8V;对于差分LVECL操作,电源范围为 -2.375V至 -3.8V。这种灵活的电源范围使得MAX9315能够适应不同的系统供电需求,无论是标称 +2.5V 还是 +3.3V 供电的系统,都能实现高性能的时钟或数据分配。

输入选择与同步控制

- 具备两个可选的差分输入,可通过单端SEL输入选择两个差分时钟输入CLK0或CLK1其中之一。同时,它还支持同步输出使能/禁用功能,通过EN引脚进行控制。这使得设计者能够根据实际需求灵活地控制输出信号,确保系统的稳定性和可靠性。

低偏斜与高频率性能

- 输出到输出偏斜低至20ps,传播延迟为360ps,并且能在1.5GHz频率下保证400mV的差分输出。这些特性使得MAX9315在高速时钟和数据分配应用中表现出色,能够有效减少信号失真和延迟。

单端输入支持

- 片上参考电压VBB可用于单端输入,当输入悬空时会被偏置为低电平。在使用单端输入时,通过将VBB连接到差分输入的反相或同相端作为参考,就能将差分时钟输入配置为接受单端输入,为设计提供了更多的选择。

三、电气特性

直流特性

| 参数 | 符号 | 条件 | -40°C | +25°C | +85°C | 单位 | ||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| MIN | TYP | MAX | MIN | TYP | MAX | MIN | TYP | MAX | ||||

| 单端输入高电压 | VIH | VCC - 1.225 | VCC | VCC - 1.225 | VCC | VCC - 1.225 | VCC | V | ||||

| 单端输入低电压 | VIL | VEE | VCC - 1.625 | VEE | VCC - 1.625 | VEE | VCC - 1.625 | V | ||||

| 输入电流 | IIN | VIH(MAX), VIL(MIN) | -500 | 500 | -500 | 500 | -500 | 500 | µA |

交流特性

| 参数 | 符号 | 条件 | -40°C | +25°C | +85°C | 单位 | ||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| MIN | TYP | MAX | MIN | TYP | MAX | MIN | TYP | MAX | ||||

| 差分输入 - 输出延迟 | tPLHD, tPHLD | Figure 2 | 290 | 400 | 310 | 440 | 300 | 520 | ps | |||

| 输出到输出偏斜 | tSKOO | Note 8 | 5 | 30 | 20 | 40 | 20 | 50 | ps | |||

| 部分到部分偏斜 | tSKPP | Note 9 | 110 | 130 | 220 | ps |

从这些电气特性中我们可以看出,MAX9315在不同温度条件下都能保持较为稳定的性能,这为其在各种复杂环境中的应用提供了有力保障。

四、典型应用

精密时钟分配

由于其低偏斜和高频率性能,MAX9315非常适合用于精密时钟分配系统,能够确保时钟信号在传输过程中的准确性和稳定性。

低抖动数据中继器

在数据传输系统中,低抖动是非常关键的性能指标。MAX9315的低偏斜和高差分输出特性使得它能够作为低抖动数据中继器,有效减少数据传输过程中的抖动和失真。

数据和时钟驱动与缓冲

在中央局背板时钟分配、DSLAM背板、基站和ATE等应用中,MAX9315可以作为数据和时钟驱动与缓冲器,为系统提供稳定可靠的时钟和数据信号。

五、设计要点

电源旁路

为了减少电源噪声对器件性能的影响,需要将VCC到VEE用高频表面贴装陶瓷0.1µF和0.01µF电容器并联旁路,并且尽量靠近器件放置,其中0.01µF电容器要最靠近器件。当使用VBB参考输出时,也需要用0.01µF陶瓷电容器将其旁路到VCC。

受控阻抗走线

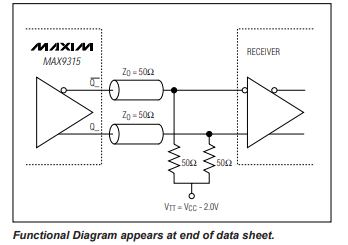

输入和输出走线的特性会影响MAX9315的性能,因此需要使用50Ω特性阻抗的走线来连接高频输入和输出信号,同时尽量减少过孔的数量,以防止阻抗不连续。在电缆和连接器中也要保持50Ω特性阻抗,以减少反射。

输出端接

输出端需要用50Ω电阻连接到VCC - 2V进行端接,也可以使用等效的戴维南端接。当从差分输出中获取单端信号时,需要对两个输出端都进行端接。

六、总结

MAX9315凭借其低偏斜、高频率性能、灵活的电源范围和丰富的功能特性,成为了时钟和数据分配应用中的理想选择。在实际设计中,我们需要根据其电气特性和设计要点进行合理的布局和布线,以充分发挥其性能优势。大家在使用MAX9315的过程中,有没有遇到过什么特别的问题或者有什么独特的设计经验呢?欢迎在评论区分享交流。

发布评论请先 登录

探索RENESAS ICS95V847:高性能时钟驱动芯片的卓越之选

探索 MAX4361/MAX4362/MAX4363:高性能 ADSL 驱动与接收的理想之选

探索MAX3386E:高性能RS - 232收发器的卓越之选

MAX9315 1:5差分LVPECL/LVECL/HSTL时钟和数据驱动器技术手册

探索MAX9315:高性能时钟与数据驱动的理想之选

探索MAX9315:高性能时钟与数据驱动的理想之选

评论