ADSP - 21992:高性能混合信号 DSP 控制器的深度剖析

在电子工程领域,高性能的 DSP 控制器一直是推动各种应用发展的核心力量。今天,我们就来深入探讨一款功能强大的混合信号 DSP 控制器——ADSP - 21992,看看它在工业控制、信号处理等领域能为我们带来怎样的惊喜。

文件下载:ADSP-21992.pdf

一、ADSP - 21992 概述

ADSP - 21992 是一款基于 ADSP - 2199x DSP 核心的混合信号 DSP 控制器,适用于各种高性能工业电机控制和信号处理应用。它将高性能 DSP 与嵌入式控制外设的混合信号集成相结合,目标应用涵盖工业电机驱动、不间断电源、光网络控制、数据采集系统、测试与测量系统以及便携式仪器等。

二、核心架构与性能

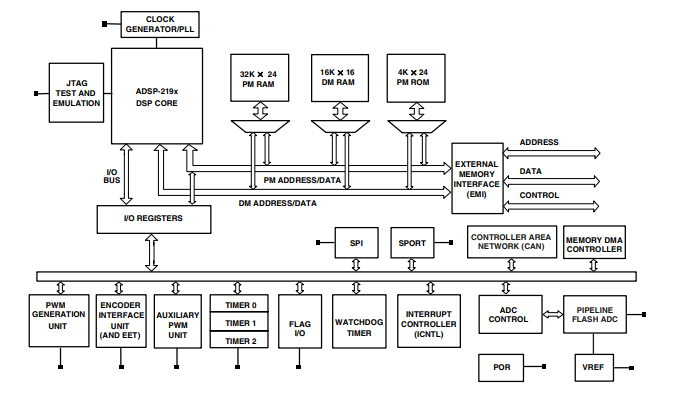

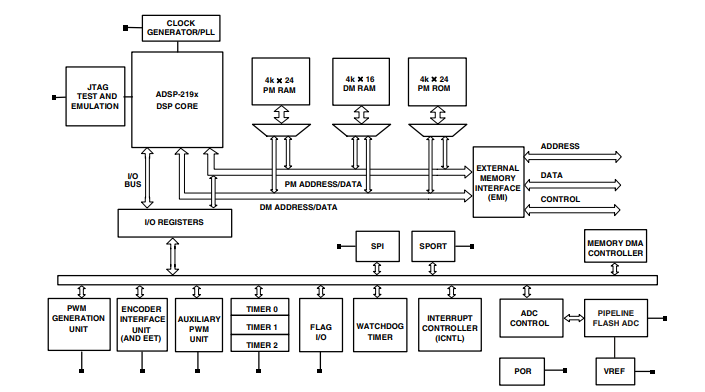

(一)DSP 核心架构

- 指令周期与性能:该控制器拥有出色的指令周期时间,内部指令周期时间可达 6.25 ns,能实现高达 160 MIPS 的持续性能。不同的时钟频率对应不同的指令周期时间,如 150 MIPS 持续性能时为 6.67 ns,100 MIPS 持续性能时为 10.0 ns。

- 代码兼容性:与 ADSP - 218x 家族代码兼容,采用易于使用的代数语法,方便工程师进行开发。

- 指令执行与内存空间:单周期指令执行,拥有高达 1M 字的可寻址内存空间,地址宽度为 24 位。其双用途程序内存可同时用于指令和数据存储,全透明指令缓存允许每个指令周期进行双操作数提取。

- 计算单元与并行执行:具备独立的 ALU、乘法器/累加器和桶形移位器计算单元,带有双 40 位累加器。支持单周期上下文切换,能够并行执行计算和内存指令,流水线架构可在高达 160 MIPS 的速度下高效执行代码。

(二)时钟与指令集

- 时钟生成:时钟生成模块包含时钟控制逻辑,用户可选择和更改主时钟频率。该模块生成两个输出时钟,即 DSP 核心时钟 CCLK 和外设时钟 HCLK。CCLK 最高可达 160 MHz,HCLK 可等于 CCLK 或 CCLK/2,最高可达 80 MHz。

- 指令集特点:指令集提供灵活的数据移动和多功能指令,每个单字指令可在单个处理器周期内执行。汇编语言采用代数语法,便于编码和阅读,同时有一套完整的开发工具支持程序开发。

三、内存架构

(一)内部内存

ADSP - 21992 提供 48K 字的片上 SRAM 内存,分为三个块:两个 16K × 24 位块(块 0 和块 1)和一个 16K × 16 位块(块 2),此外还有一个 4K × 24 位的程序内存引导 ROM。其统一的程序和数据内存空间由 16M 个位置组成,可通过两个 24 位地址总线(PMA 和 DMA 总线)访问。

(二)外部内存

该控制器支持多种外部内存空间,包括外部内存空间(MS3 - 0 引脚)、I/O 内存空间(IOMS 引脚)和引导内存空间(BMS 引脚)。每个外部内存空间都有单独的控制寄存器,可配置独特的访问参数。

四、外设架构

(一)通信接口

- SPI 端口:基于 SPI 标准,提供通用可配置的串行端口接口功能,支持主或从操作,数据速率可达 HCLK/4,具备 DMA 能力和专用中断。

- SPORT 端口:集成完整的同步串行端口,支持双向通信、双缓冲、多种时钟模式、可变字长、硬件压缩扩展、直接内存访问等功能,还具备多通道能力和 UART 软件仿真功能。

- CAN 模块:符合 CAN V2.0B 标准,支持标准(11 位)和扩展(29 位)标识符,数据速率可达 1 Mbps 及以上,拥有 16 个可配置邮箱和数据过滤功能。

(二)模拟与数字转换

- ADC 系统:包含一个快速、高精度、多输入的模数转换系统,具有 8 个专用模拟输入和双通道同时采样能力。最高采样率可达 20 MSPS,输入电压范围为 2.0 V 峰 - 峰,支持内部或外部电压参考。

- 电压参考:片上集成带隙参考,可提供精确的 1.0 V 输出,也可配置为使用外部参考。

(三)PWM 与编码器接口

- PWM 生成单元:3 相 16 位中心 PWM 生成单元,可编程脉冲宽度,分辨率可达 12.5 ns,支持单/双更新模式、可编程死区时间和开关频率等。

- 辅助 PWM 生成单元:2 通道 16 位辅助 PWM 输出单元,可编程频率和占空比,支持独立或偏移操作模式。

- 编码器接口单元:强大的编码器接口块,支持高达 53 MHz 的正交速率,具备可编程滤波、32 位编码器计数器等功能。

(四)其他外设

还包含 16 个通用标志 I/O 引脚、3 个可编程 32 位间隔定时器、看门狗定时器、中断控制器和集成的上电复位(POR)电路等。

五、低功耗操作

ADSP - 21992 具有四种低功耗选项,包括空闲模式、掉电核心模式、掉电核心/外设模式和掉电所有模式。通过执行 IDLE 指令并配置 PLLCTL 寄存器中的相关位,可选择不同的低功耗模式,以显著降低设备在待机条件下的功耗。

六、开发与设计要点

(一)开发工具

该控制器得到了一套完整的 CROSSCORE™ 软件和硬件开发工具的支持,包括 Analog Devices 仿真器和 VisualDSP++™ 开发环境。这些工具提供了从编程到调试的全方位支持,有助于提高开发效率。

(二)设计兼容板

在设计与仿真器兼容的 DSP 板时,需要注意目标板应包含连接 DSP JTAG 端口到仿真器的接口。具体的设计问题可参考 Analog Devices 网站上的 EE - 68: JTAG Emulation Technical Reference。

七、总结

ADSP - 21992 以其强大的核心架构、丰富的外设功能和灵活的低功耗操作模式,为工业电机控制和信号处理等领域提供了一个高性能、高集成度的解决方案。作为电子工程师,我们在使用这款控制器时,要充分了解其特性和参数,合理利用其功能,以实现更高效、更稳定的系统设计。大家在实际应用中遇到过哪些关于 ADSP - 21992 的问题呢?欢迎在评论区交流分享。

-

工业控制

+关注

关注

38文章

1695浏览量

92230

发布评论请先 登录

16位数字信号控制器DSP56857:技术剖析与设计指南

DSP56853:16位数字信号控制器的技术剖析与设计指南

dsPIC30F6010:高性能16位数字信号控制器的技术剖析

ADSP-CM40xF系列混合信号控制处理器:高性能与多功能的完美融合

ADSP - BF531/ADSP - BF532/ADSP - BF533:高性能嵌入式处理器的深度剖析

ADSP-21560/21561/21564/21568:高性能SHARC+单核心DSP的深度剖析

深入剖析ADSP - 2189M:高性能数字信号处理的理想选择

ADSP - 2185M数字信号处理器深度剖析:特性、架构与应用指南

深度剖析LTC3788:高性能2相双同步升压控制器

LTC3784:高性能多相同步升压控制器的深度剖析

MSP430x43x/44x系列混合信号微控制器深度剖析

ADSP-21992高性能混合型信号DSP,160MHz,32K字程序存储器RAM,16K字数据存储器RAM技术手册

ADSP - 21992:高性能混合信号 DSP 控制器的深度剖析

ADSP - 21992:高性能混合信号 DSP 控制器的深度剖析

评论