深入解析LM5067:负热插拔/浪涌电流控制器的技术奥秘

在电子设备的设计中,热插拔功能和浪涌电流控制至关重要,它能确保设备在带电系统中安全、稳定地运行。德州仪器(TI)的LM5067负热插拔/浪涌电流控制器,凭借其丰富的特性和广泛的应用场景,成为众多工程师的首选。今天,我们就来深入探讨一下LM5067的技术细节和应用设计。

文件下载:lm5067.pdf

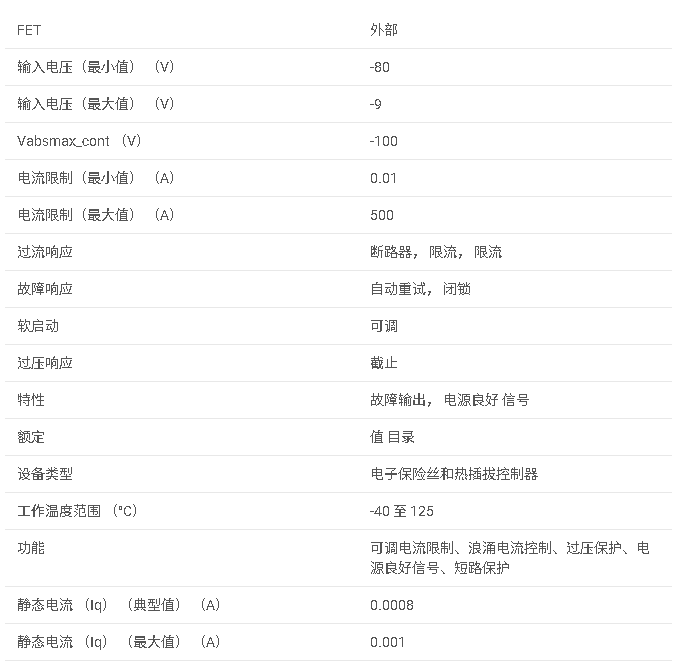

一、LM5067特性亮点

1. 宽工作范围

LM5067的工作电压范围为 -9 V至 -80 V,具备 -100 V的瞬态承受能力,能够适应多种不同的电源环境,为设计提供了更广泛的选择。

2. 浪涌电流限制

在电路卡插入带电系统背板或其他“热”电源时,LM5067能有效控制浪涌电流,减少系统电压降和瞬态干扰,保护其他电路不受影响,避免意外复位的发生。

3. 可编程功能

- 最大功耗限制:通过外部电阻可对外部串联N沟道MOSFET的最大功耗进行编程,确保其在安全工作区域(SOA)内运行。

- 电流限制:可调节电流限制阈值,满足不同应用场景的需求。

- 欠压和过压锁定:可编程的欠压锁定(UVLO)和过压锁定(OVLO)功能,以及相应的迟滞设置,能在输入电压超出正常范围时及时关闭电路,保护设备安全。

4. 故障保护功能

- 断路器功能:当检测到严重过流情况(如负载短路)时,能迅速切断串联开关器件,保护系统安全。

- 可编程故障定时器:避免误触发,提高系统的可靠性。

5. 电源良好指示

有源高电平开漏POWER GOOD输出,可指示输出电压是否接近输入电压,方便用户实时了解系统状态。

6. 多种工作模式

提供锁存故障和自动重启两种版本,满足不同应用场景的需求。

二、应用场景广泛

LM5067的应用场景十分广泛,包括但不限于以下几个方面:

- 服务器背板系统:确保服务器在带电背板上的安全插拔,减少对系统的影响。

- 浪涌电流限制:有效控制设备启动时的浪涌电流,保护电源和其他设备。

- 固态断路器:实现快速切断电路,保护系统免受短路等故障的影响。

- 瞬态电压保护器:对瞬态电压进行保护,提高系统的稳定性。

- 固态继电器:可作为固态继电器使用,实现远程开关控制。

- 欠压锁定和电源良好检测:实时监测输入电压和输出状态,确保系统在正常电压范围内工作。

三、功能原理剖析

1. 上电序列

系统电压从0开始上升时,外部N沟道MOSFET(Q1)被GATE引脚的110 mA下拉电流保持关断。当LM5067的工作电压(VCC – VEE)达到 (POR{IT}) 阈值(7.7V)时,插入定时器启动,此时TIMER引脚的电容 (C{T}) 由6 µA电流源充电,Q1仍被2.2 mA下拉电流保持关断,以允许系统电压的振荡和瞬态稳定。插入时间结束后,当工作电压达到 (POR_{EN}) 阈值(8.4 V)时,LM5067控制电路启用。当系统电压超过UVLO阈值(UVLO引脚 > 2.5V 高于VEE)时,GATE引脚输出52 µA电流开启Q1,同时监测Q1的漏极电流和功耗,进行浪涌电流限制和功率限制。

2. 栅极控制

在正常工作时,GATE引脚输出52 µA电流使Q1导通,Q1的栅源电压被限制在约13V。在系统电压初始施加时,GATE引脚被110 mA下拉电流拉低,防止MOSFET因漏栅电容充电而误开启。在插入时间内,GATE引脚被2.2 mA下拉电流拉低,确保Q1处于关断状态。当系统输入电压低于UVLO阈值或高于OVLO阈值时,GATE引脚被2.2 mA下拉电流拉低,关闭Q1。

3. 电流限制

当检测电阻 (R{S}) 两端的电压达到50 mV时,电流限制阈值被触发,GATE电压被控制以限制MOSFET Q1的电流。在电流限制期间,故障定时器启动。如果负载电流在故障超时周期结束前降至电流限制阈值以下,LM5067恢复正常工作。为确保正常工作, (R{S}) 电阻值应不大于100 mΩ。

4. 断路器功能

当负载电流迅速增加(如负载短路),检测电阻 (R{S}) 中的电流超过电流限制阈值的约两倍(100 mV/ (R{S}) )时,GATE引脚的110 mA下拉电流迅速拉低Q1的栅极,启动故障超时周期。当 (R_{S}) 两端的电压降至100 mV以下时,110 mA下拉电流关闭,Q1的栅极电压由电流限制或功率限制功能决定。

5. 功率限制

LM5067通过监测Q1的漏源电压(OUT至SENSE)和漏极电流,计算Q1的功耗。当功耗达到由PWR引脚电阻编程的功率限制阈值时,GATE电压被调制以降低Q1的电流,同时故障定时器启动。功率限制功能可确保MOSFET Q1的最大功耗在其SOA额定范围内。

6. 故障定时器和重启

当电流限制或功率限制阈值被触发时,85 µA的故障定时器电流源对 (C{T}) 充电。如果故障在TIMER引脚电压达到4.0V之前消除,LM5067恢复正常工作, (C{T}) 被2.5 µA电流源放电。如果TIMER引脚电压达到4.0V,Q1被2.2 mA下拉电流关闭。LM5067-1在故障超时周期结束后锁定GATE引脚低电平,需要外部重新启动;LM5067-2则在故障超时周期后自动进行重启序列,TIMER引脚在4 V和1.25 V之间循环七次,最后在第八次降至0.3 V时开启Q1。

7. 欠压锁定(UVLO)和过压锁定(OVLO)

通过外部电阻分压器设置UVLO和OVLO阈值,当输入电源电压低于UVLO阈值或高于OVLO阈值时,Q1被关闭,同时提供迟滞功能,提高系统的稳定性。

8. 电源良好引脚(PGD)

PGD引脚连接到内部N沟道MOSFET的漏极,需要外部上拉电阻。当外部MOSFET的 (V{DS}) 降至1.23 V以下时,PGD引脚输出高电平;当 (V{DS}) 超过2.5 V、系统输入电压低于UVLO阈值或高于OVLO阈值、或检测到故障时,PGD引脚输出低电平。

四、应用设计要点

1. 设计要求

- 确定系统电压范围:选择合适的输入电阻 (R{IN}) ,确保在最小系统电压下为VCC引脚提供至少2 mA电流,并根据最大系统电压计算 (R{IN}) 的功率额定值。

- 确定电流限制阈值:根据正常最大负载电流和电流检测电阻的公差,确定电流限制阈值 (I{LIM}) ,并计算 (R{S}) 的值。

- 确定功率限制阈值:根据MOSFET的SOA信息,确定最大允许功率耗散 (P{FET(LIM)}) ,并计算 (R{PWR}) 的值。

- 确定定时器电容 (C_{T}) 的值:根据插入时间延迟、故障超时周期和重启时间的要求,计算 (C_{T}) 的值。

- 设置UVLO和OVLO阈值:根据应用需求,选择合适的方法设置UVLO和OVLO阈值及迟滞。

- 选择合适的电源良好输出电压和上拉电阻:确保PGD引脚能准确指示系统状态。

2. 详细设计步骤

(R{IN}) 和 (C{IN}) 的选择

LM5067的工作电压由内部13 V并联稳压器确定, (R_{IN}) 需确保在最小系统电压下为LM5067提供至少2 mA电流,并根据最大系统电压计算其功率额定值。

电流限制 (R_{S}) 的计算

根据所需的电流限制阈值 (I{LIM}) ,计算 (R{S}) 的值: (R{S}=frac{50 mV}{I{LIM}}) 。同时,要考虑 (R_{S}) 的功率额定值和浪涌能力,采用Kelvin连接技术确保准确测量电流。

功率限制阈值的设置

根据所需的功率限制阈值 (P{FET(LIM)}) 和 (R{S}) 的值,计算 (R{PWR}) 的值: (R{PWR}=1.42 × 10^{5} × R{S} × P{FET(LIM)}) 。为确保功率限制功能正常工作, (R_{PWR}) 应不大于150 kΩ。

开启时间的计算

开启时间取决于LM5067在开启过程中是仅工作在电流限制模式还是同时工作在功率限制和电流限制模式。不同模式下,开启时间的计算公式不同,需根据具体情况进行计算,并确保故障超时周期大于开启时间。

MOSFET的选择

选择外部MOSFET(Q1)时,应考虑其 (BV{DSS}) 额定值、最大连续电流额定值、脉冲漏极电流规格、SOA图表和热特性等因素,确保其能满足应用需求。如果Q1的最大 (V{GS}) 额定值小于13V,需添加外部齐纳二极管进行保护。

定时器电容 (C_{T}) 的确定

根据插入延迟、故障超时周期和重启时间的要求,分别计算 (C{T}) 的值。插入延迟时间 (t1) 对应的 (C{T}) 计算公式为 (C{T}=t1 × 1.5 × 10^{-6}) ;故障超时周期 (t{FAULT}) 对应的 (C{T}) 计算公式为 (C{T}=t{FAULT} × 2.13 × 10^{-5}) ;LM5067-2的重启时间 (t{RESTART}) 对应的 (C{T}) 计算公式为 (t{RESTART}=C_{T} × 9.4 × 10^{6}) 。

UVLO和OVLO的设置

可根据应用需求选择不同的方法设置UVLO和OVLO阈值及迟滞,如使用三个电阻(R1 - R3)或四个电阻(R1 - R4)的配置。在设置过程中,要确保UVLO和OVLO引脚的电压不超过其绝对最大额定值。

热考虑

为确保LM5067的结温不超过125°C,需根据环境温度、热阻和功耗进行热计算。结温计算公式为 (T{J}=T{A}+(R{theta JA} × P{D})) ,其中 (P{D}=13 V × I{CC}) 。

系统考虑

在设计中,要确保电源侧有足够的电容来吸收负载电流关断时产生的瞬态电压,避免损坏LM5067。对于感性负载,需在LM5067的输出端添加二极管,提供负载电流的回流路径。在极端反向电流浪涌事件中,可使用串联电阻和肖特基二极管保护SENSE、SENSE_K和OUT引脚。

电源良好引脚的设计

PGD引脚在初始上电时为高电平,当工作电压超过约2V时变为低电平,当Q1导通且OUT引脚电压与SENSE引脚电压之差小于1.23 V时,PGD引脚再次变为高电平。可根据需要添加延迟电路,如使用电容或电阻电容组合来实现不同的延迟效果。

五、布局设计注意事项

1. 布局准则

- 将LM5067靠近电路板的输入连接器,减少连接器到FET的走线电感。

- 将 (R{IN}) 和 (C{IN}) 靠近VCC和VEE引脚,降低瞬态电压对LM5067的影响。

- 检测电阻 (R_{S}) 应靠近LM5067,并采用Kelvin连接技术。

- 高电流路径和返回路径应尽量平行且靠近,以减少环路电感。

- 各组件的VEE连接应直接连接到LM5067的VEE引脚,再连接到系统VEE。

- 为串联开关器件(Q1)提供足够的散热措施,降低热应力。

- 电路板边缘连接器可设计为在电路板拔出时先关闭LM5067,避免电源电压突然断开。

- 如果LM5067的功耗较高,可在封装下方提供暴露的铜焊盘,并通过多个过孔连接到电路板另一侧的铜层。

2. 布局示例

文档中提供了一个建议的电路板连接器设计示例,展示了各组件的布局和连接方式,可作为实际设计的参考。

六、总结

LM5067负热插拔/浪涌电流控制器以其丰富的功能和灵活的可编程特性,为电子设备的热插拔和浪涌电流控制提供了可靠的解决方案。在设计过程中,工程师需要根据具体应用需求,合理选择组件参数,优化布局设计,确保系统的稳定性和可靠性。希望本文能对大家在使用LM5067进行设计时有所帮助。你在使用LM5067的过程中遇到过哪些问题呢?欢迎在评论区分享你的经验和见解。

-

热插拔控制器

+关注

关注

0文章

351浏览量

12091

发布评论请先 登录

LM5067,pdf datasheet (Negative

带功率限制的负热插拔/浪涌电流控制器

深入解析LM5067:负热插拔/浪涌电流控制器的技术奥秘

深入解析LM5067:负热插拔/浪涌电流控制器的技术奥秘

评论